**Q:**如何编写定时器中断驱动内核模块?

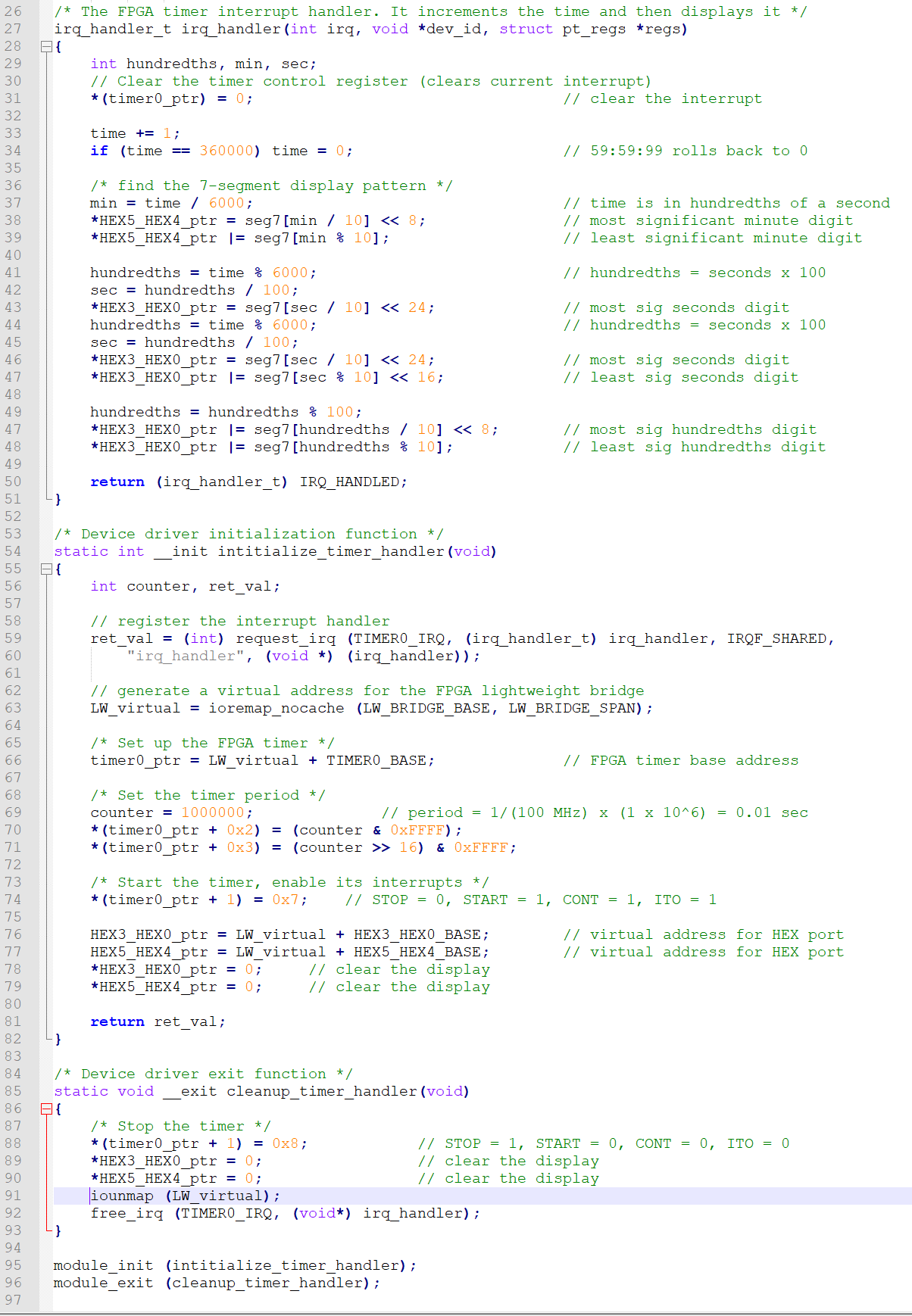

**A:**使用在FPGA中实现的间隔定时器FPGA Timer0,寄存器接口基地址为0x00002000,时钟频率100MHz,中断ID为72。调用这个定时器需要向Counter start value寄存器写入适当的值(有两个Counter start value寄存器,一个存储32位定时器值中的高16位,另一个存储低16位);通过程序将TO位写为0,即可将其值清零。如果Control寄存器中的ITO位为1,则每次设置TO位的时候,定时器将产生一个ARM中断。

本次实验编写的定时器中断驱动内核模块可实现在数码管上显示实时时钟,内核模块中使用到一个hardware timer模块,实现持续记录时间的功能,部分代码如下:

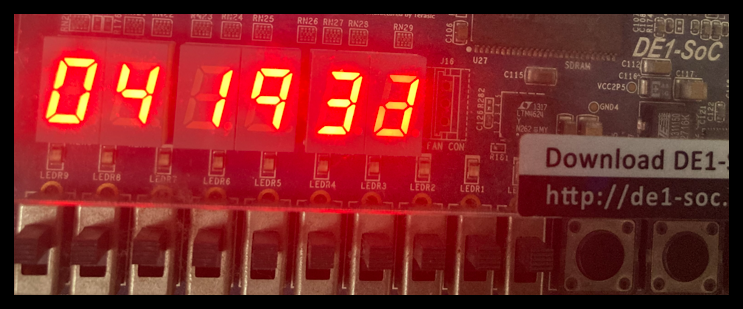

启动DE1-SoC-UP Linux系统,执行make命令编译生成模块文件然后加载模块,可观察到DE1-SoC开发板上的七段数码管HEX5~HEX0上显示实时时钟,从00:00:00开始计时,到59:59:99后重新返回00:00:00开始计时;在Terminal上使用rmmod命令移除内核模块后,exit程序会将七段数码管清零。