时域反射计 (TDR) 是一种通常用于测量印刷电路板 (PCB) 测试试样和电缆阻抗的仪器。TDR 对于测量过孔和元件焊盘的电感和电容、探针尖端电容和电感,甚至寄生电感收发器耦合电容器也非常有用。这也是验证仿真或提取您自己的模型的一种简单方法。高端专用 TDR 通常包含此功能,但即使使用简单的基于实时示波器的 TDR 也可以通过简单的光标测量来产生这些结果。

理论和模拟结果

基本的 TDR 测量是反射系数 Γ,几乎每个 TDR(包括 Picotest J2151A,使用可在 [1] 中下载的设置文件)都提供此数据轨迹。TDR 使用 Γ 和 TDR 阻抗(通常为 50Ω)的变换来确定传输线(电缆或 PCB 走线)的阻抗。

此阻抗变换也包含在上述引用的 setup 文件中。对于具有均匀Γ(或阻抗)的无损传输线,显示的 TDR 走线是一条平坦的线,几乎不需要解释。门控光标用于显示光标之间的平均阻抗值。

当传输线不均匀或连接了元件时,显示的 TDR 走线不是平坦的,这就是需要解释的地方。

反射系数 Γ 中的正"光点"表示串联电感,而反射系数 Γ 中的负"光点"表示并联电容。

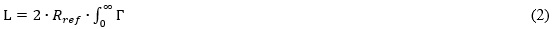

串联电感和分流电容可以从反射系数、Γ和 TDR 参考阻抗(通常为 50 Ω)获得,如下所示:

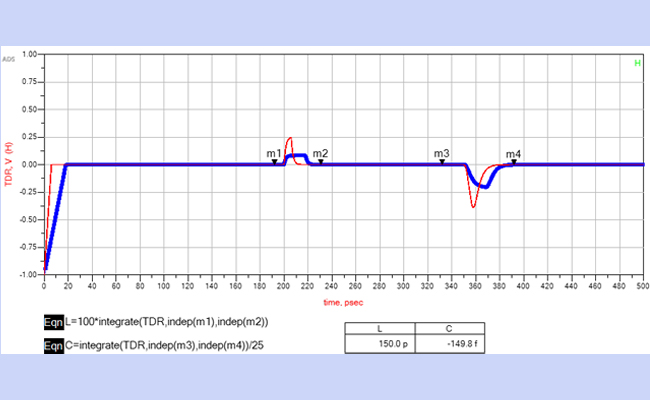

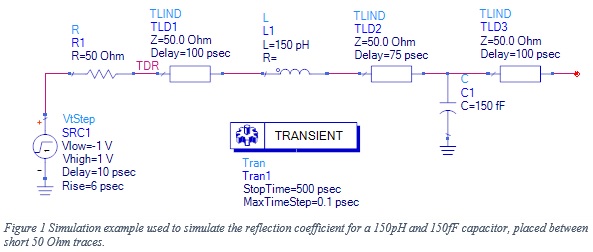

可以以简单的模拟为例。图 1 所示的示例包括串联电感和分流电容。

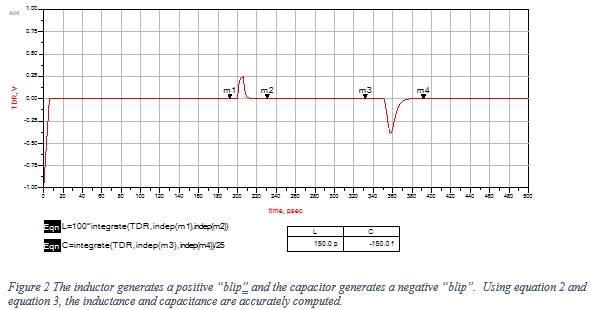

仿真结果如图 2 所示。

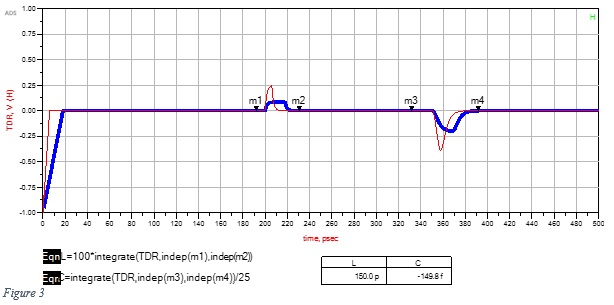

有趣的是,TDR 的带宽对结果影响很小。此仿真以 18ps 的上升时间而不是 6ps 的上升时间重复。结果如图 3 所示,提供与 6ps 相同的结果。在某些时候,传输线损耗会降低测量信噪比,结果将变得可疑。

该仿真结果中的第一个 "小插曲" 是串联电感器,它位于 100ps 无损传输线的末端。TDR 看到往返路径,因此正确显示 200ps。

分流电容位于串联电感之后 75ps,TDR 再次正确地将往返路径视为 2*(100ps+75ps) 或 350ps。

放置在每个 "blip" 之前和之后的标记用作积分时间。标记的位置并不重要,因为 blip 之前和之后的平坦区域对积分结果的贡献很小。

实验结果

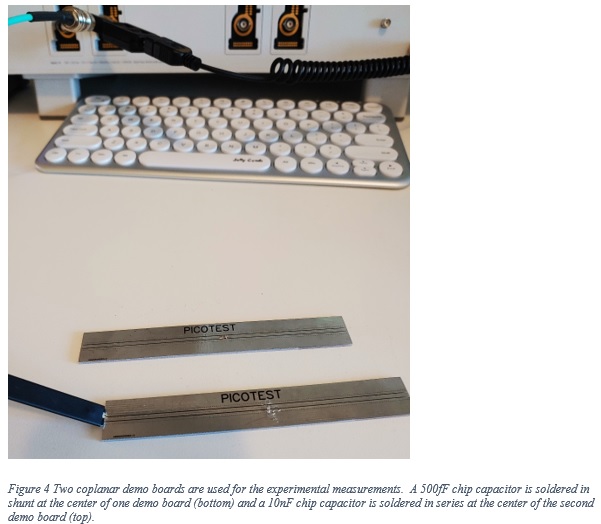

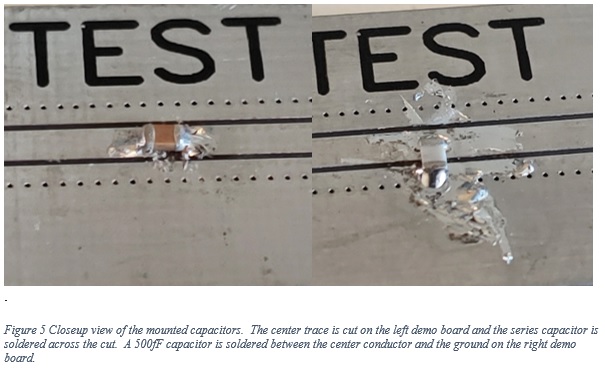

一个 500fF 片式电容器焊接在一个共面演示 PCB 的中心走线和接地之间。切下第二个共面演示板的中心走线,并在切口上焊接一个 10nF 串联电容器。这将允许测量电容器的等效串联电感器 (ESL)。这两个演示板如图 4 所示,安装的电容器的特写如图 5 所示。

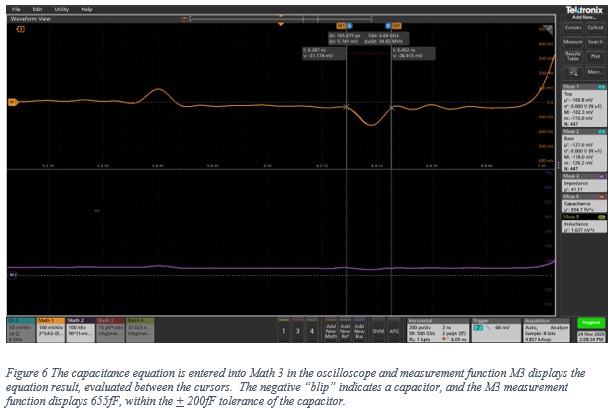

图 6 所示的上部数据迹线是用分流电容器测得的Γ迹线。左边的正(感应)"光点"是探针尖端的感应,我们稍后会测量。光标位于负(电容)"blip"(即分流电容器)之前和之后。门控光标数学功能将电容显示为 655fF,在 500fF 电容器的 200fF 容差范围内。

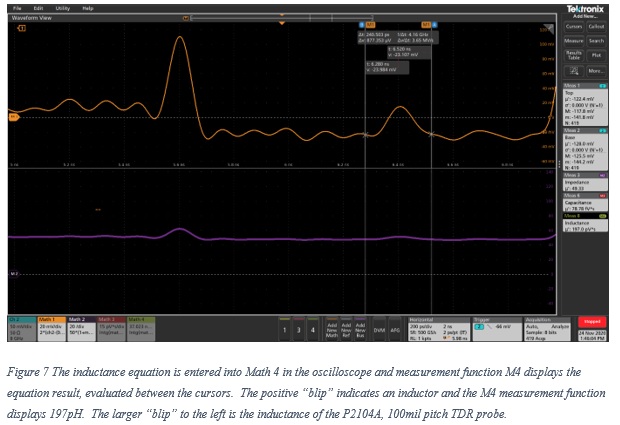

上面的数据迹线如图 7 所示,是使用串联安装电容器测得的Γ迹线。左侧的正 "blip" 是探针尖端的电感。使用较大的探针来显示较大的结果"光点"。光标放置在正(感应)"blip"之前和之后,门控光标数学函数将电感显示为 197pH。这是串联安装电容器的 ESL。

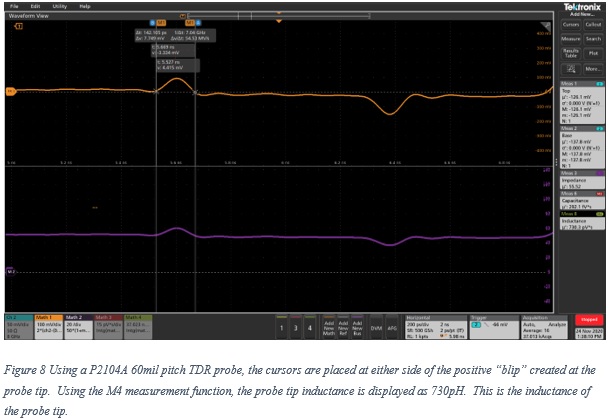

光标测量也可用于测量探针尖端的电感,如图 8 所示,这主要是由于探针弹簧针造成的。探头接触点的正(感应)"光点"是通过将光标放在"光点"之前和之后来测量的。门控光标数学函数将电感显示为 730 pH,该电感是探头带宽的最大贡献者。电感越高,探头带宽越低。

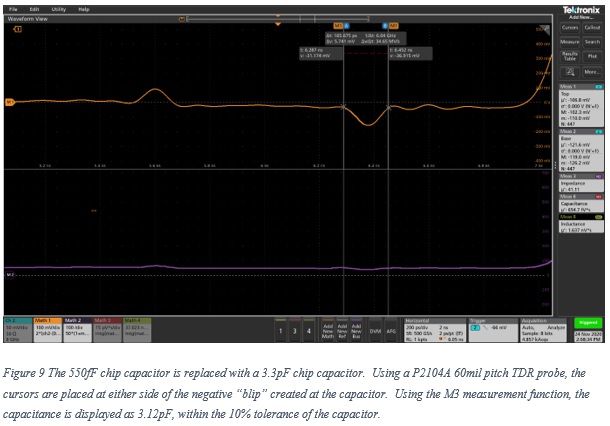

移除 500fF 并联电容器并替换为 3.3pF 片式电容器,以获得第二个实验数据点,如图 9 所示。光标位于负 (电容) "blip" (即分流电容器) 之前和之后。门控光标数学函数将电容显示为 3.12pF,这完全在电容器的 10% 容差范围内。

提高测量效果的 5 个技巧

- 使用单个测量迹线,即连接到 CH2 的 TDR 迹线。通过使波形尽可能填充窗口并包含迹线平均,最大限度地提高此通道的信噪比。

- 设置文件包括脉冲电压、反射系数、阻抗以及电容器和电感器计算。禁用未使用的 traces 将提供更好的 view 所需波形。请务必关闭显示屏;不要删除数学函数。在关闭频道显示之前最大化 SNR。

- 电容器焊接在演示板的中间,允许干净的导入和引出走线,以最大限度地减少测量附近的反射。

- 较小间距的探头提供更高的带宽,从而实现更清晰的测量。

- 在测量未知值之前,始终测量已知值和类似量级。

结论

TDR 提供了 500fF 电容器和 280pH 电感器的精确测量。在这两种情况下,信噪比都很好,迹线很清晰。这表明可以测量更小的电感和电容值。