第一篇:SPI协议基础与工作机制

1. 串行外设接口导论

1.1 SPI的核心定位

- 协议本质 :

全双工同步串行协议(对比UART异步、I²C半双工) - 核心优势 :

- 无寻址开销(通过片选直连)

- 时钟速率可达100MHz+(I²C通常≤1MHz)

- 无复杂的仲裁/应答机制

- 典型应用场景 :

| 设备类型 | 代表芯片 | 时钟速率 |

|---|---|---|

| NOR Flash | Winbond W25Q128JV | 104 MHz |

| 加速度传感器 | ADXL345 | 5 MHz |

| TFT液晶控制器 | ILI9341 | 10 MHz |

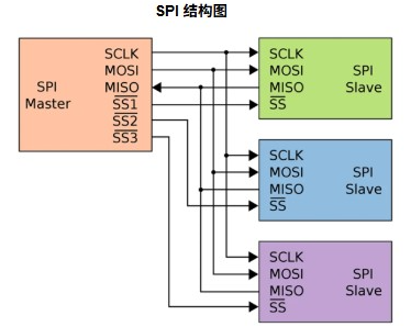

1.2 拓扑结构与信号线

-

四线制基础架构 :

SCK :主设备输出的同步时钟(关键时序参考)

MOSI :主出从入(Master Output Slave Input)

MISO :主入从出(Master Input Slave Output)

CS/SS :从设备片选(低电平有效,每个从设备独立) -

多从机连接方案 :

独立片选 :主设备提供N个CS信号 → 占用IO多但控制简单

菊花链 :所有从设备共享CS,数据级联传输 → 节省IO但延迟增加Master → [Slave1] → [Slave2] → ... → MISO回主设备

2. 协议层深度解析

2.1 时钟极性(CPOL)与相位(CPHA)

-

四种模式定义 :

模式 CPOL CPHA 时钟空闲电平 数据采样沿 0 0 0 Low 上升沿 1 0 1 Low 下降沿 2 1 0 High 下降沿 3 1 1 High 上升沿 -

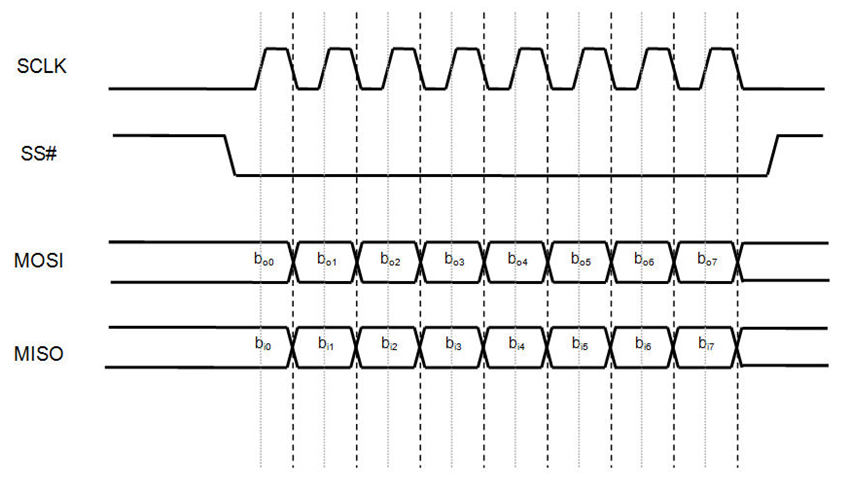

模式0时序详解 (最常用):

-

建立时间(Setup Time) :数据在采样沿前必须稳定的最小时间

tSU≥0.5×TSCK(典型值)

t SU ≥0.5 ×T SC**K(典型值) -

保持时间(Hold Time) :数据在采样沿后必须保持的最小时间

tH≥0.3×TSCK(典型值)

t H≥0.3 ×T SCK (典型值)

2.2 帧结构与数据传输

- 数据位顺序控制 :

MSB First (默认):最高位先传输(如0xAA = 1_0_1_0_1_0_1_0)

LSB First :最低位先传输(0xAA = 0_1_0_1_0_1_0_1)

-

Verilog实现 :

assign mosi = msb_first ? data_reg[7] : data_reg[0];

always @(posedge sck) begin

data_reg <= msb_first ? {data_reg[6:0], 1'b0} : {1'b0, data_reg[7:1]};

end -

多字节传输连续性 :

CS保持低电平 :帧间无空闲时钟,SCK连续运行

应用场景 :Flash存储器连续读(节省CS切换时间)

2.3 片选(CS)协议

- 硬件CS时序要求 :

| 参数 | 公式 | 说明 |

|---|---|---|

| CS建立时间(t_CS_SU) | ≥2 T_SCK | CS激活到首个SCK边沿的延迟 |

| CS撤销时间(t_CS_HD) | ≥1 T_SCK | 末个SCK边沿到CS撤销的延迟 |

- 软件模拟CS的缺陷 :

GPIO切换延迟(>100ns)导致t_CS_SU违例 → 需降频使用

3. 电气特性与物理层

3.1 电压兼容性设计

- 电平转换方案 :

| 主设备电压 | 从设备电压 | 解决方案 |

|---|---|---|

| 3.3V | 5V | 单向电平转换器(如TXB0104) |

| 1.8V | 3.3V | 双向自动方向转换器(如SN74LVC8T245) |

- 驱动能力计算 :

最大负载电容公式 :

C_LO AD ≤t_R/(0.5 ×R_DRIVE)

例如:t_R=10ns, R_DRIVE=50Ω → C_LOAD ≤ 400 pF

3.2 信号完整性优化

- 阻抗匹配方案 :

| 问题现象 | 解决方案 | 电路示意图 |

|---|---|---|

| 信号振铃 | 源端串联电阻(22-33Ω) | SCK ──[R]─→ Slave |

| MISO回波反射 | 并联终端电阻(50Ω对地) | MISO ──[R]─┐ GND |

4. SPI变种与扩展

4.1 四线SPI(QSPI)

- 协议加速原理 :

信号线扩展 :- IO0(MOSI)、IO1(MISO)、IO2(WP#)、IO3(HOLD#)

- 数据传输模式 :

| 模式 | 数据线数量 | 带宽增益 |

|---|---|---|

| Standard SPI | 1 | 1x |

| Dual SPI | 2 | 2x |

| Quad SPI | 4 | 4x |

- 应用实例 :

Winbond W25Q128JV在Quad模式下速率可达80MB/s(对比20MB/s标准SPI)

4.2 菊花链(Daisy-Chain)

-

数据流转发机制 :

主设备发送: [Data1][Data2][Data3] → Slave1接收Data1,转发[Slave1_Data][Data2][Data3] → Slave2接收Data2,转发[Slave2_Data][Slave1_Data][Data3] → 主设备最终接收: [Slave3_Data][Slave2_Data][Slave1_Data] -

级联移位寄存器实现 :

verilogalways @(posedge sck) begin if (cs_n == 0) begin shift_reg <= {shift_reg[14:0], mosi}; // 16位移位寄存器 miso <= shift_reg[15]; // 输出最高位 end end

4.3 三线半双工SPI

-

省IO方案 :

合并MOSI/MISO为SIO线(双向传输)

方向切换时序 :主设备发数据: 驱动SIO输出 从设备回数据: 主设备释放SIO(高阻态),从设备驱动SIO

附录:SPI模式配置速查表

| 设备类型 | 推荐模式 | 最大时钟 | 特殊要求 |

|---|---|---|---|

| AT25 SPI Flash | Mode 0 | 50 MHz | CS撤销后等待1μs |

| NXP IMU传感器 | Mode 3 | 10 MHz | 数据LSB优先 |

| TI ADC128S022 | Mode 1 | 8 MHz | CS激活期间SCK持续 |

关键结论 :

- 模式选择 :工业设备普遍采用Mode 0(85%场景),Mode 3用于特定传感器

- 速率瓶颈 :长走线(>20cm)需降至10MHz以下,PCB阻抗匹配决定上限

- 变种选择 :QSPI适用于>50MB/s需求,三线制适合IO极度受限场景