D-PHY物理层的包头纠错码(Packet Header ECC)

1. 核心功能

- 作用对象 :仅保护 长包/短包的包头(PH) (32位),包括:

数据标识(DI, 1字节)

字计数(WC, 2字节) - 核心能力 :

单比特错误纠正

双比特错误检测 - 不覆盖范围 :

包负载数据(由CRC校验)

C-PHY物理层(仅D-PHY适用)

2. ECC实现机制

(1) 输入数据映射

将24位包头按以下顺序映射为ECC输入:

text

D[23:16] = WC[15:8] (MSB)

D[15:8] = WC[7:0]

D[7:0] = DI[7:0] (2) 校验码生成

-

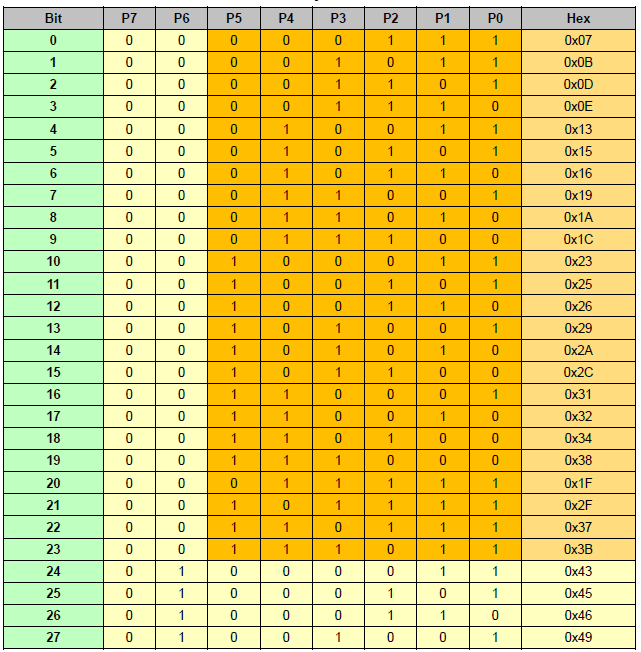

表格 :

-

算法 :改进型汉明码(Hamming-Modified Code)

-

校验位 :6位

-

生成逻辑 :

python# 示例:P0计算(基于表5橙色区域) P0 = D0^D1^D2^D4^D5^D7^D10^D11^D13^D16^D20^D21^D22^D23 -

输出 :8位ECC(高2位=0,低6位=校验值)

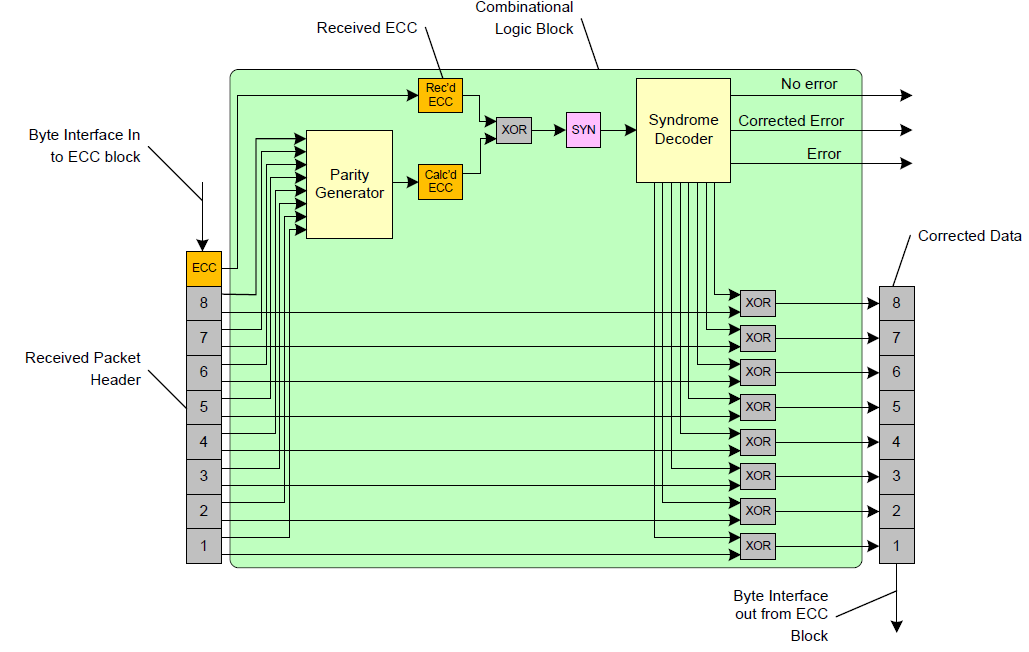

3. 接收端处理流程

-

重新计算ECC :对接收到的DI+WC生成新ECC'

-

计算症候(Syndrome) :

S = Received_ECC ⊕ ECC' -

错误处理 :

症候值 操作 说明 S=0无错误 - S∈表4纠正单比特错误 查表4定位错误位并取反 S∉表4标记不可纠正错误(>2比特) 丢弃包或上报应用层

4. 关键设计约束

-

位宽限制 :

仅支持24位包头(64位模式禁用,ECC高位固定为0)。

-

硬件实现 :

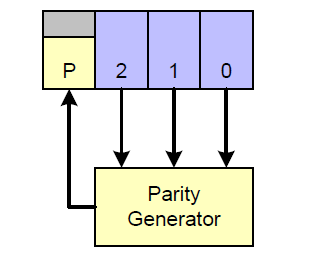

发送端 :并行计算, 输入为3 个字节数据

-

接收端 :syndrome查表解码

-

错误范围 :

ECC不保护负载数据(负载由CRC校验)。

5. 示例说明(图46)

- 输入 :

DI=0x37,WC_LSB=0xF0,WC_MSB=0x01

→ 映射为24位数据:0x01_F0_37 - ECC计算 :

输出ECC=0x3F(二进制0011_1111) - 传输包头 :

[DI=0x37] [WC_LSB=0xF0] [WC_MSB=0x01] [ECC=0x3F]

总结 :此ECC机制是D-PHY链路可靠性的核心保障,通过汉明码变种实现包头关键字段的实时纠错,但需严格限定24位输入范围。工程实现需重点优化症候查表逻辑以降低延迟。