用 LaTeX 优化 FPGA 开发:结合符号计算与 Vivado 工具链(一)

系列文章目录

第一章:深入了解 LaTeX:科技文档排版的利器

第二章:LaTeX 下载安装保姆级教程

第三章:LaTeX 创建工程并生成完整文档指南

第四章:LaTeX 表格制作全面指南

第五章:LaTeX 复杂图形绘制教程:从基础到进阶

第六章:学术排版利器 LaTeX:疑难问题排查与高效应用技巧

第七章:LaTeX 引用参考文献的全面指南

文章目录

- [用 LaTeX 优化 FPGA 开发:结合符号计算与 Vivado 工具链(一)](#用 LaTeX 优化 FPGA 开发:结合符号计算与 Vivado 工具链(一))

- 系列文章目录

-

- 一、引言

- [二、LaTeX 与 FPGA 开发集成概述](#二、LaTeX 与 FPGA 开发集成概述)

-

- [2.1 LaTeX 在 FPGA 开发中的优势](#2.1 LaTeX 在 FPGA 开发中的优势)

- [2.2 与 Vivado 工具链的集成点](#2.2 与 Vivado 工具链的集成点)

- [三、使用 LaTeX 生成 FPGA 设计文档](#三、使用 LaTeX 生成 FPGA 设计文档)

-

- [3.1 文档结构规划](#3.1 文档结构规划)

- [3.2 使用 TikZ 绘制 FPGA 架构图](#3.2 使用 TikZ 绘制 FPGA 架构图)

- [3.3 代码集成与语法高亮](#3.3 代码集成与语法高亮)

- [3.4 集成 Vivado 生成的报告](#3.4 集成 Vivado 生成的报告)

- [3.5 表格和数据展示](#3.5 表格和数据展示)

一、引言

FPGA(现场可编程门阵列)开发是一个复杂的过程,需要同时关注硬件设计、逻辑实现和系统集成。随着 FPGA 设计规模和复杂度的不断提高,文档管理 和数学计算 在开发流程中的重要性日益凸显。传统的 FPGA 开发工具如 Vivado 虽然提供了强大的设计和验证功能,但在文档生成和符号计算方面的能力有限(5)。

LaTeX 作为一种专业的文档排版系统,在科技文献编写、公式排版和图表生成方面具有显著优势。将 LaTeX 与 FPGA 开发结合,可以为工程师提供一个统一的环境,用于记录设计思路、推导数学模型、生成高质量文档,并与 Vivado 工具链协同工作(3)。

本文将详细介绍如何利用 LaTeX 生成专业的 FPGA 设计文档,同时进行符号计算和公式处理,并与 Vivado 开发工具链集成,从而优化整个 FPGA 开发流程。

二、LaTeX 与 FPGA 开发集成概述

2.1 LaTeX 在 FPGA 开发中的优势

LaTeX 作为文档生成工具,为 FPGA 开发提供了以下关键优势:

-

专业排版质量 :LaTeX 能够生成高质量的文档,满足学术和工业标准,特别适合编写 FPGA 设计文档、技术报告和论文(14)。

-

数学公式处理 :LaTeX 内置强大的数学排版功能,能够轻松处理复杂的数学表达式、逻辑推导和算法描述,这对于 FPGA 开发中的理论分析至关重要(16)。

-

图表集成 :LaTeX 支持多种图表格式,可以清晰展示 FPGA 设计架构、数据流图和状态机等关键设计元素(26)。

-

版本控制友好 :LaTeX 文档本质上是纯文本文件,便于与版本控制系统(如 Git)集成,方便团队协作和设计历史追踪(3)。

-

可扩展性 :通过丰富的 LaTeX 包和第三方工具,可以扩展 LaTeX 的功能,满足特定的 FPGA 开发需求(27)。

2.2 与 Vivado 工具链的集成点

将 LaTeX 与 Vivado 集成,可以在以下关键环节优化 FPGA 开发流程:

-

设计文档生成 :将 Vivado 生成的设计报告、时序分析结果和资源使用情况整合到 LaTeX 文档中,形成完整的设计记录(39)。

-

数学模型与算法推导 :在 LaTeX 中进行符号计算和数学建模,生成 FPGA 实现所需的公式和算法,并将结果直接应用于 Vivado 设计(17)。

-

验证与测试文档 :结合 LaTeX 的表格和图表功能,记录和展示 FPGA 设计的验证结果和测试数据(41)。

-

设计决策记录 :在 LaTeX 文档中记录设计决策、权衡分析和替代方案,提高设计透明度和可追溯性(1)。

三、使用 LaTeX 生成 FPGA 设计文档

3.1 文档结构规划

一个完整的 FPGA 设计文档应包含以下关键部分,这些部分可以通过 LaTeX 高效组织和呈现:

-

设计概述 :简要描述设计目标、范围和主要功能(1)。

-

架构设计:高层次描述 FPGA 设计的整体架构和模块划分。

-

详细设计:各模块的详细逻辑设计、接口定义和信号描述。

-

时序分析:关键路径的时序分析结果和时序约束说明。

-

资源使用情况:FPGA 资源(如 LUT、FF、BRAM、DSP 等)的使用情况总结。

-

验证策略:描述验证方法、测试用例和预期结果。

-

实现细节:包括综合、布局布线和比特流生成的关键参数和设置。

-

附录:包含详细的公式推导、重要代码片段和参考资料。

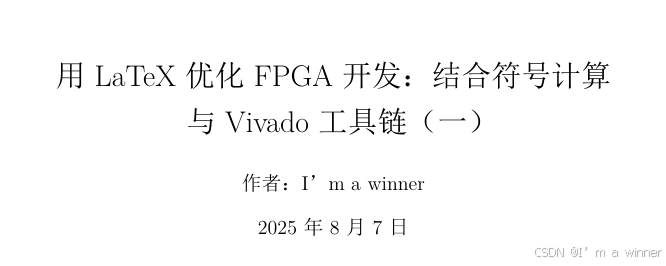

以下是一个基本的 LaTeX 文档结构示例:

\documentclass{article}

\usepackage{graphicx}

\usepackage{amsmath}

\usepackage{amsfonts}

\usepackage{tikz}

\usetikzlibrary{circuits.logic.US}

\begin{document}

\title{FPGA设计文档:我的项目名称}

\author{你的名字}

\date{\today}

\maketitle

\section{设计概述}

简要描述设计目标和主要功能。

\section{系统架构}

\input{architecture.tex} % 包含架构图的TeX文件

\section{详细设计}

\input{module1.tex}

\input{module2.tex}

\section{时序分析}

\input{timing\_analysis.tex}

\section{资源使用}

\input{resource\_usage.tex}

\end{document}

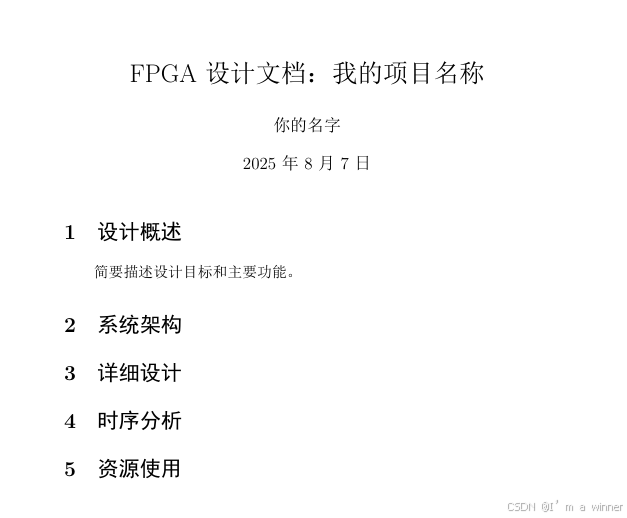

3.2 使用 TikZ 绘制 FPGA 架构图

LaTeX 的 TikZ 包是绘制 FPGA 架构图和逻辑图的强大工具,特别是结合电路逻辑库使用时(28)。以下是一些关键技巧:

-

基本模块绘制 :使用 TikZ 的

circuits.logic.US库可以绘制标准逻辑门和触发器(30):\begin{tikzpicture}[circuit logic US]

\node[and gate] (AND) at (0,0) {};

\node[or gate] (OR) at (2,0) {};

\node[not gate] (NOT) at (4,0) {};

\draw (AND.output) -- (OR.input 1);

\draw (OR.output) -- (NOT.input);

\end{tikzpicture}

-

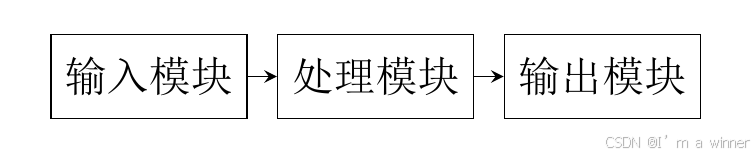

数据流图 :使用标准 TikZ 形状和箭头可以创建高层次的数据流图(27):

\tikzstyle{block} = [rectangle, draw, minimum height=2em, minimum width=4em]

\tikzstyle{arrow} = [->, >=stealth]\begin{tikzpicture}[node distance=2cm]

\node[block] (input) {输入模块};

\node[block] (processing) [right of=input] {处理模块};

\node[block] (output) [right of=processing] {输出模块};\draw[arrow] (input) -- (processing); \draw[arrow] (processing) -- (output);\end{tikzpicture}

-

寄存器传输级 (RTL) 图 :结合电路逻辑库和自定义形状,可以创建 RTL 级别的详细设计图(31):

\usetikzlibrary{circuits.logic.US, arrows.meta}

\begin{tikzpicture}[circuit logic US, >=Stealth]

% 触发器

\node[dff, clock input] (dff1) at (0,0) {DFF1};

\node[dff, clock input] (dff2) at (3,0) {DFF2};% 组合逻辑 \node[and gate] (and1) at (1.5,-1.5) {}; % 连接 \draw (dff1.Q) -- (and1.input 1); \draw (dff2.Q) -- (and1.input 2); \draw (and1.output) -- ++(0,-0.5) node[right] {输出}; % 时钟信号 \draw (dff1.clock) -- ++(-1,0) node[left] {CLK}; \draw (dff2.clock) -- (dff1.clock |- dff2.clock);\end{tikzpicture}

-

总线和多比特信号 :使用

decorations.pathreplacing库可以创建总线符号和注释(27):\usetikzlibrary{decorations.pathreplacing}

\begin{tikzpicture}

% 模块

\node[rectangle, draw] (module) at (0,0) {模块};% 总线 \draw (module.west) -- ++(-1,0) node[left] {数据总线[31:0]}; % 总线注释 \draw[decorate, decoration={brace, mirror}] (-1.5,-0.5) -- (-1.5,0.5) node[midway, left] {32位};\end{tikzpicture}

3.3 代码集成与语法高亮

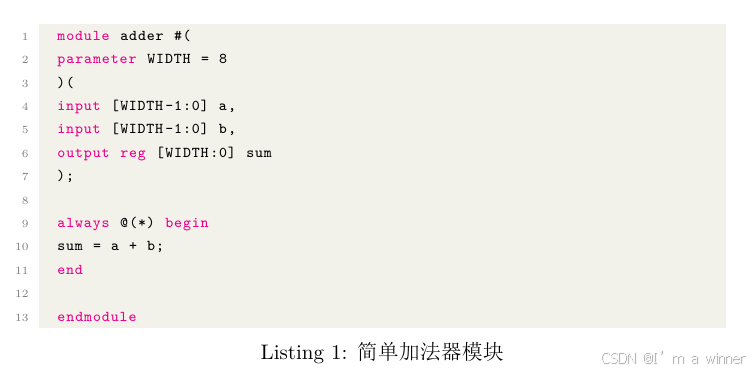

在 FPGA 设计文档中,通常需要展示关键的 Verilog 或 VHDL 代码片段。LaTeX 的listings包提供了优秀的代码高亮和格式化功能(3):

\usepackage{listings}

\usepackage{xcolor}

\definecolor{codegreen}{rgb}{0,0.6,0}

\definecolor{codegray}{rgb}{0.5,0.5,0.5}

\definecolor{codepurple}{rgb}{0.58,0,0.82}

\definecolor{backcolour}{rgb}{0.95,0.95,0.92}

\lstdefinestyle{mystyle}{

backgroundcolor=\color{backcolour},

commentstyle=\color{codegreen},

keywordstyle=\color{magenta},

numberstyle=\tiny\color{codegray},

stringstyle=\color{codepurple},

basicstyle=\ttfamily\footnotesize,

breakatwhitespace=false,

breaklines=true,

captionpos=b,

keepspaces=true,

numbers=left,

numbersep=5pt,

showspaces=false,

showstringspaces=false,

showtabs=false,

tabsize=2

}

\lstset{style=mystyle}使用上述定义的样式,可以在文档中插入 Verilog 代码:

\begin{lstlisting}[language=Verilog, caption=简单加法器模块]

module adder #(

parameter WIDTH = 8

)(

input [WIDTH-1:0] a,

input [WIDTH-1:0] b,

output reg [WIDTH:0] sum

);

always @(*) begin

sum = a + b;

end

endmodule

\end{lstlisting}

3.4 集成 Vivado 生成的报告

Vivado 可以生成多种报告文件,包括时序分析、资源使用和综合结果。将这些报告集成到 LaTeX 文档中,可以形成完整的设计记录(39):

-

时序分析报告 :Vivado 的

report_timing命令可以生成详细的时序分析报告。可以将报告的关键部分复制到 LaTeX 文档中,或者使用脚本来自动提取关键数据(52):\section{时序分析}

\lstinputlisting[language=none]{timing_report.rpt}

-

资源使用报告 :Vivado 的

report_utilization命令生成资源使用报告。可以将报告内容直接包含在 LaTeX 文档中,或者使用表格形式重新组织关键数据(41):\section{资源使用}

\lstinputlisting[language=none]{utilization_report.rpt}

-

自动生成报告 :可以编写 Tcl 脚本,在 Vivado 中自动生成报告并保存为文本文件,供 LaTeX 文档使用(49):

# 生成时序报告

report_timing > timing_report.rpt

# 生成资源使用报告

report_utilization > utilization_report.rpt

3.5 表格和数据展示

在 FPGA 文档中,经常需要展示各种表格,如资源使用情况、时序分析结果和测试结果。LaTeX 提供了强大的表格生成功能(14):

-

基本表格:

\begin{table}[ht]

\centering

\begin{tabular}{|c|c|c|}

\hline

资源类型 & 使用量 & 可用量 \\

\hline

LUT & 456 & 10000 \\

\hline

FF & 320 & 20000 \\

\hline

BRAM & 8 & 50 \\

\hline

DSP & 4 & 100 \\

\hline

\end{tabular}

\caption{FPGA资源使用情况}

\end{table}

-

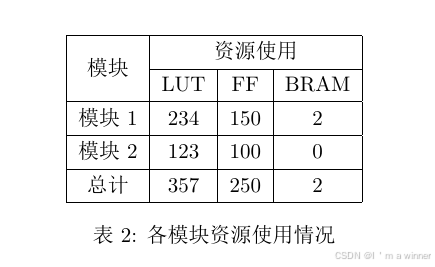

复杂表格 :使用

multirow和multicolumn命令可以创建更复杂的表格结构:\usepackage{multirow}

\begin{table}[ht]

\centering

\begin{tabular}{|c|c|c|c|}

\hline

\multirow{2}{*}{模块} & \multicolumn{3}{c|}{资源使用} \\

\cline{2-4}

& LUT & FF & BRAM \\

\hline

模块1 & 234 & 150 & 2 \\

\hline

模块2 & 123 & 100 & 0 \\

\hline

总计 & 357 & 250 & 2 \\

\hline

\end{tabular}

\caption{各模块资源使用情况}

\end{table}

-

从 CSV 文件导入数据 :可以使用

pgfplotstable包从 CSV 文件导入数据并生成表格,这在自动化生成报告时特别有用(42):\usepackage{pgfplotstable}

\begin{table}[ht]

\centering

\pgfplotstabletypeset[

col sep=comma,

columns={module, lut, ff, bram},

columns/module/.style={column name=模块},

columns/lut/.style={column name=LUT},

columns/ff/.style={column name=FF},

columns/bram/.style={column name=BRAM},

]{resource_usage.csv}

\caption{资源使用情况}

\end{table}