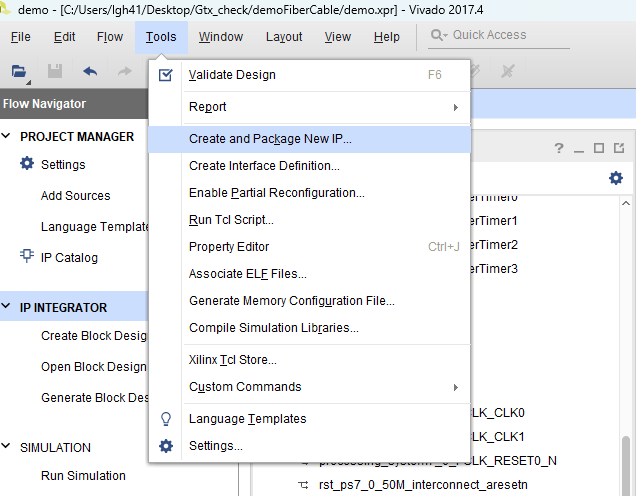

1、打开工程,并建创建IP核

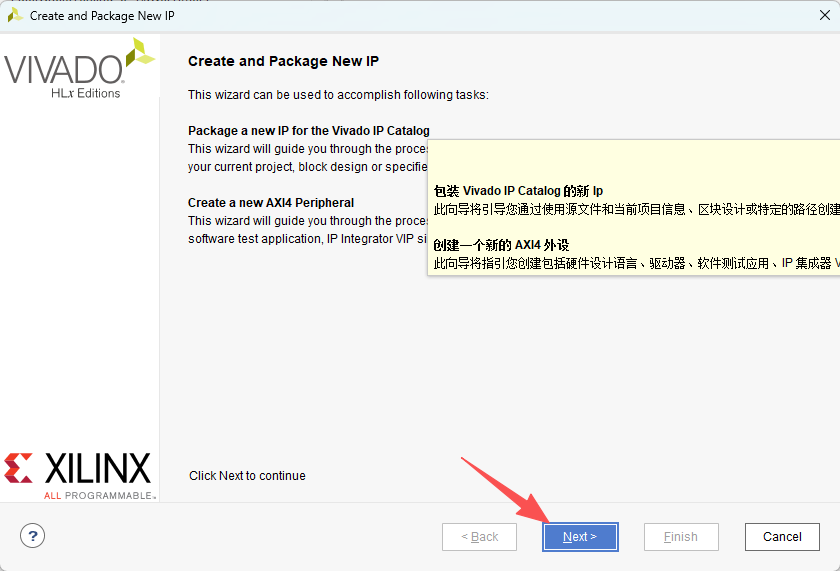

2、点击下一步

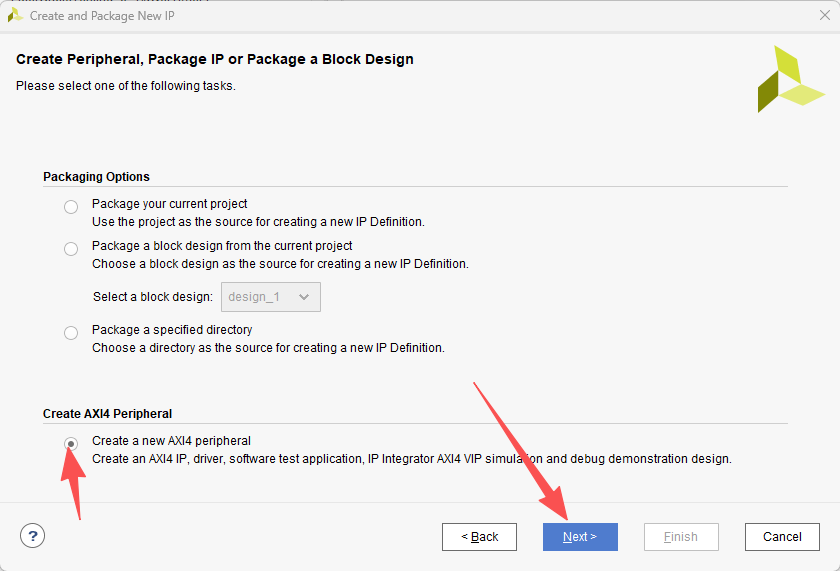

3、选择AXI4,点击下一步

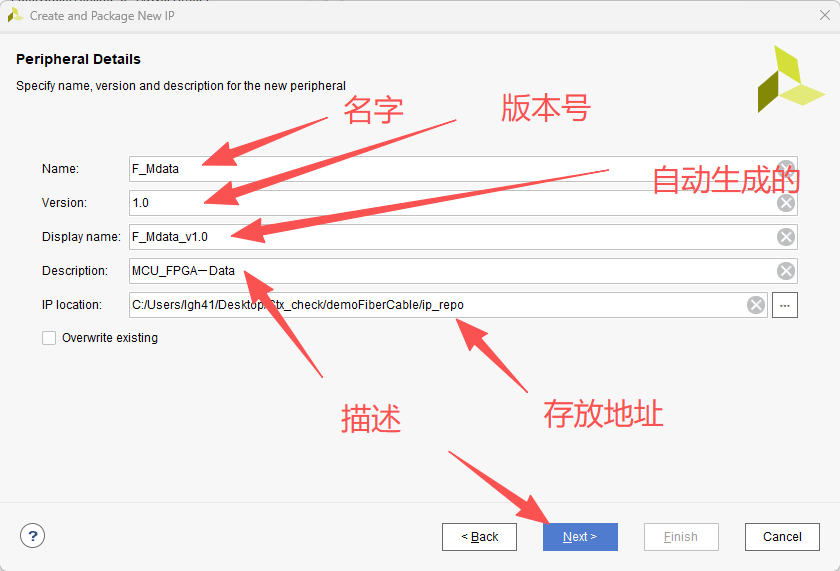

4、起名字,并设置存储位置

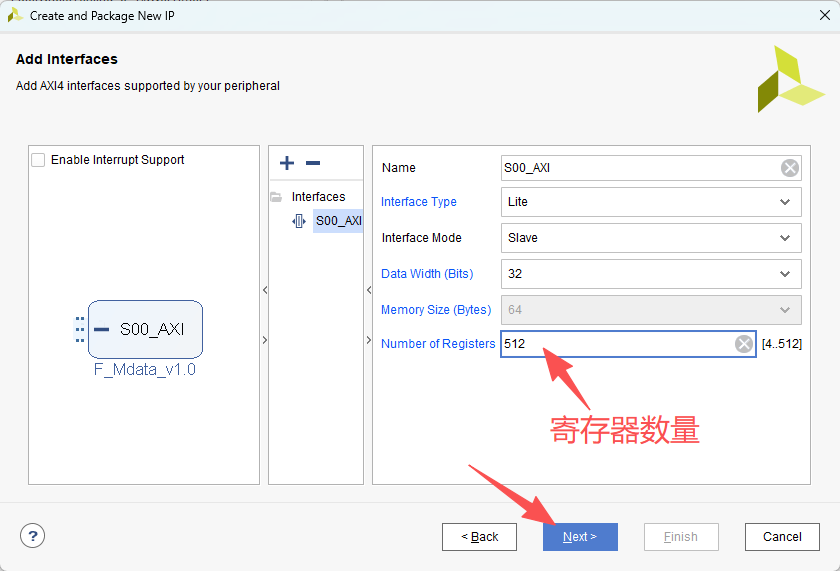

5、设置一次传输,数据最大传输的数量

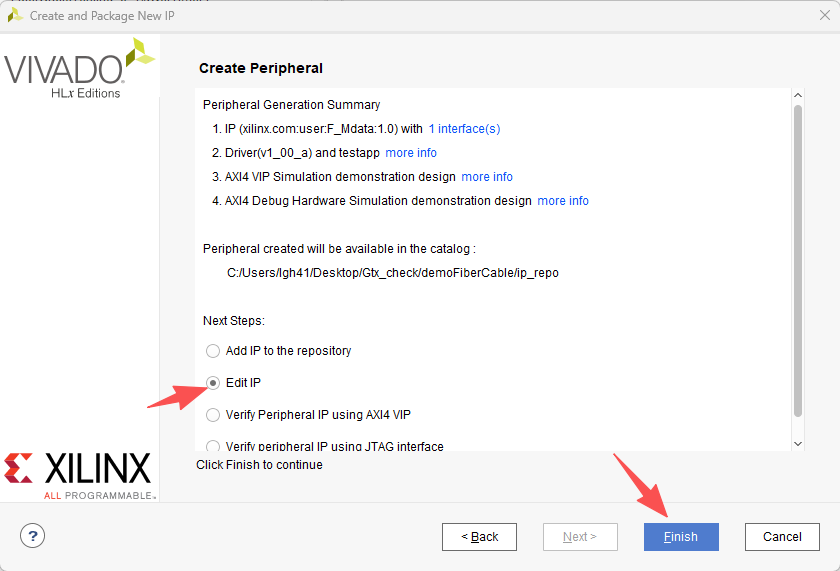

6、建立IP和编辑IP

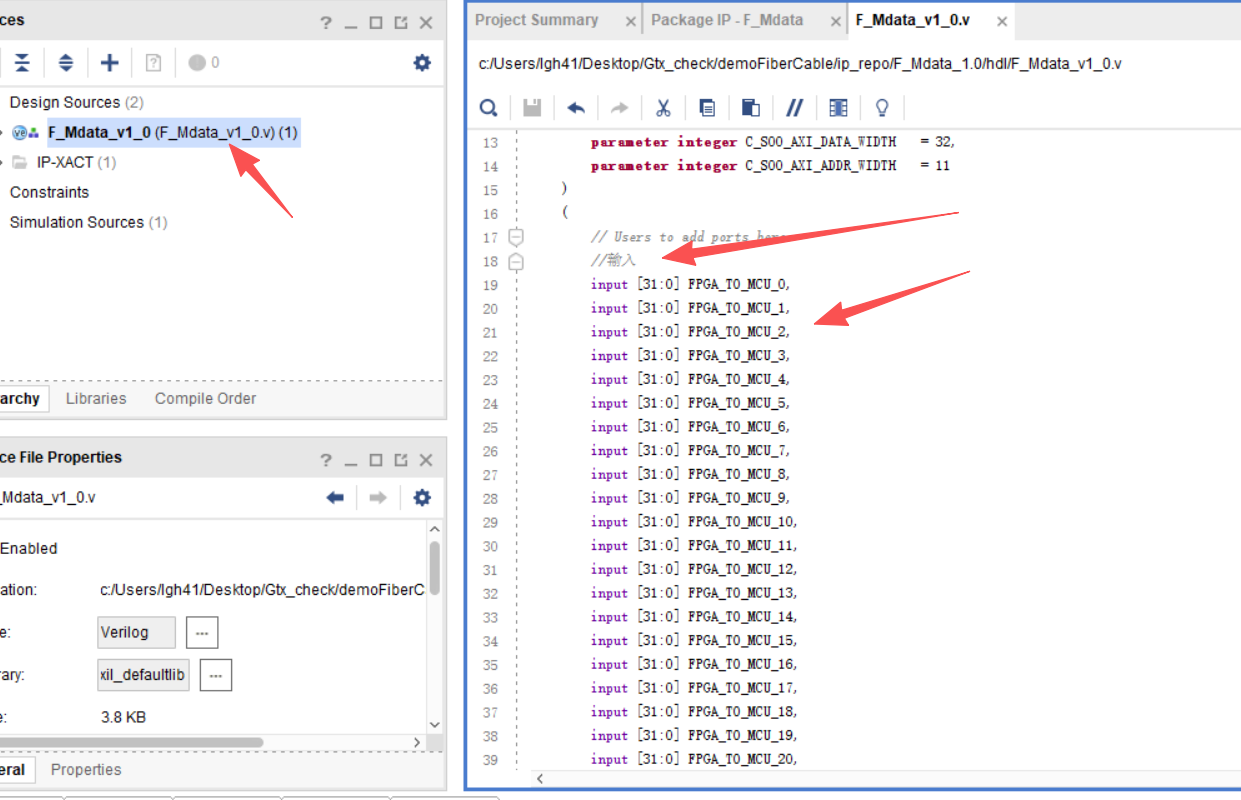

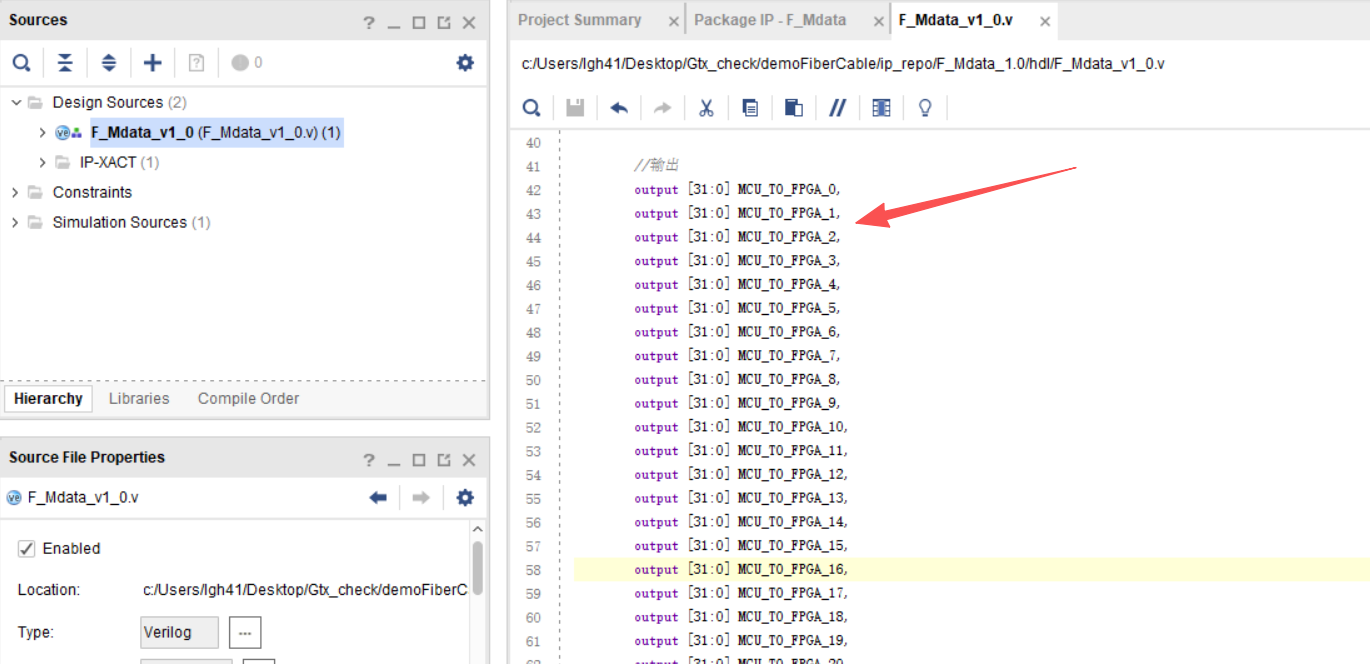

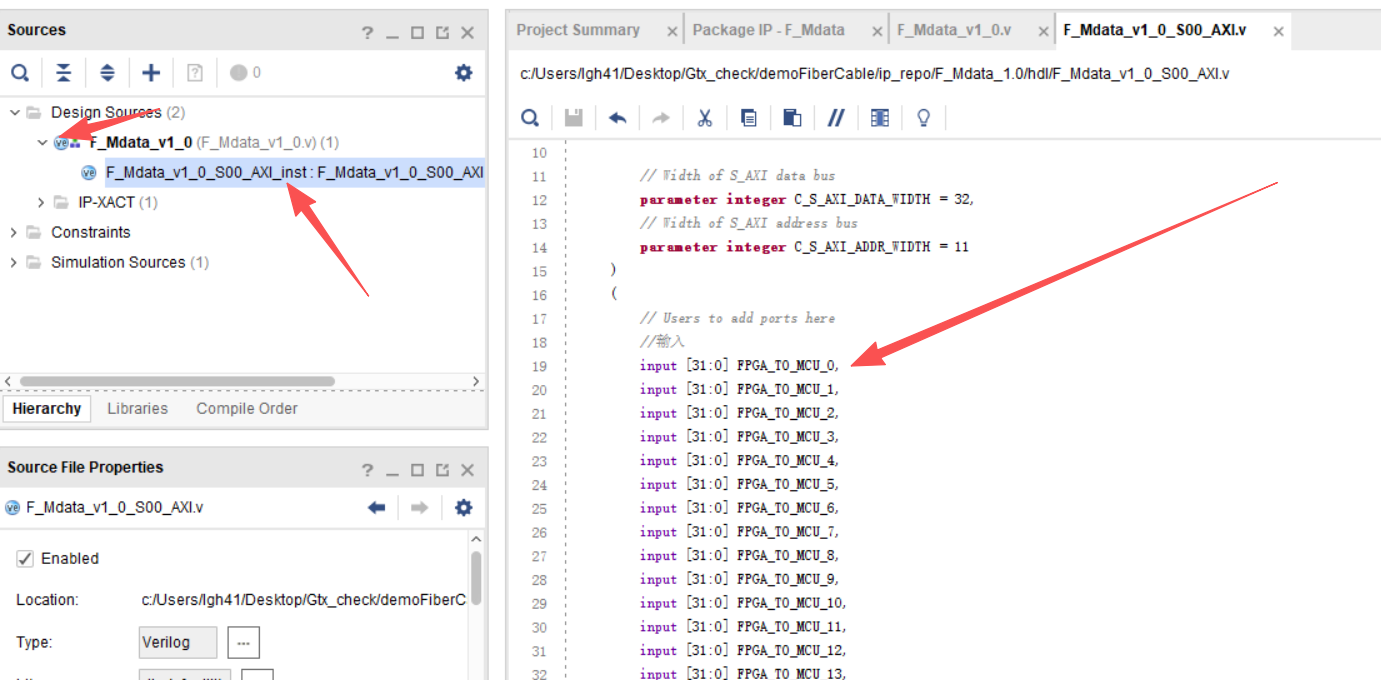

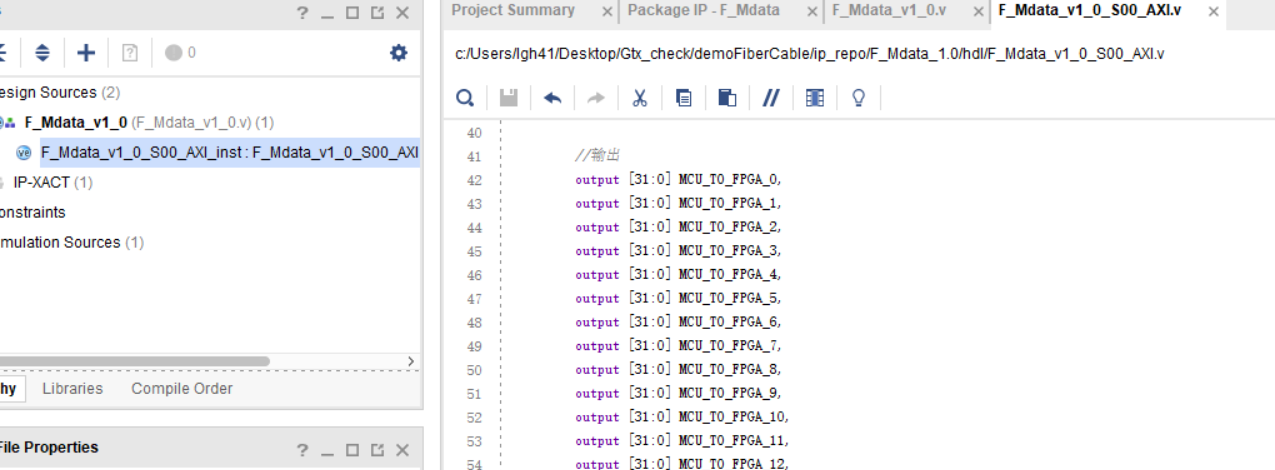

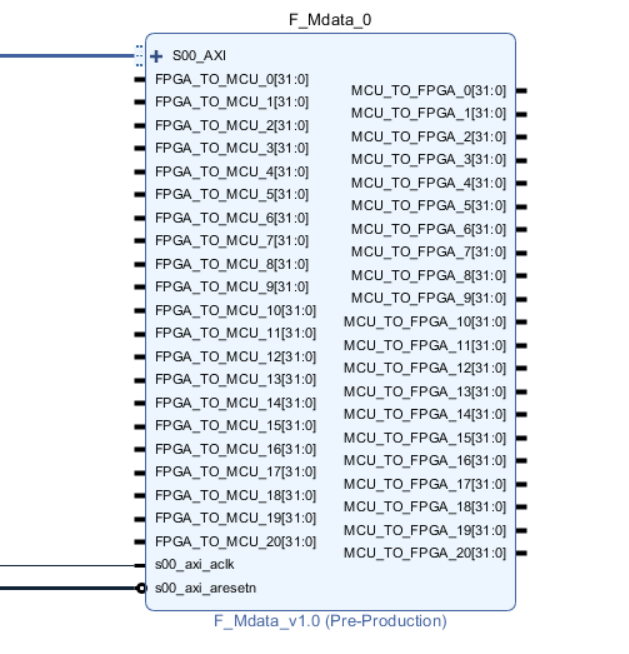

7、建立连接口,根据第5步最多设置512*32个字节,注意分配输出和输入

intput 是FPGA到MCU,output是MCU到FPGA数据传输

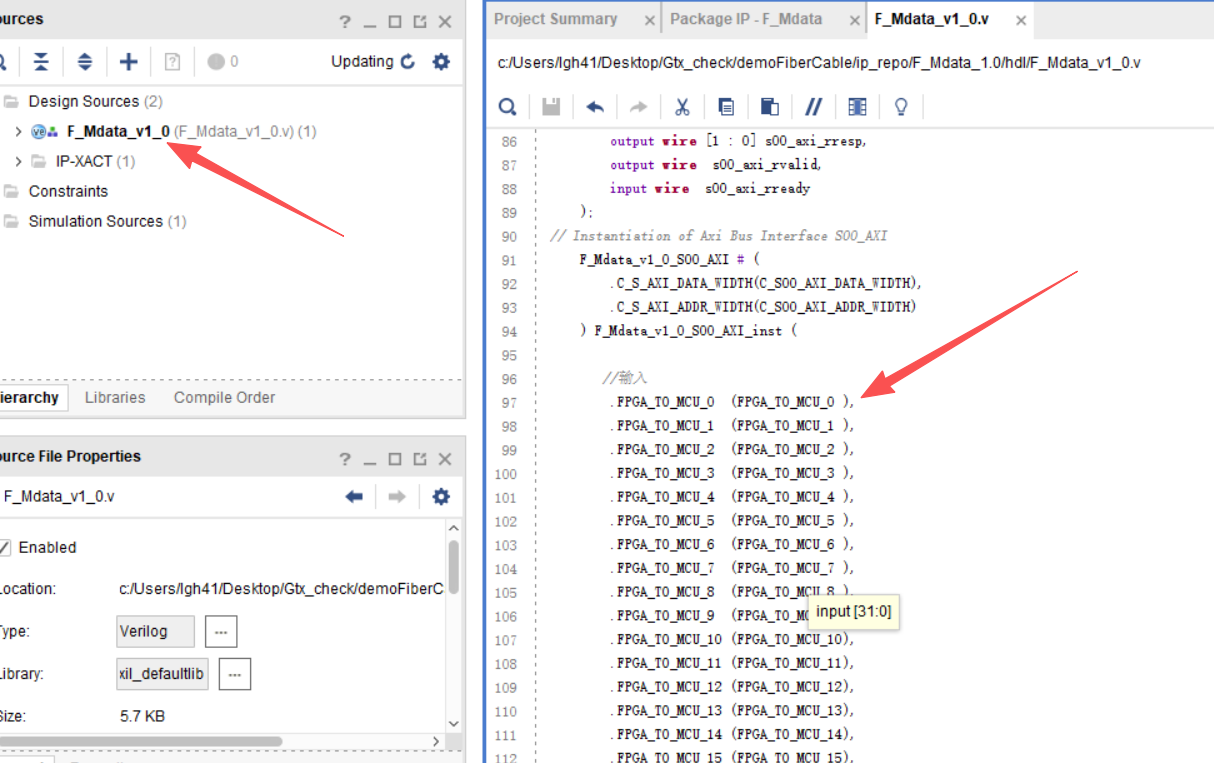

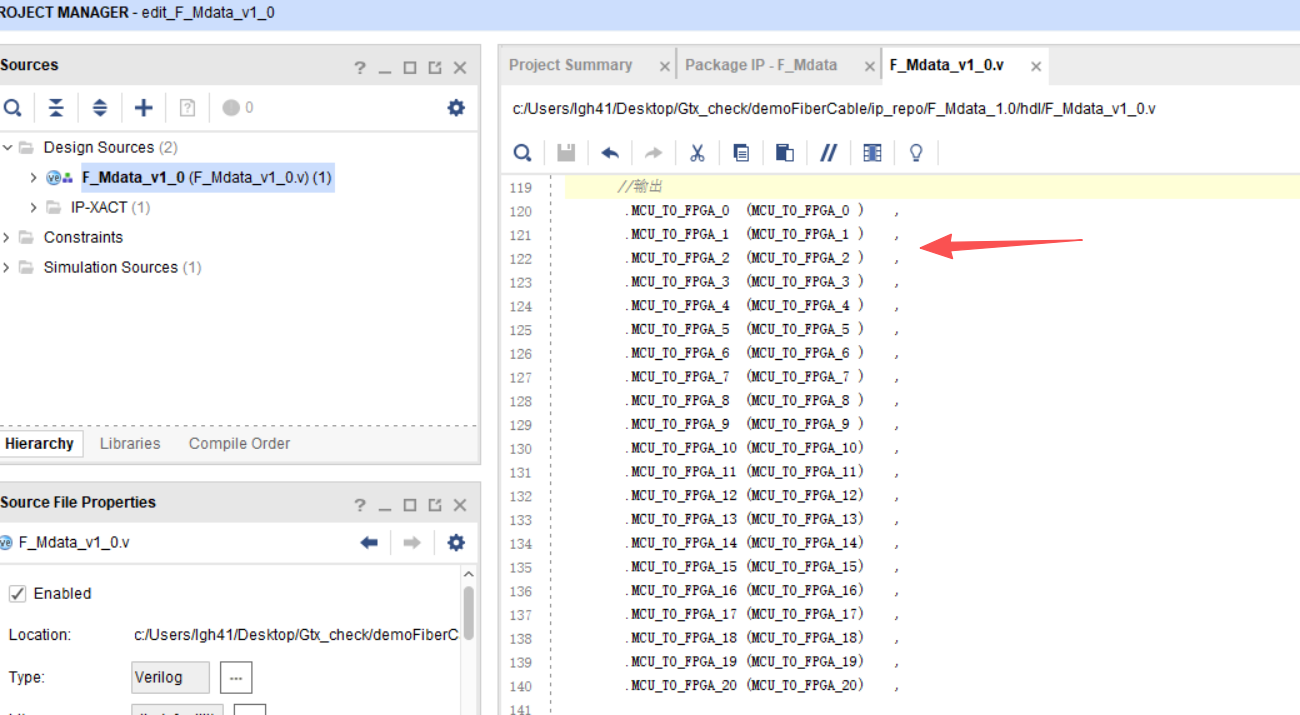

8、建立内部例化调用

9、数据例化内部调用,建立链接,名称、类型、大小和第7步要相同

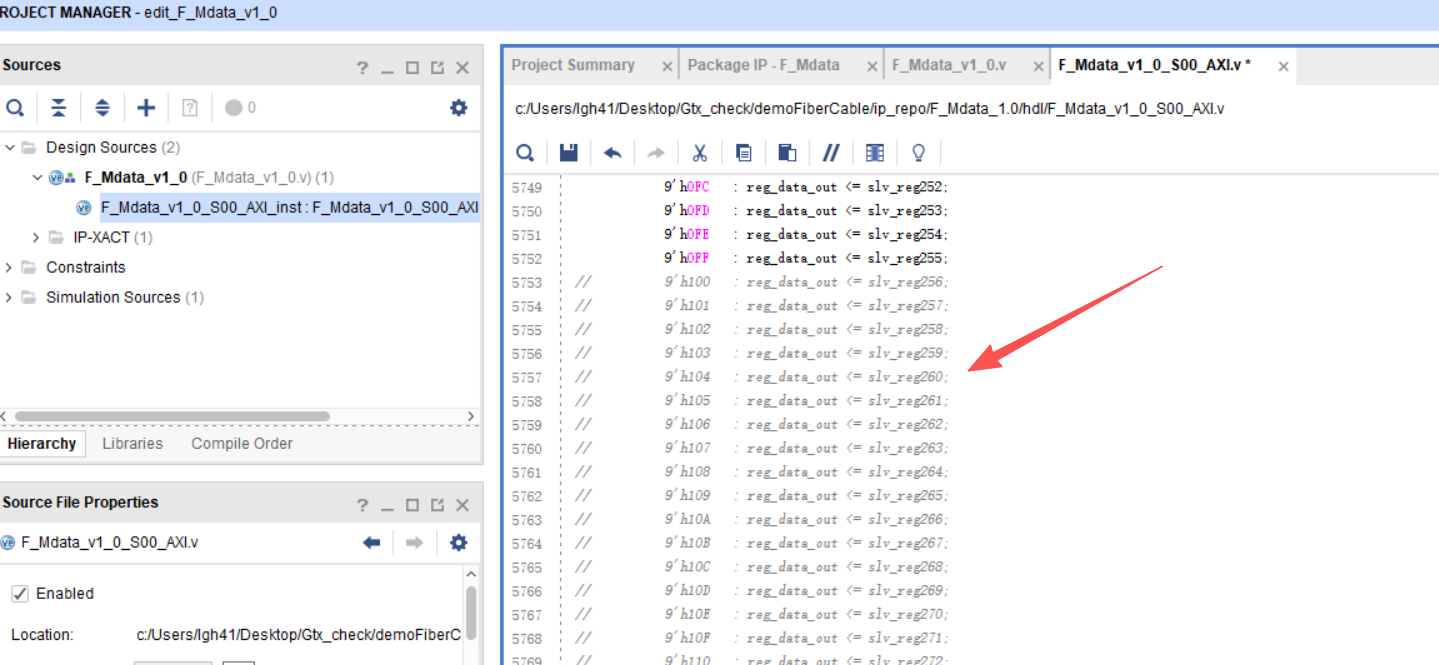

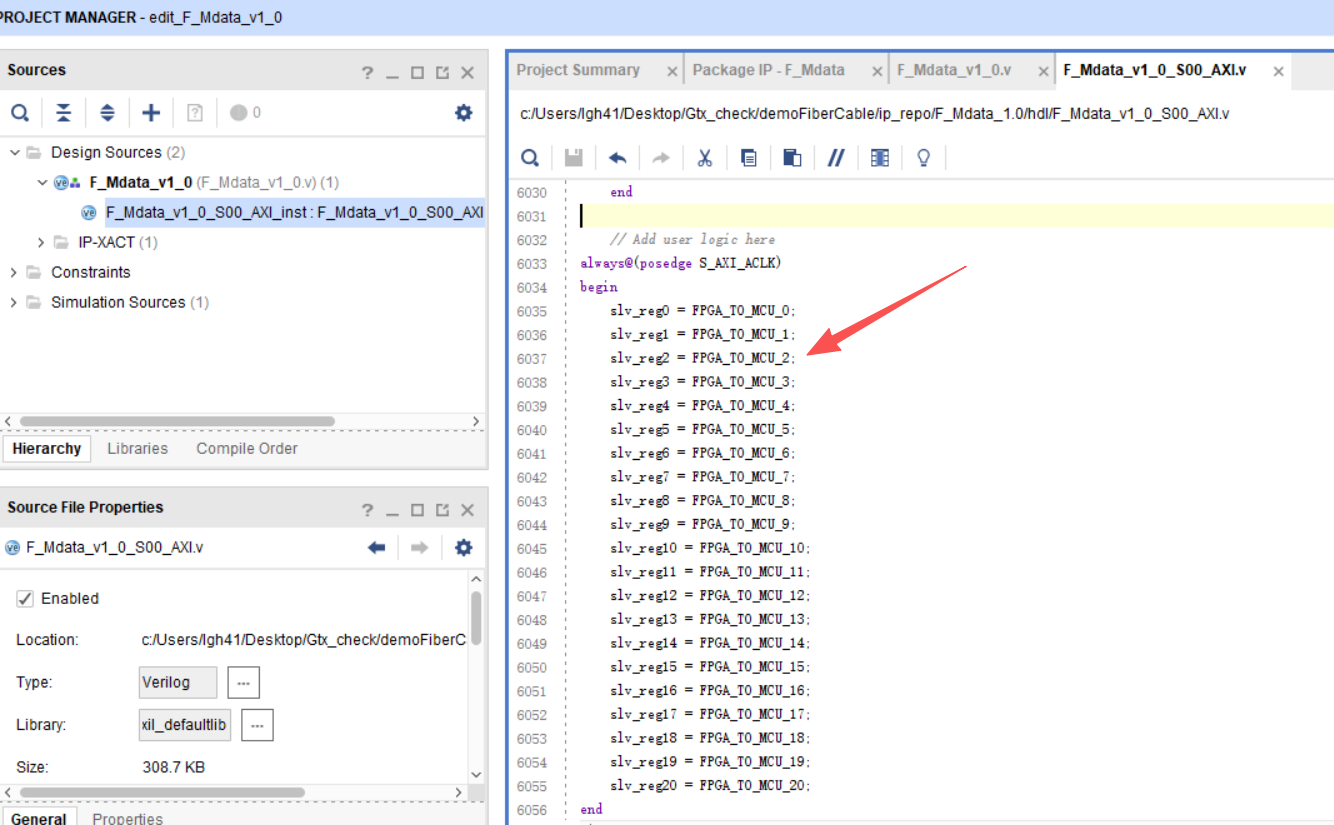

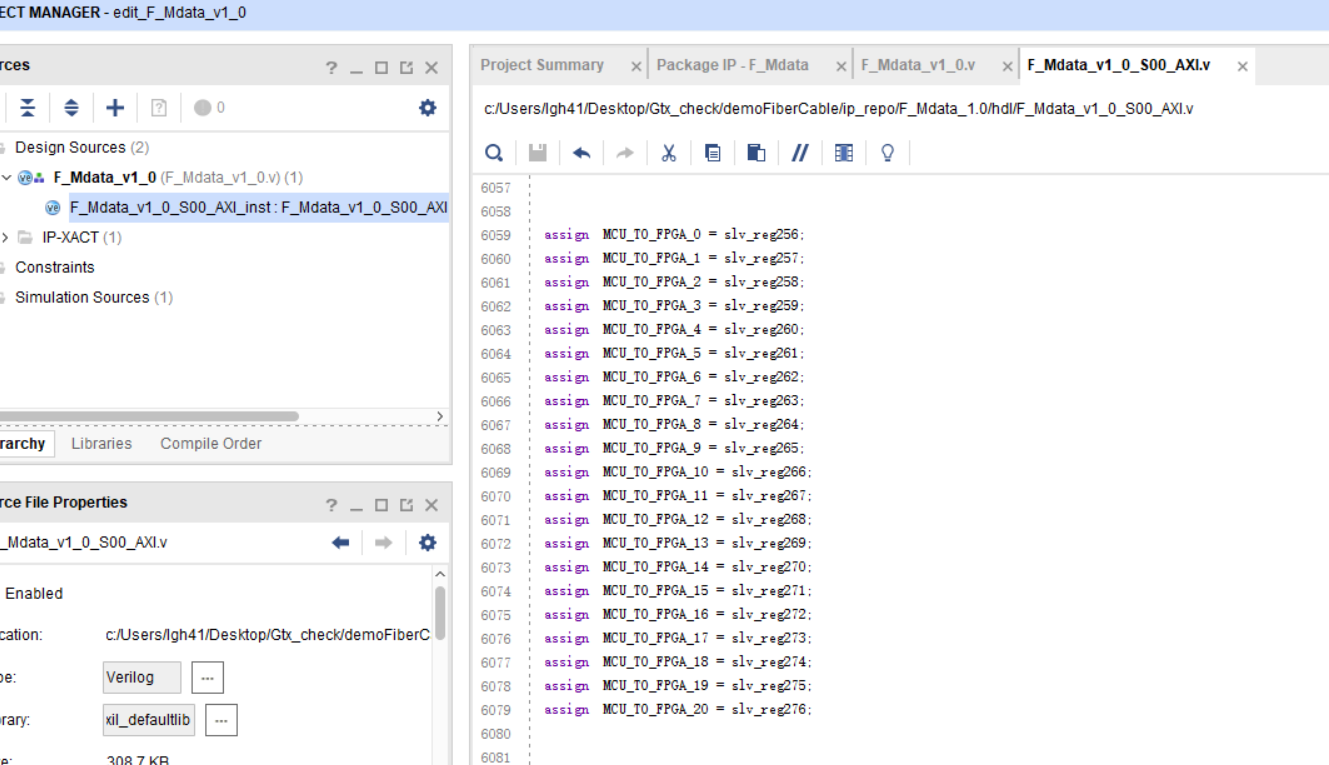

10、分配第5步设定的寄存器数值,一共设定了512个寄存器,设定前256个是FPGA给定到MCU数据,后256个为MCU给定到FPGA数据,寄存器的值为slv_reg0到slv_reg511.故slv_reg0到slv_reg255为输入及FPGA到MCU,后slv_reg256到slv_reg511为输出即MCU到FPGA数据。

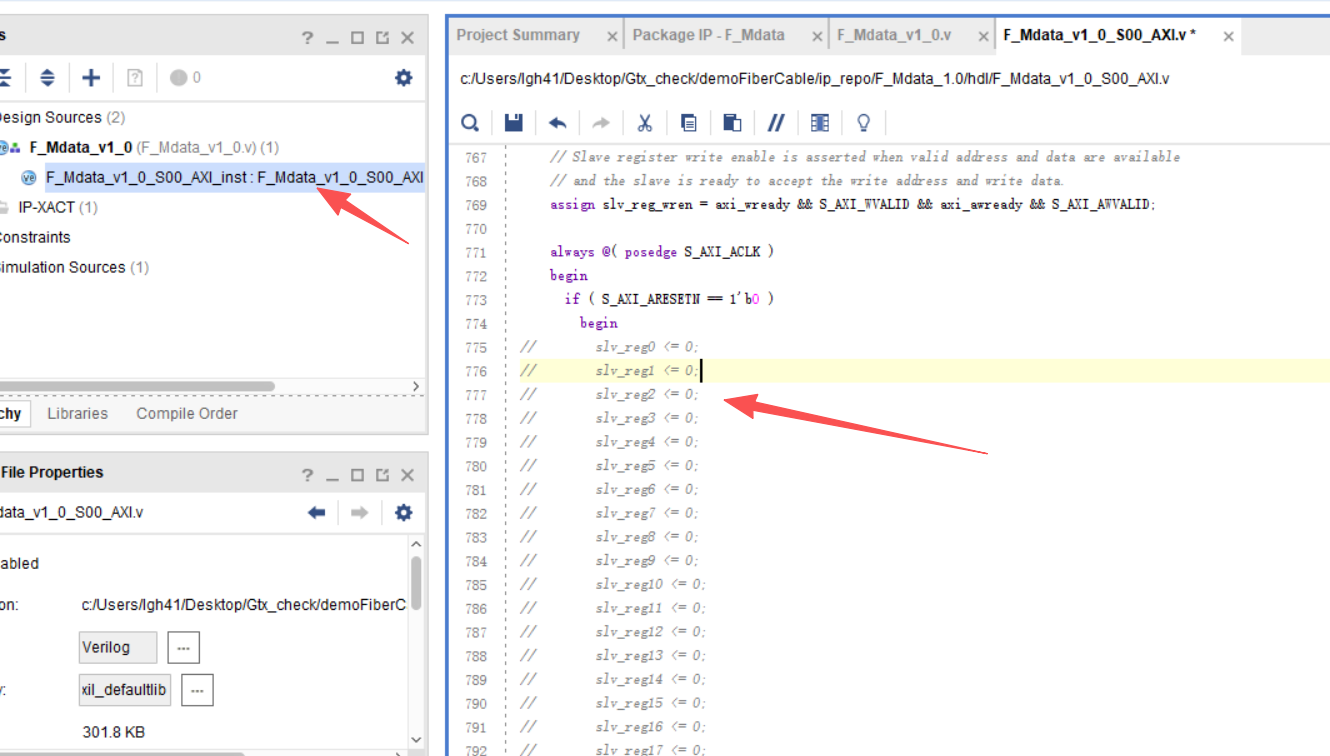

11、屏蔽这个地方的所有寄存器

12、屏蔽slv_reg0到slv_reg255的输入,即FPGA给MCU的数值,防止数值被覆盖

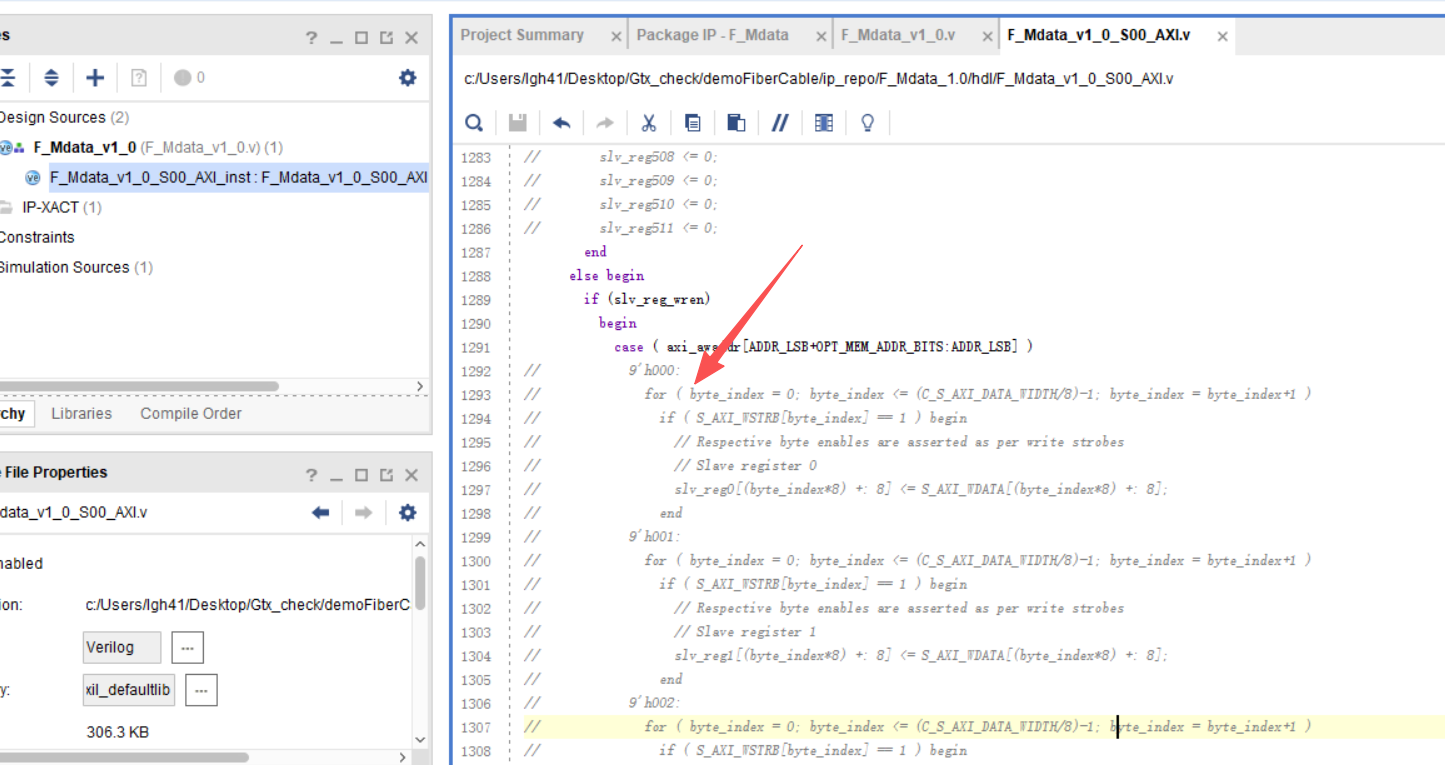

13、屏蔽slv_reg0到slv_reg255的输入,即FPGA给MCU的数值,防止数值被覆盖

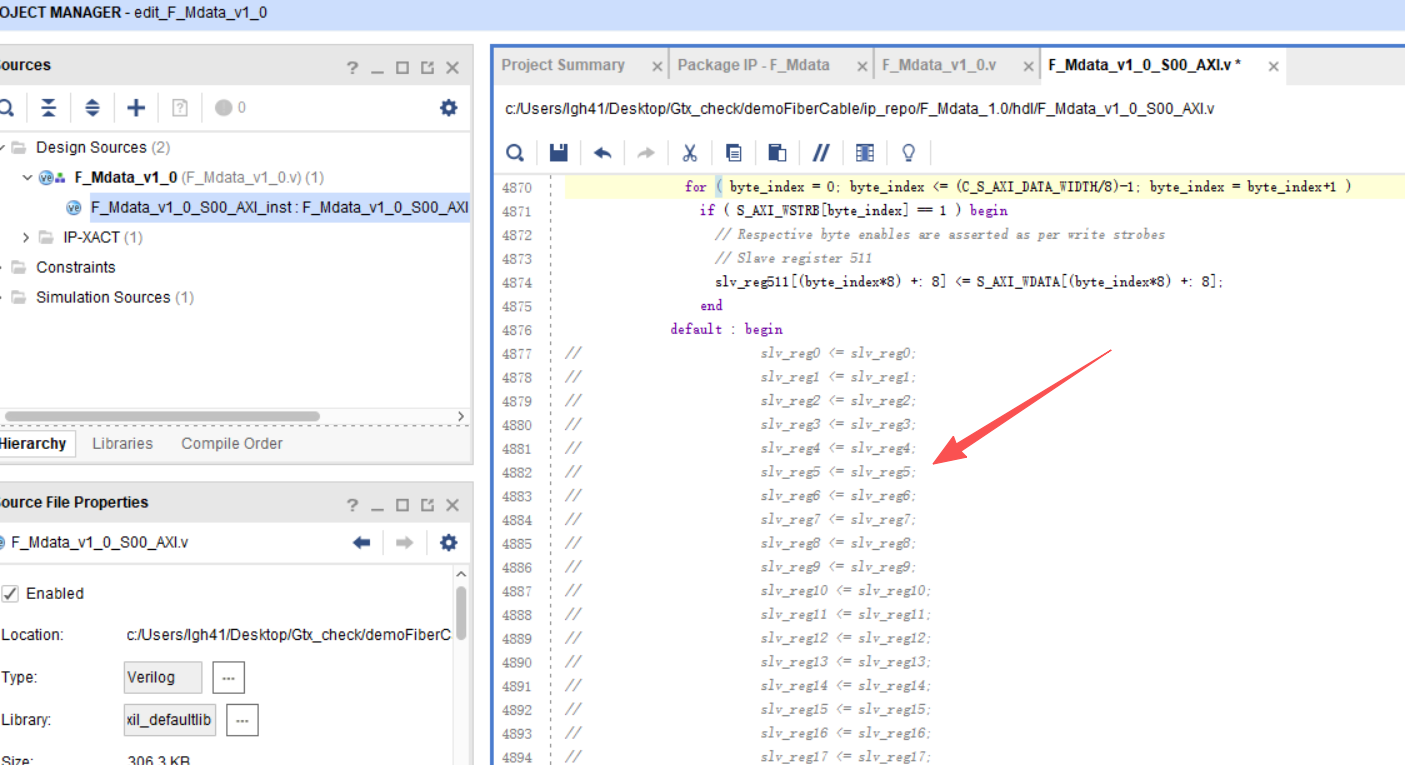

14、屏蔽slv_reg256到slv_reg511的输出,即MCU给FPGA的数值,防止数值被覆盖

15、编程赋值

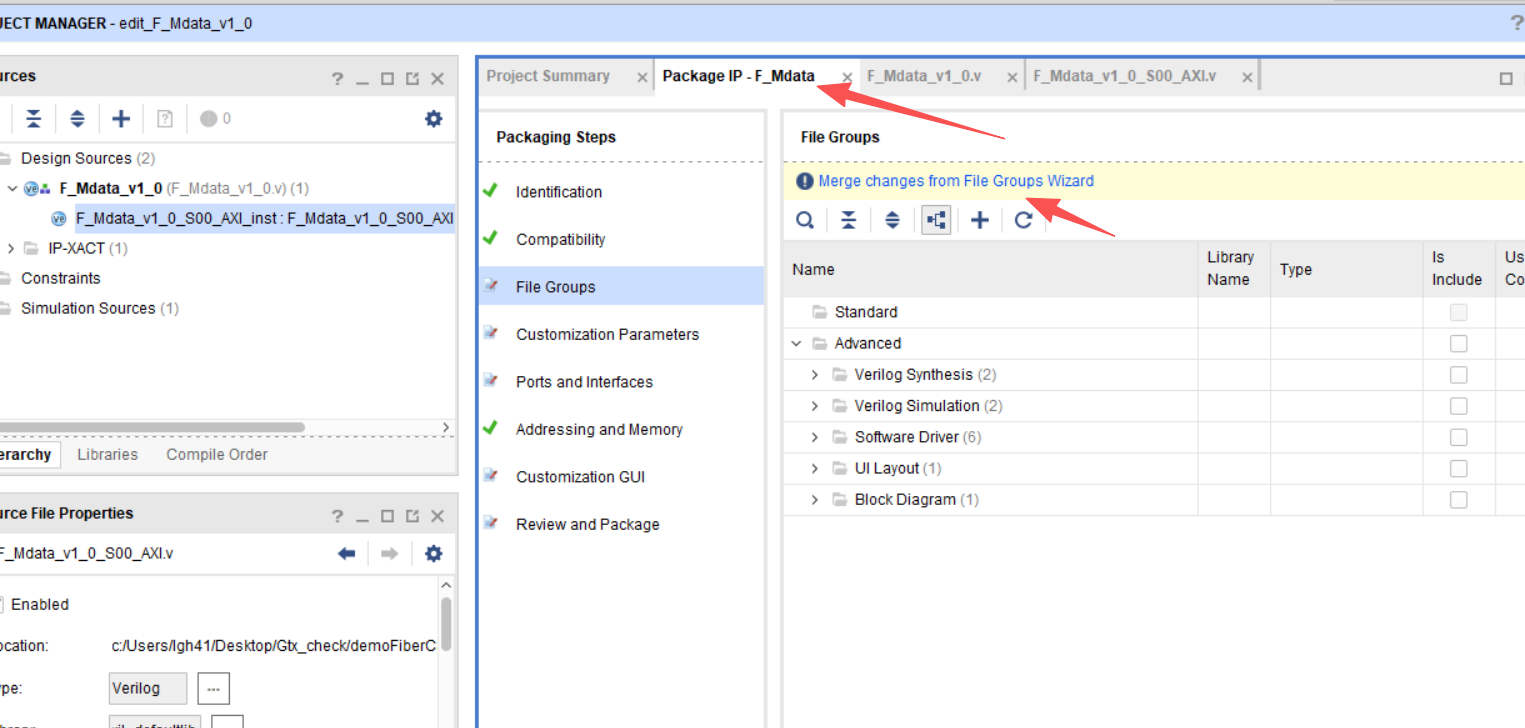

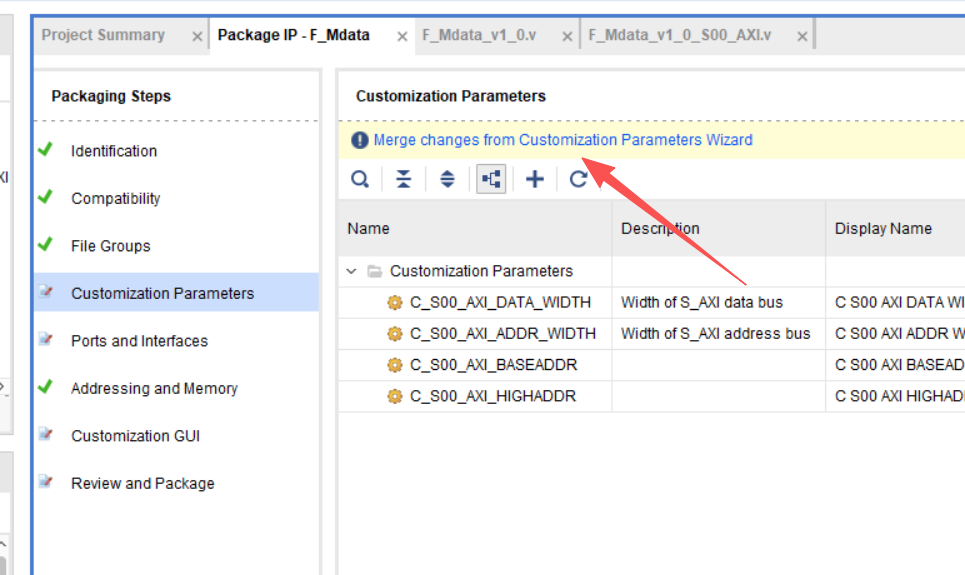

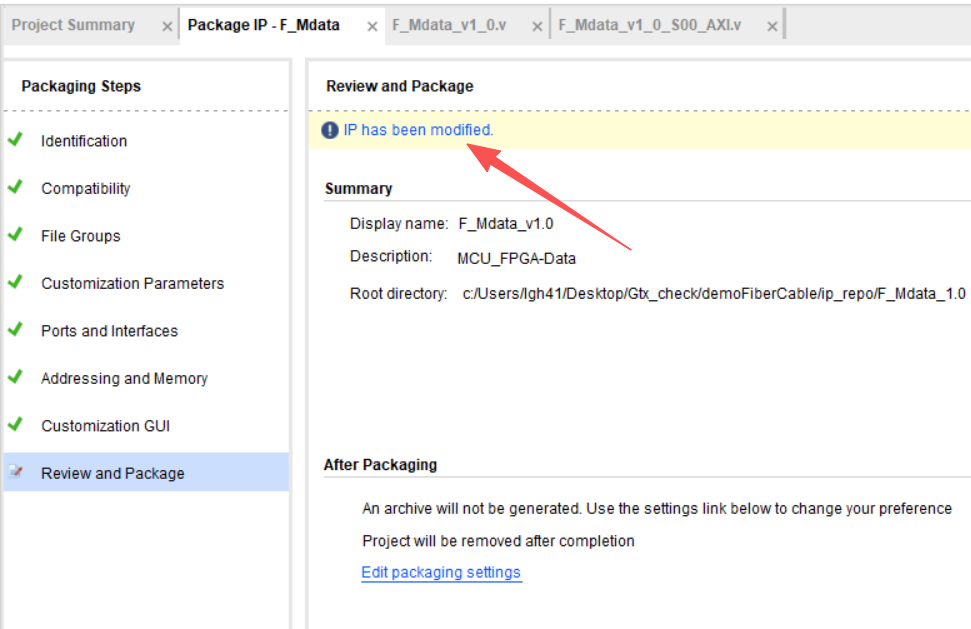

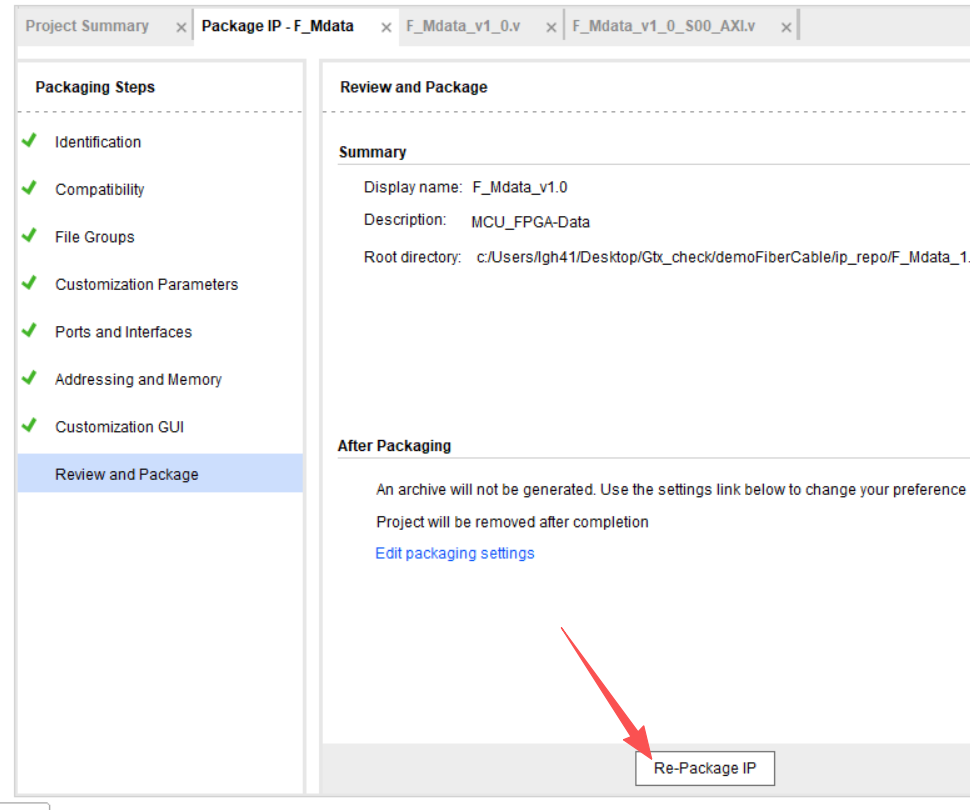

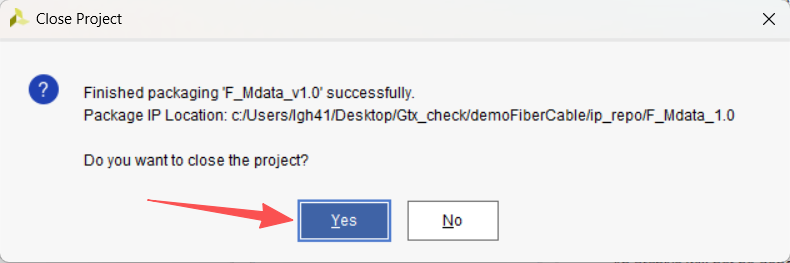

16、IP生成

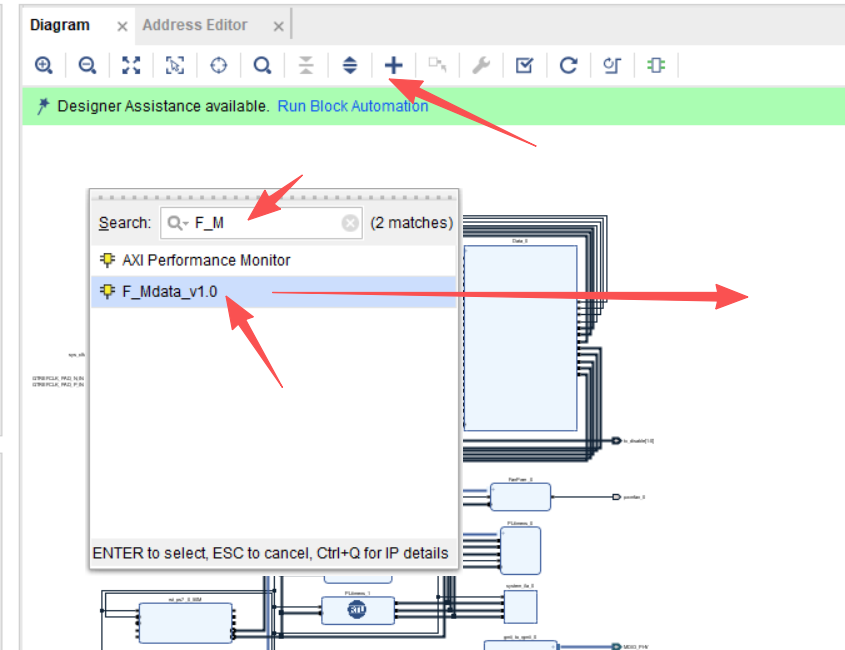

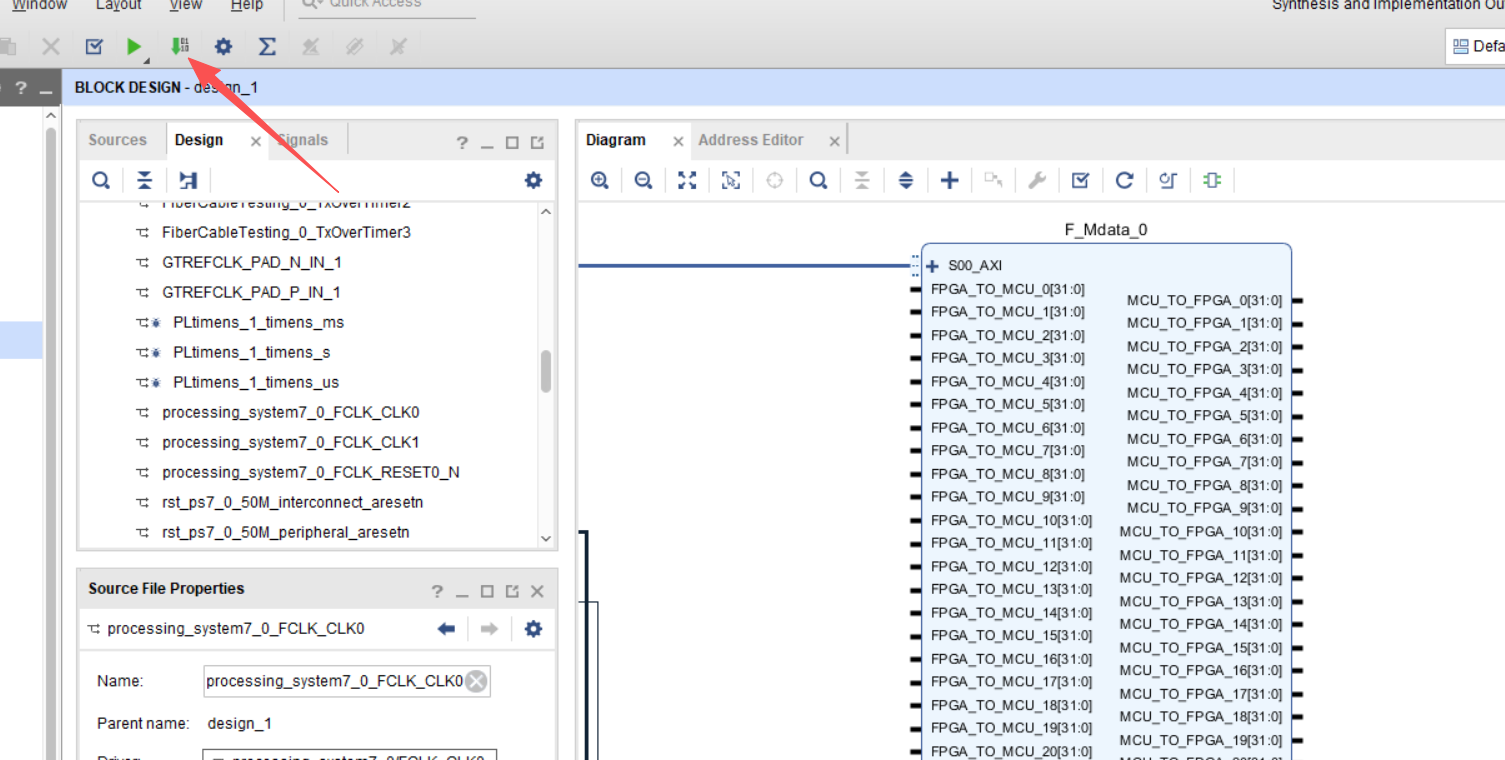

17、调用IP内核

18、编译FPGA

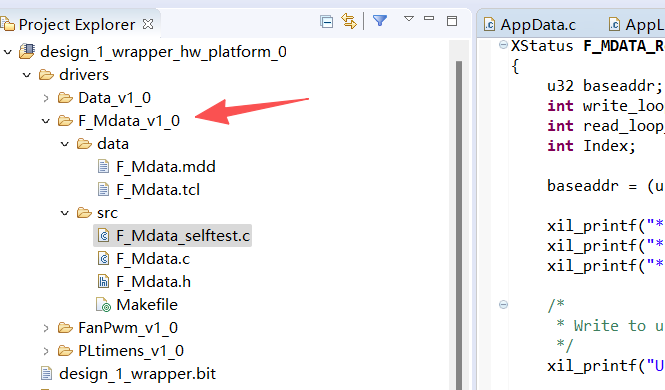

19、生成后打开C代码

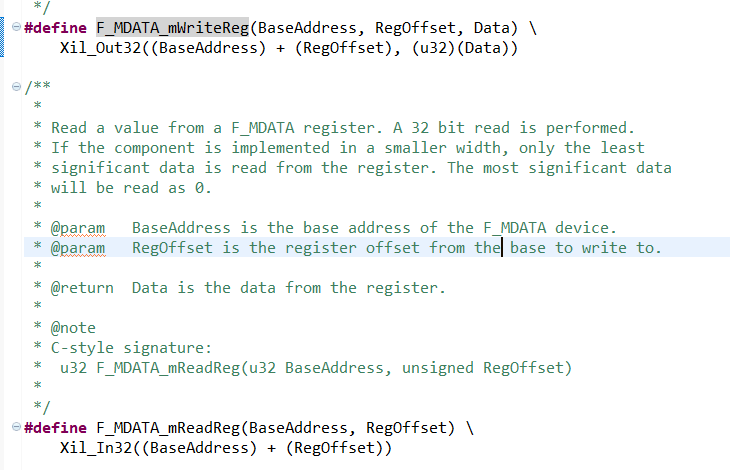

20、MCU到FPGA传数据

F_MDATA_mWriteReg(XPAR_DATA_0_S00_AXI_BASEADDR,F_MDATA_S00_AXI_SLV_REG256_OFFSET,传输的数据32bit);

21、FPGA到MCU传数据

F_MDATA_mReadReg(XPAR_DATA_0_S00_AXI_BASEADDR, F_MDATA_S00_AXI_SLV_REG0_OFFSET)