本文帮助大家快速配置DDS核,并给出相应的仿真代码观察相应的波形。没有多余的讲解,先用起来再说。

DDS核产生正弦波

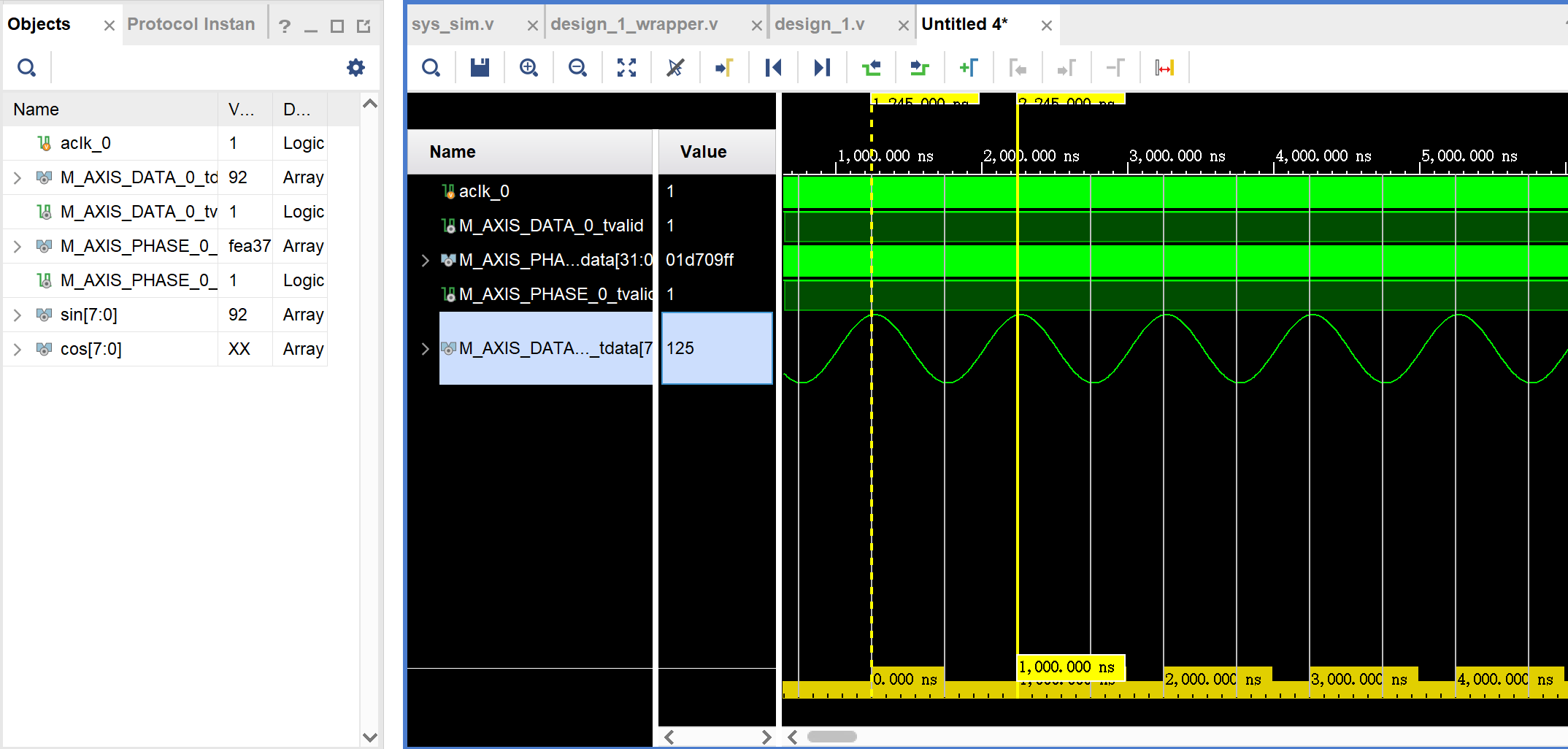

产生的正弦波效果如图:

是一个1M的正弦波

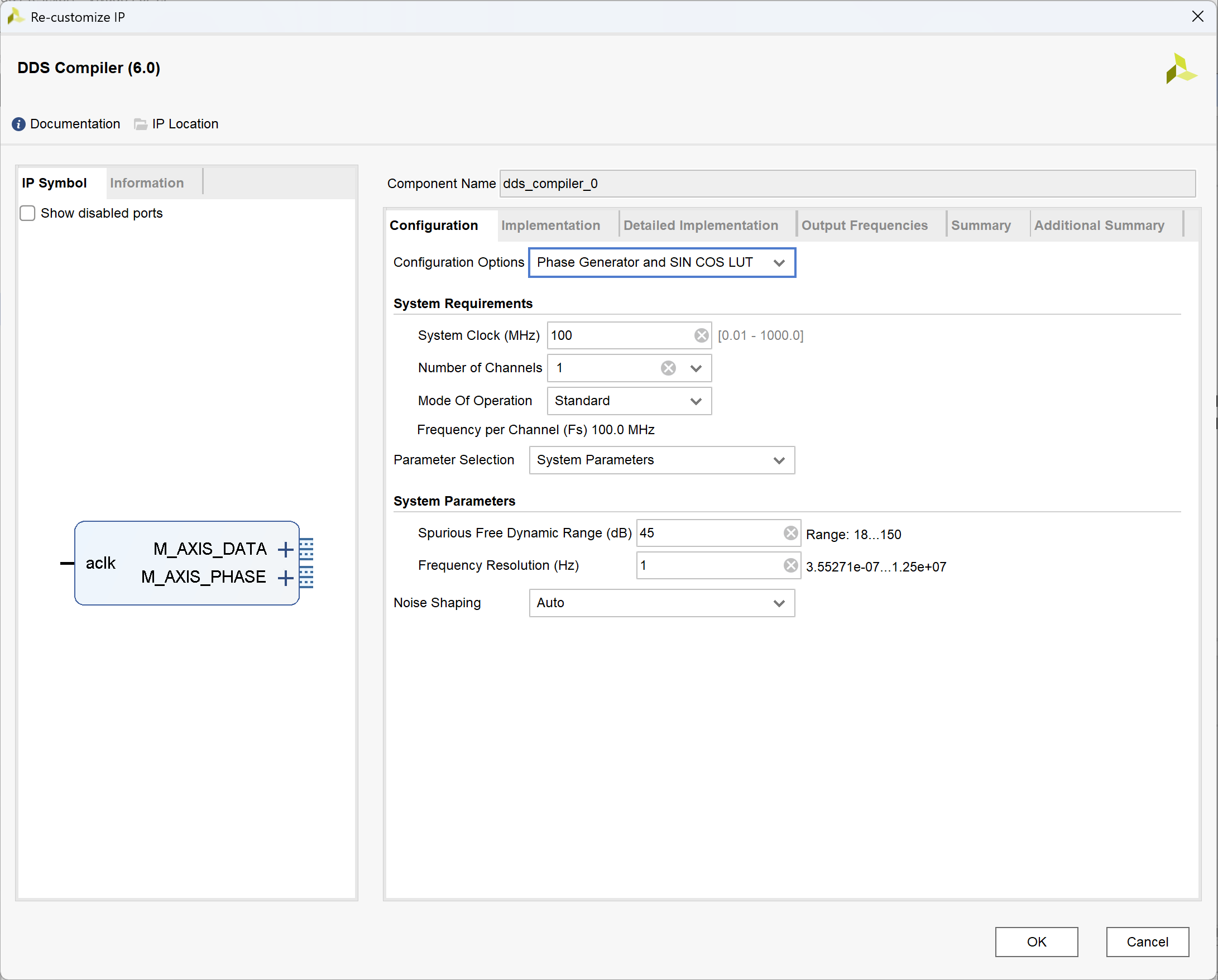

对IP核的配置

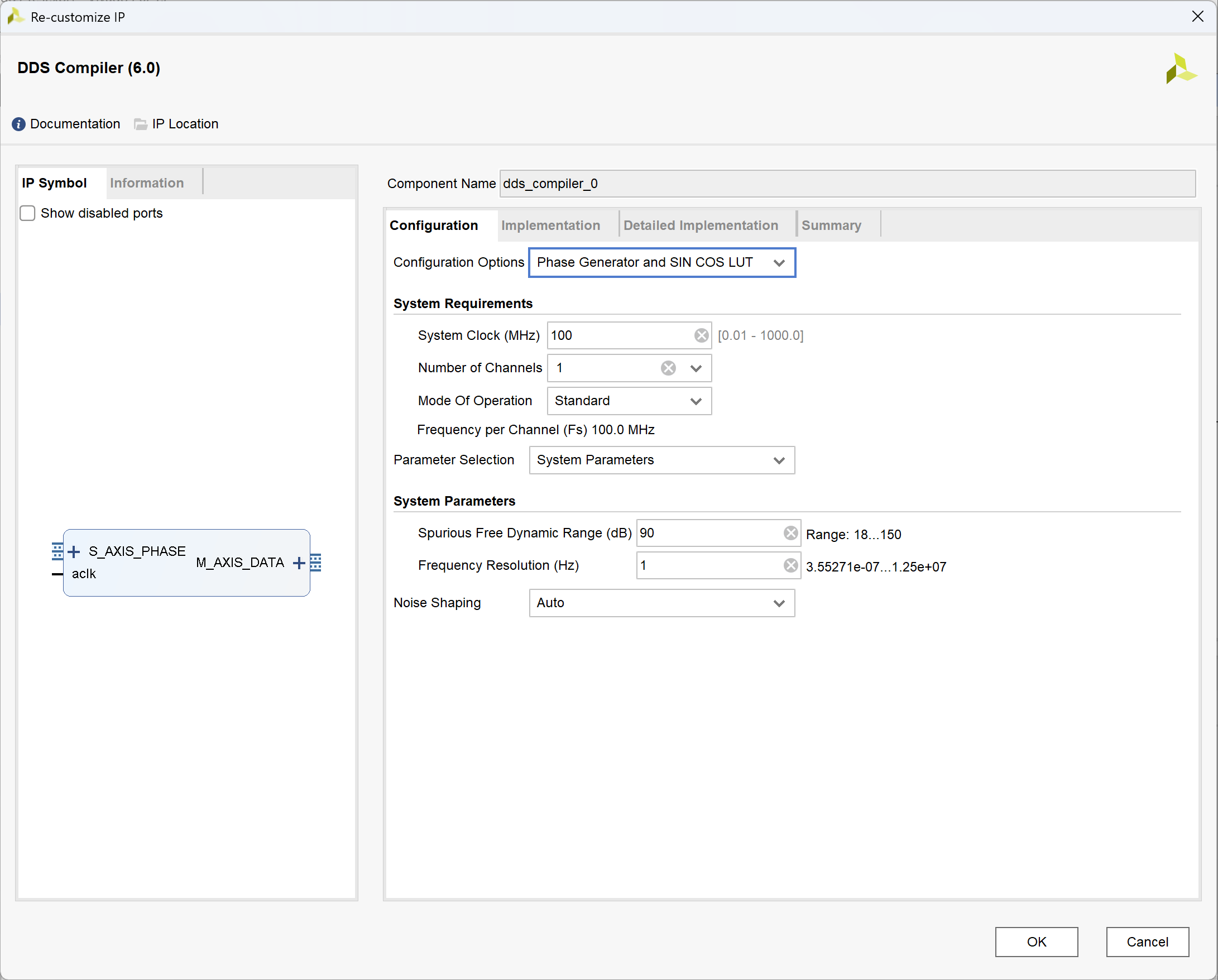

第一页

第二页第三页默认就行

第二页第三页默认就行

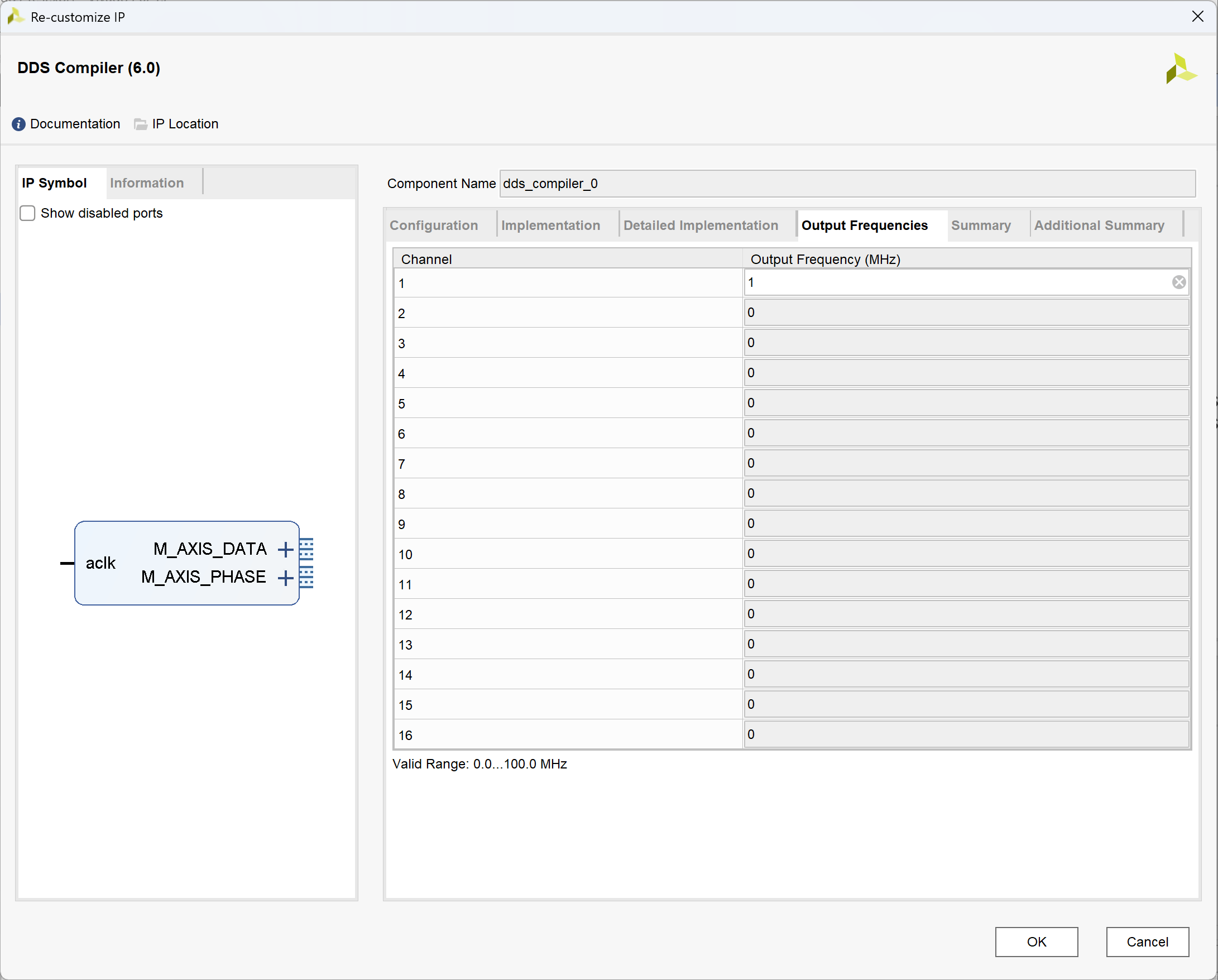

第四页

仿真代码如下:

仿真代码如下:

cpp

module sys_sim(

);

// 定义信号

reg aclk_0;

wire [7:0] M_AXIS_DATA_0_tdata;

wire M_AXIS_DATA_0_tvalid;

wire [31:0] M_AXIS_PHASE_0_tdata;

wire M_AXIS_PHASE_0_tvalid;

wire [7:0] sin;

wire [7:0]cos;

// 实例化被测模块

design_1_wrapper dut (

.M_AXIS_DATA_0_tdata(M_AXIS_DATA_0_tdata),

.M_AXIS_DATA_0_tvalid(M_AXIS_DATA_0_tvalid),

.M_AXIS_PHASE_0_tdata(M_AXIS_PHASE_0_tdata),

.M_AXIS_PHASE_0_tvalid(M_AXIS_PHASE_0_tvalid),

.aclk_0(aclk_0)

);

// 生成100MHz时钟 (周期=10ns)

initial begin

aclk_0 = 0;

forever #5 aclk_0 = ~aclk_0; // 每5ns翻转一次

end

endmodule生成单一频率的正弦波配置确实很简单,可以直接设置自己想要的频率。

DSS核产生线性调频波

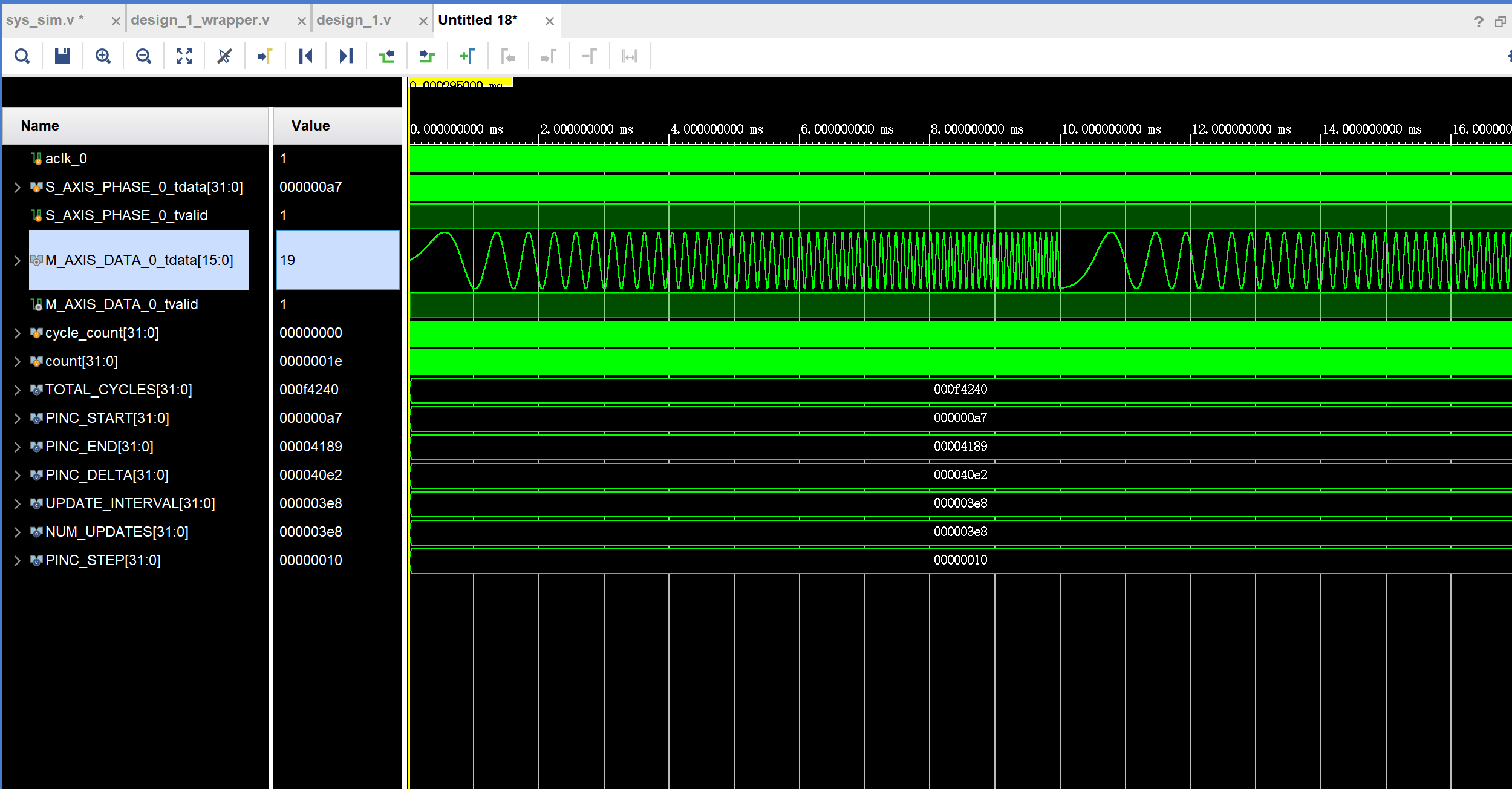

下图为线性调频波的生成效果

不断的产生100HZ到100Khz的线性调频波,周期为10ms。

要生成这样的波形,IP核要做如下的配置

第一页

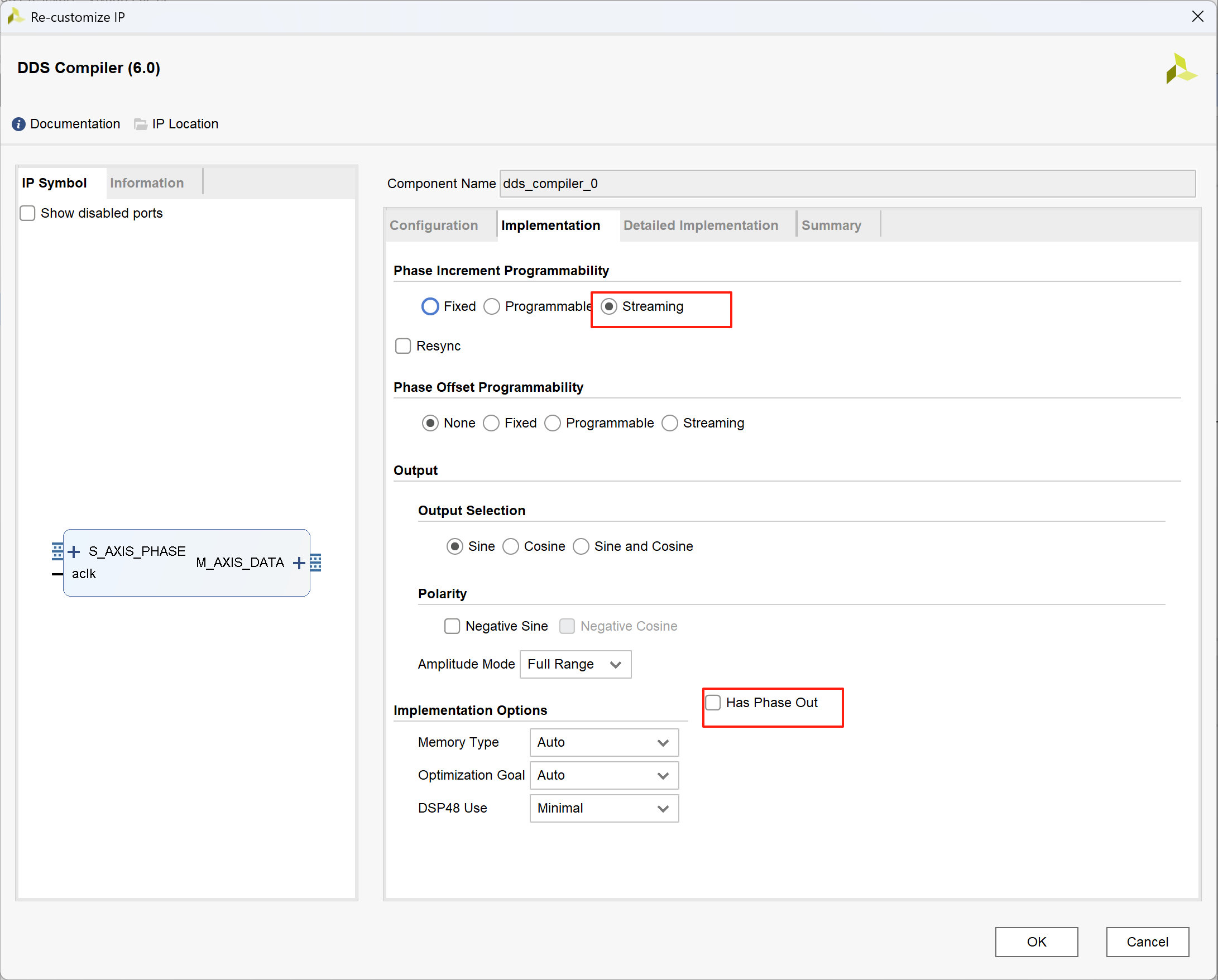

第二页

上面的红框是设置IP核可以在运行过程中修改输出的频率,下面的红框是把相位的输出关掉了。

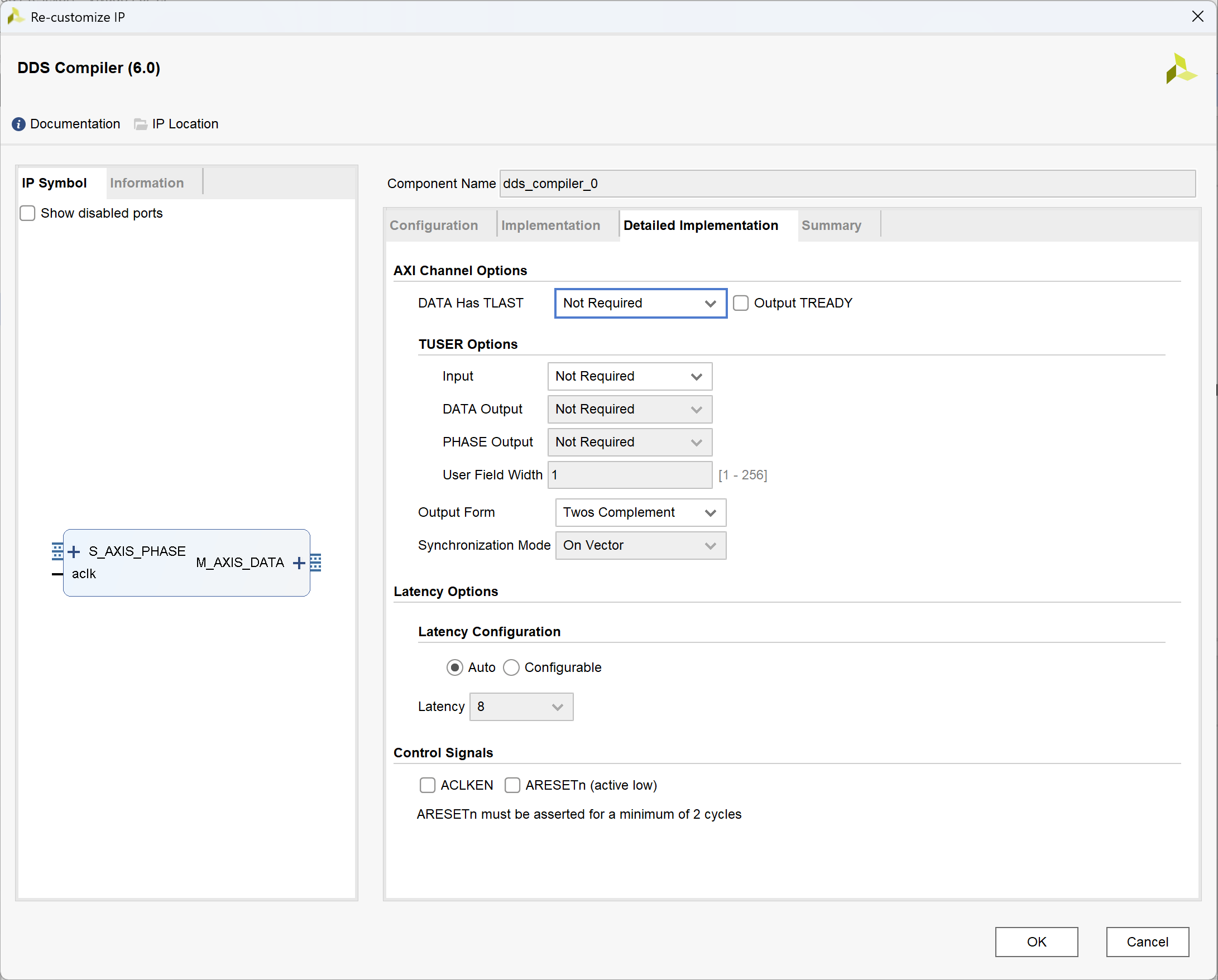

第三页

仿真代码如下:

cpp

module sys_sim(

);

// 定义信号

reg aclk_0;

reg [31:0] S_AXIS_PHASE_0_tdata;

reg S_AXIS_PHASE_0_tvalid;

wire [15:0] M_AXIS_DATA_0_tdata;

wire M_AXIS_DATA_0_tvalid;

// 实例化被测模块

design_1_wrapper dut (

.M_AXIS_DATA_0_tdata(M_AXIS_DATA_0_tdata),

.M_AXIS_DATA_0_tvalid(M_AXIS_DATA_0_tvalid),

.S_AXIS_PHASE_0_tdata(S_AXIS_PHASE_0_tdata),

.S_AXIS_PHASE_0_tvalid(S_AXIS_PHASE_0_tvalid),

.aclk_0(aclk_0)

);

// 开始生成线性调频波

// 参数计算

parameter TOTAL_CYCLES = 1_000_000; // 10ms @ 100MHz 这个参数设置线性调频波的周期

parameter PINC_START = 167; //这个参数设置起始频率,计算公式为 (START_FREQ * (2**相位累加器宽度)) / 时钟频率;

parameter PINC_END = 16777; //这个参数设置结束频率,计算公式为 (END_FREQ * (2**相位累加器宽度)) / 时钟频率;

parameter PINC_DELTA = PINC_END - PINC_START;

// 每K个周期更新一次PINC

parameter UPDATE_INTERVAL = 1000; // 这个参数设置你频率改变的速度,值越小速度越快

parameter NUM_UPDATES = TOTAL_CYCLES / UPDATE_INTERVAL;

parameter PINC_STEP = PINC_DELTA / NUM_UPDATES;

// 生成100MHz时钟 (周期=10ns)

initial begin

S_AXIS_PHASE_0_tdata <= 167;

S_AXIS_PHASE_0_tvalid<=1;

aclk_0 = 0;

forever #5 aclk_0 = ~aclk_0;

end

// 控制逻辑

reg [31:0] cycle_count=0;

reg [31:0] count=0;

always @(posedge aclk_0) begin

if (cycle_count < NUM_UPDATES)begin

if (count ==UPDATE_INTERVAL) begin

// 更新PINC值

count<=1;

cycle_count <= cycle_count + 1;

S_AXIS_PHASE_0_tdata <= S_AXIS_PHASE_0_tdata + PINC_STEP;

end

else

count<=count+1;

end

else begin

S_AXIS_PHASE_0_tdata <= PINC_START;

cycle_count<=0;

end

end

endmodule写在最后

希望这篇文章可以帮大家快速的使用DDS这个IP核,下篇文章我会根据一些实际的需求教大家怎么改参数,大家有什么问题欢迎留言讨论。如果配置还是有困难也可以私聊我发你工程。