14. PWM驱动

14.1. IMX6U的PWM控制器

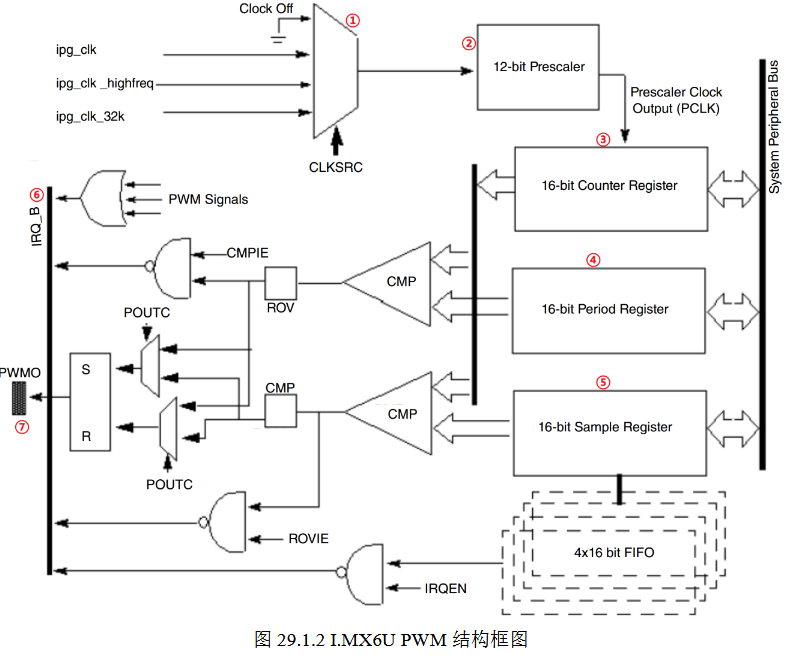

IMX6U的PWM结构如图所示

-

时钟选择与分频:

- 首先,从三个时钟源 (

ipg_clk,ipg_clk_highfreq,ipg_clk_32k) 中选择一个作为PWM模块的基准时钟。 - 这个基准时钟被送入一个12位的预分频器(

Prescaler)进行分频,产生一个更慢的时钟信号,我们称之为PCLK(Prescaler Clock)。这个PCLK是驱动核心计数器的时钟。

- 首先,从三个时钟源 (

-

计数器开始计数:

- 在一个PWM周期的开始,16位计数器从

0x0000开始,在每个PCLK时钟的驱动下递增。 - 同时,PWM的输出引脚

PWMO被置为高电平(这是默认行为,可以配置)。这个动作通常由计数器从周期末尾翻转(Roll-over)到0x0000的事件(ROV)触发。

- 在一个PWM周期的开始,16位计数器从

-

占空比比较:

- 计数器在递增的过程中,它的值会和 16位采样寄存器(

PWMx_PWMSAR) 中的值进行实时比较。 - 当计数器的值 ==

PWMx_PWMSAR的值 时,比较器(CMP)会产生一个匹配信号。 - 这个匹配信号会触发PWM输出引脚 PWMO 变为低电平。

- 计数器在递增的过程中,它的值会和 16位采样寄存器(

-

周期结束与循环:

- 计数器继续递增,直到它的值与 16位周期寄存器(

PWMx_PWMPR) 中的值相等。 - 当计数器的值 ==

PWMx_PWMPR的值 时,标志着当前PWM周期的结束。 - 在下一个PCLK时钟到来时,计数器会翻转回 0x0000,同时PWMO输出再次被置为高电平,开始一个新的PWM周期。

- 计数器继续递增,直到它的值与 16位周期寄存器(

-

简单来说,整个过程就是:

周期开始 -> 输出拉高 -> 计数器开始从0计数 -> 计数到采样值 -> 输出拉低 -> 计数器继续计数 -> 计数到周期值 -> 周期结束 -> 计数器归零,重复上述过程。

-

采样FIFO

- 采样FIFO用于存储多个采样值,允许在多个PWM周期内使用不同的占空比。

- 当计数器达到采样寄存器值(下一个PWM周期开始)时,FIFO中的下一个采样值会被加载到采样寄存器中,准备在下一个周期使用。

- 最多有4个采样值可以存储在FIFO中

- FIFO满时,新的采样值将被丢弃

- 可以在寄存器

PWM1_PWMCR的FWM(bit27:26)设置FIFO水位:即设置 FIFO 空余位置为多少的时候表示 FIFO 为空 - 当 FIFO 空余位置 <= 水位时,寄存器

PWM1_PWMSR的FE(bit3)置1,若寄存器PWM1_PWMIR的FIE(bit0)已经置1(设置了FIFO中断),那么就会触发中断,一般使用DMA不断向FIFO中写入采样值,减少CPU的负担

14.2. 频率与占空比的设置

-

频率设置

- 频率 = PCLK / (周期寄存器值(

PWMx_PWMPR) + 1) - 其中,PCLK = 基准时钟 / (预分频器值(

Prescaler) + 1) - 因此,频率 = 基准时钟 / ((预分频器值(

Prescaler) + 1) * (周期寄存器值(PWMx_PWMPR) + 1))

- 频率 = PCLK / (周期寄存器值(

-

占空比设置

- 占空比 = (采样寄存器值(

PWMx_PWMSAR) + 1) / (周期寄存器值(PWMx_PWMPR) + 1) * 100%

- 占空比 = (采样寄存器值(

14.3. 核心寄存器

查看手册29.1节