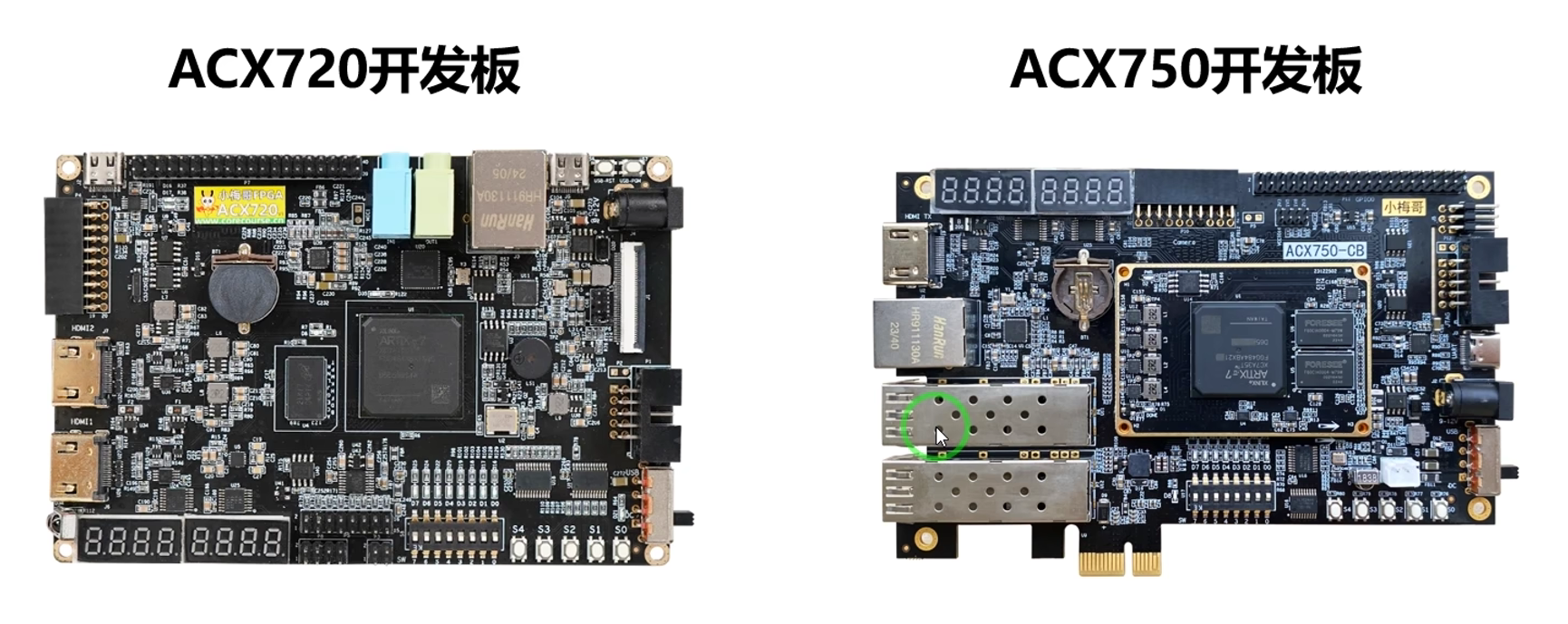

本次实验支持ACX720kaifaban和ACX750开发板,此处以ACX720为例。

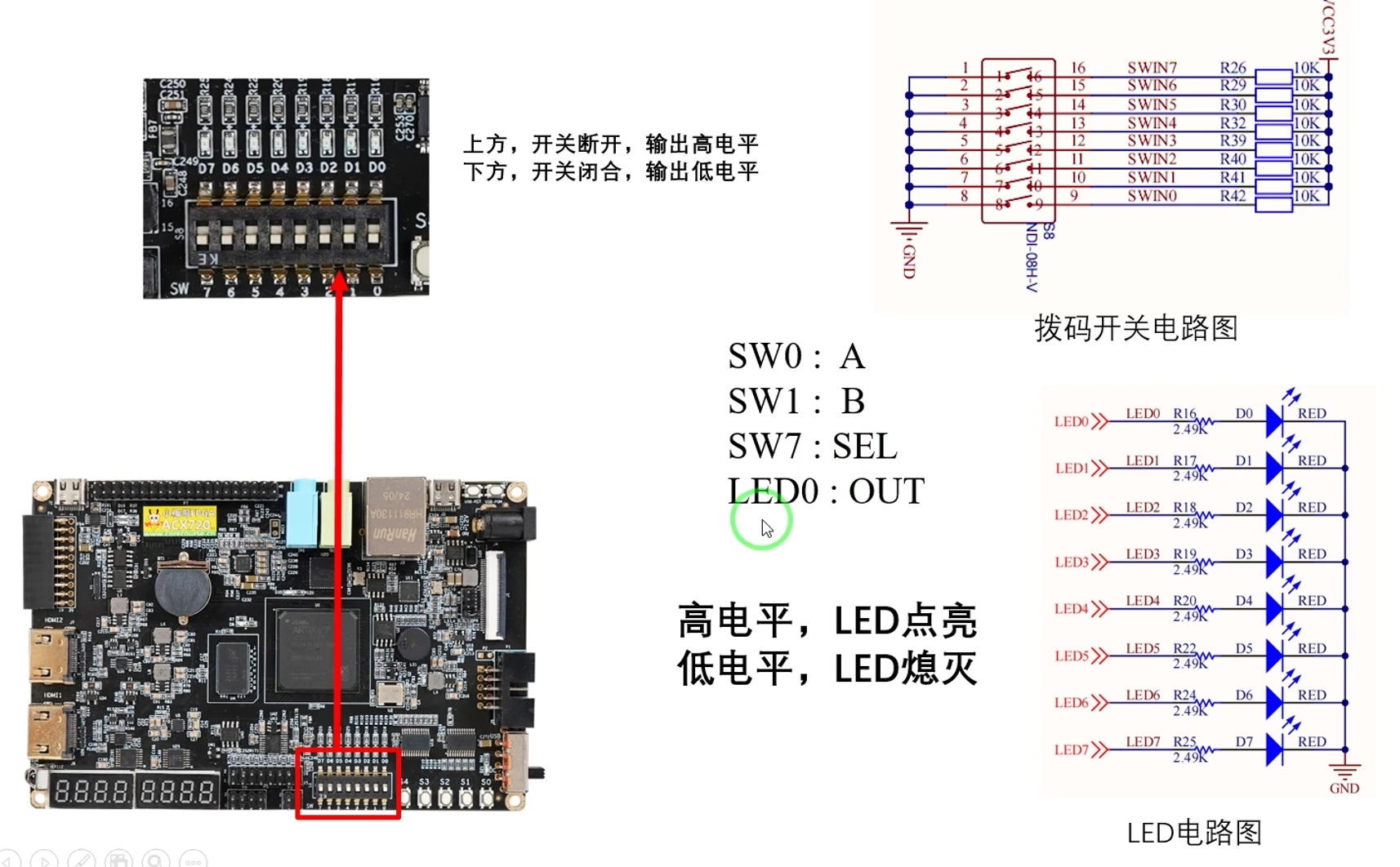

本设计共有三个输入端口,分别为A B SEL,需要在程序运行的过程中去手动修改这三个端口的值,该场景适合开发板上的拨码开关电路。

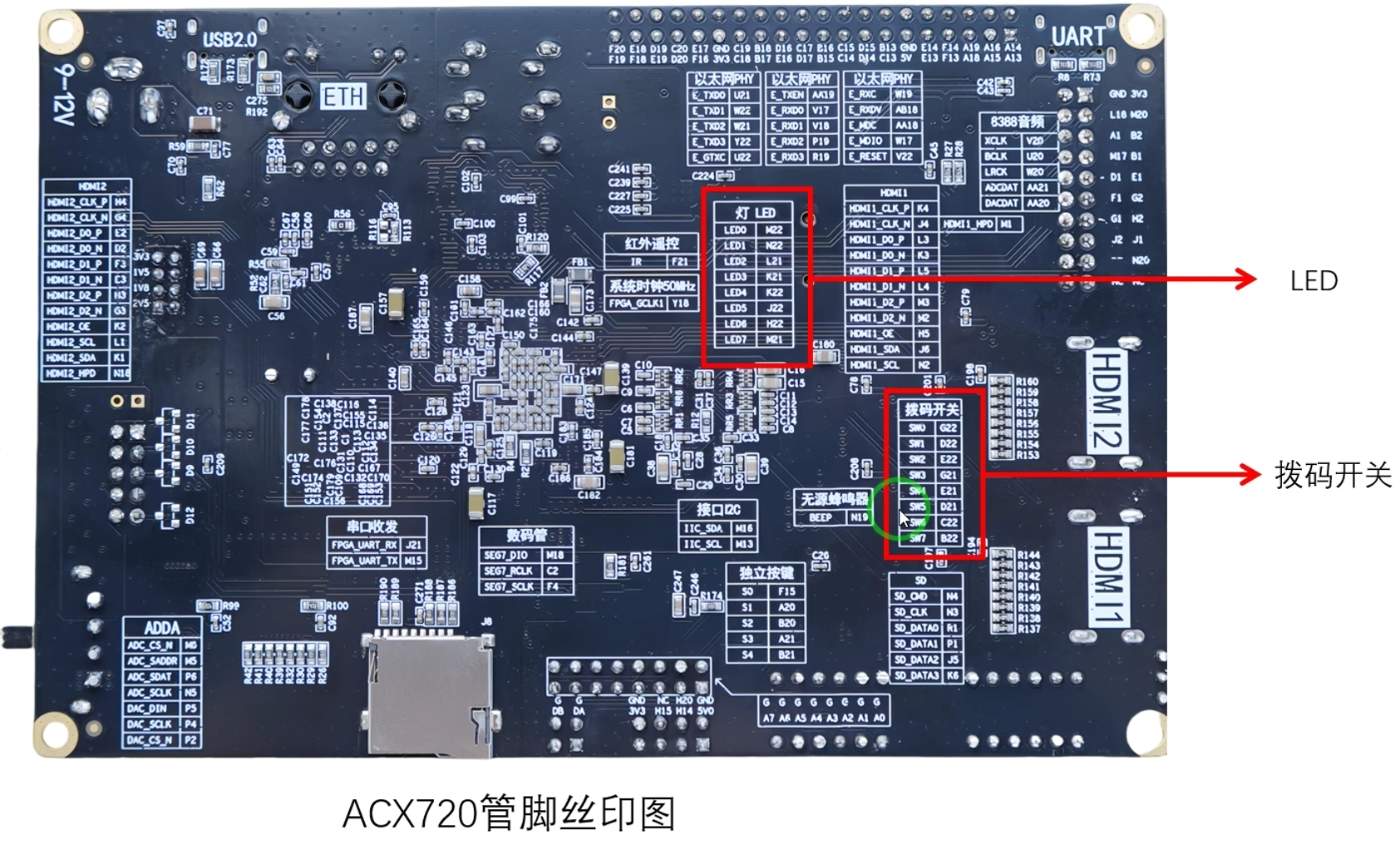

ACX720开发板上的拨码开关作为输入,输出端口OUT可以使用LED灯来指示该端口的电平状态。

ACX720上有八个拨码开关和八个LED灯。

开关断开时,对应的FPGA管脚会被上拉电阻拉到高电平,开关闭合时,FPGA管脚接地变为低电平。

FPGA管脚输出高电平对应的LED灯亮,输出低电平,对应的LED灯灭。

从硬件电路中挑选几个开关和LED灯与设计中的端口进行对应

(SW通常对应拨码开关,S通常对应按键)

确定好物理硬件和设计的二选一多路器的端口关系后,需要将这种对应关系告诉Vivado软件,只有这样才能将该信号端口通过内部布局布线的方式连接到对应的FPGA管脚上,该操作通常称为管脚约束(或管脚分配、管脚绑定)。

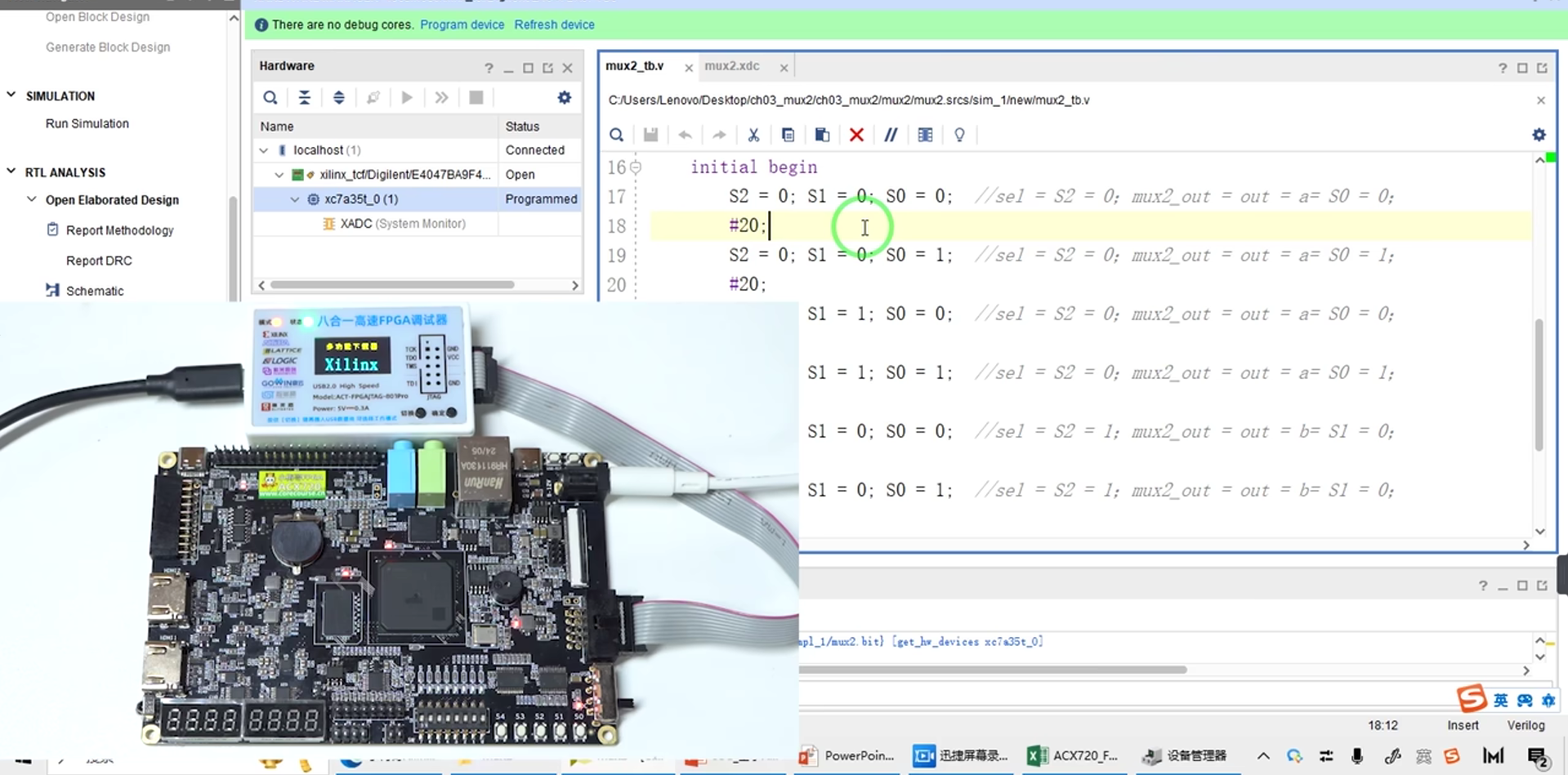

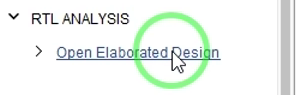

1.打开设计

点击Open Elaborated Design打开设计

点击OK

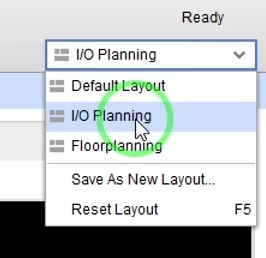

打开后右上角默认是I/O Planning,软件会切换到管脚分配的页面

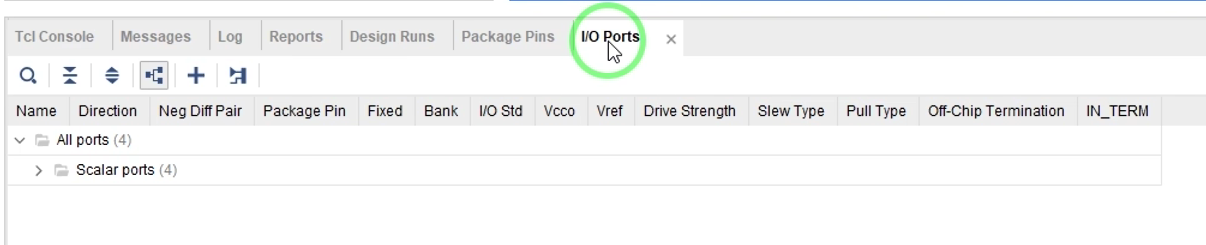

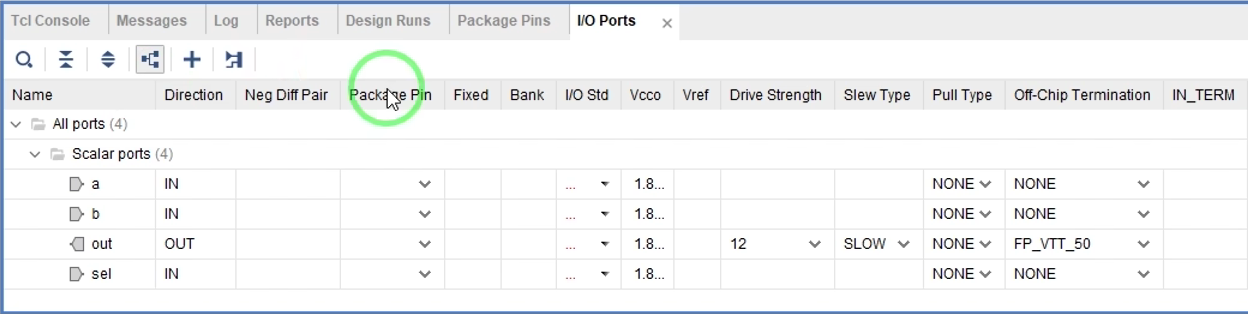

I/O Ports页面是可以进行管脚绑定的图形界面

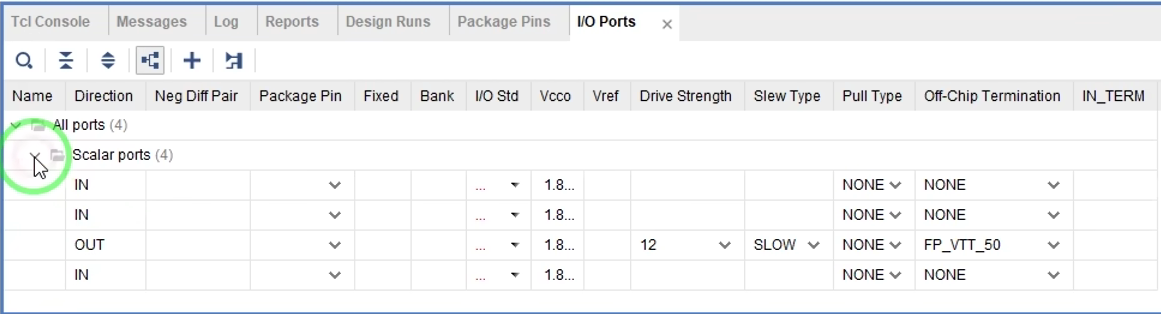

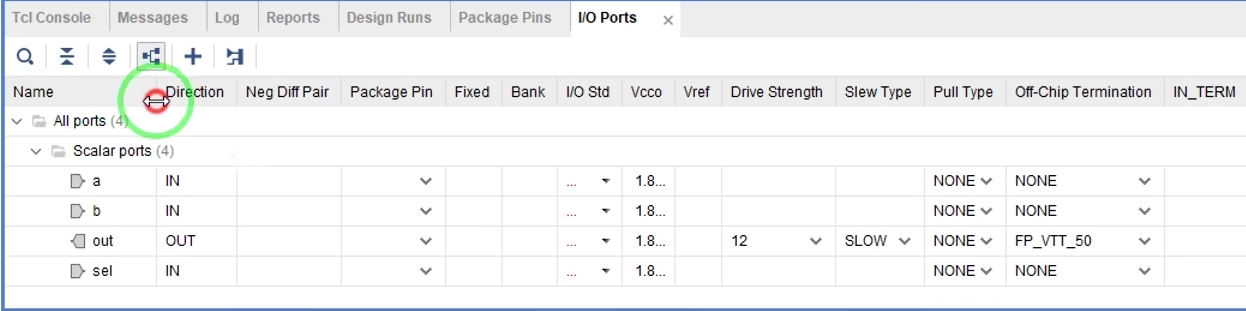

All ports是所有端口,展开Scalar ports即可看到四个端口

手动将Name栏拉宽就可以看到端口名称

2.进行管脚输入

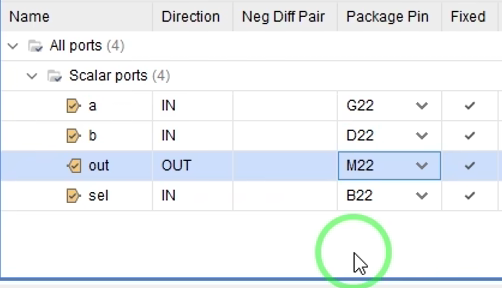

要根据具体的硬件开发板管脚的对应关系来选择对应的FPGA管脚,填入每个信号栏后面的Package Pin

如何查阅管脚信息?

具体每个功能对应哪个管脚有很多方式可以获取信息,比如查看原理图、查看用户手册或查看引脚信息表,对于该开发板最简单的方式是通过开发板背面的丝印进行分配

另一种查阅方法:扫描该二维码或者打开浏览器进入网站www.corecourse.cn

点击所以开发板模块下载资料

找到ACX720

第一个就是资料下载链接

点击网盘资料链接

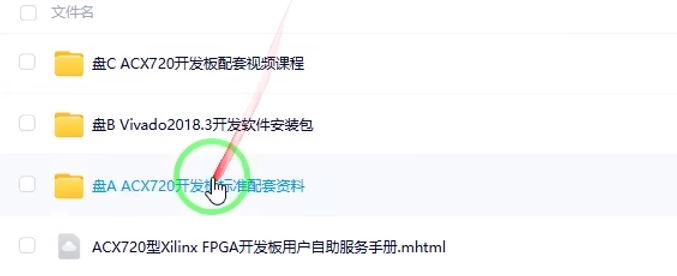

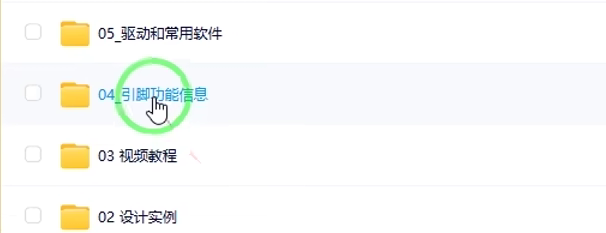

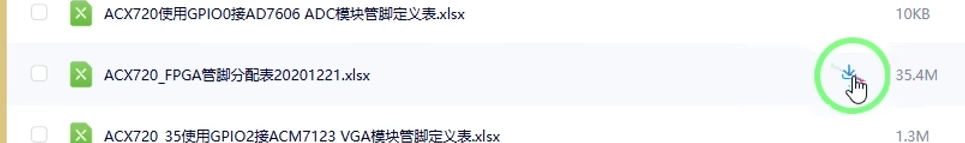

找到A盘→04引脚功能信息

只需要下载Excel表格即可

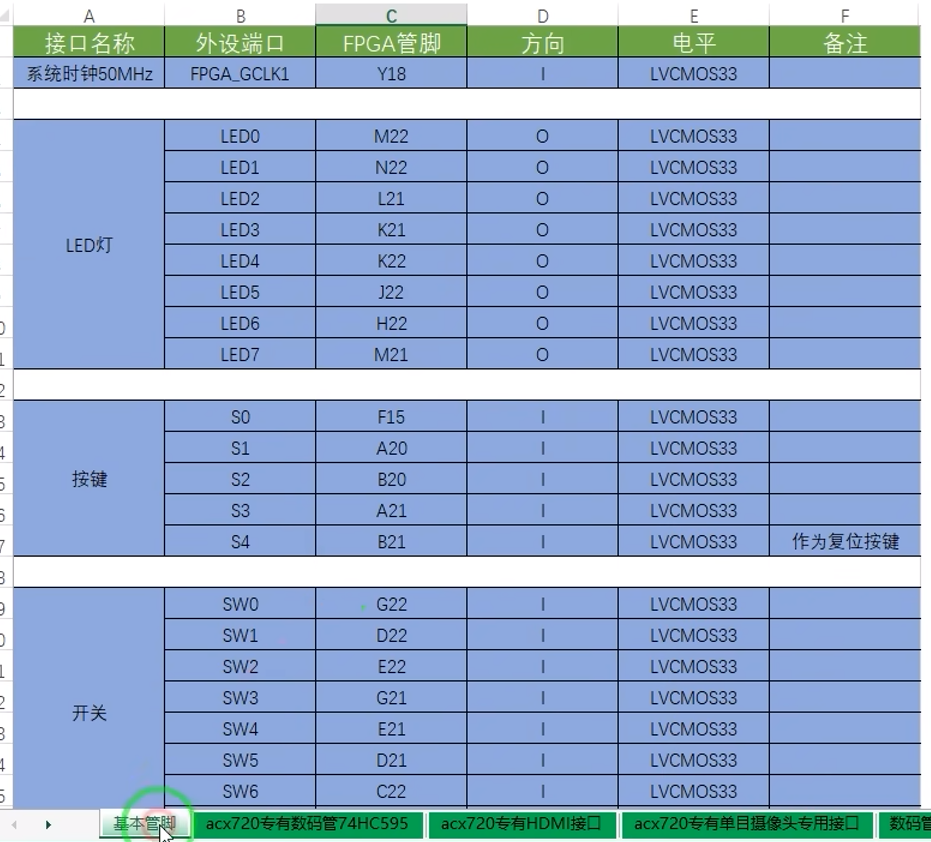

在基本管脚处就可以看到管脚对应关系

进行管脚输入(直接输入+回车即可)

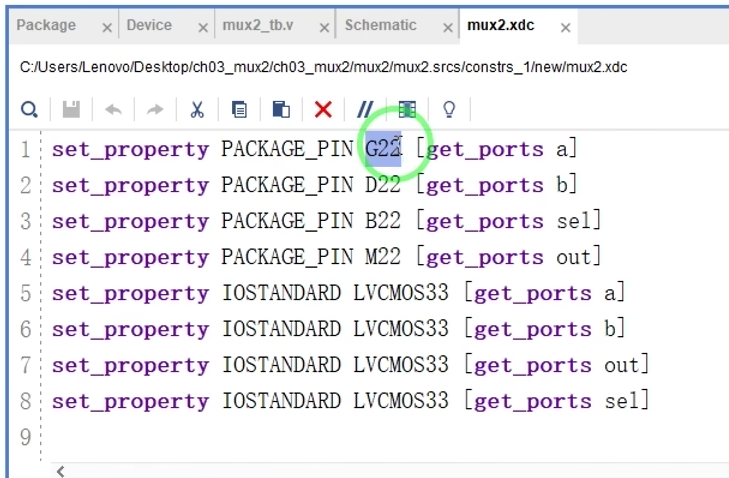

a→SW0→G22

b→SW1→D22

sel→SW7→B22

out→LED0→M22

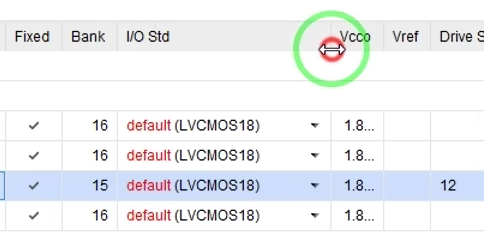

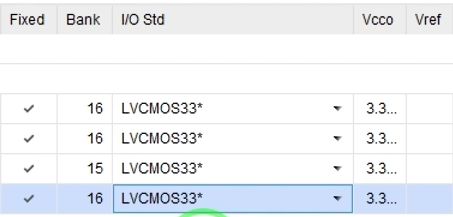

位置确定完之后还需要修改信号的管脚电平,拉宽I/O Std(I/O电平标准)

默认是1.8V的CMOS电平标准,需要将其修改为电路板上实际使用的电平标准 LVCMOS33

3.生成xdc文件

需要将这些管脚绑定的信息保存到一个软件能够识别的约束文件中,xdc格式

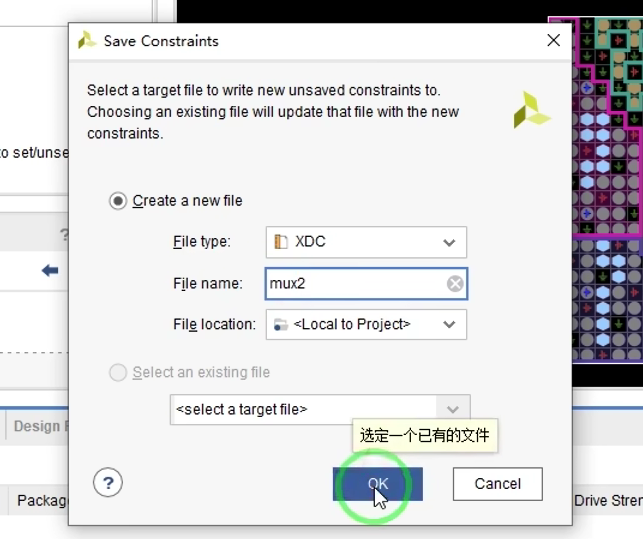

按组合键Ctrl+S会弹出一个保存对话框,输入要保存的文件名称

点击OK后自动生成了一个文件

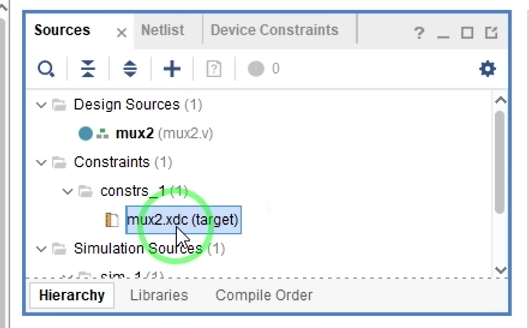

在Sources中可找到

实际上上述步骤,在图形界面一个个的输入管脚修改电平只是一个过程,目的是为了生成一个xdc的文件

双击该文件打开查看其内容,以文本的形式描述了每一个功能对应的FPGA管脚以及所使用的电平标准

set_property是设置属性的,具体的属性值,PACKAGE_PIN是封装对应G22

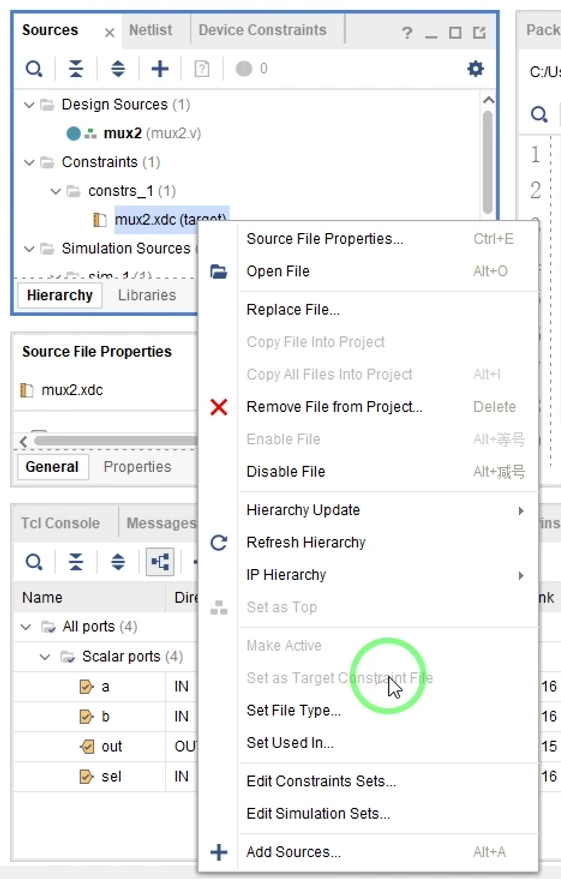

在文件名后面有target,表示该文件是当前工程所使用的目标约束文件,工程会根据这个文件中的内容将各个端口与FPGA的具体管脚在布局布线时一一绑定,当工程复杂时可能会有多个目标约束文件,右键选择Set as Target Constraint File

4.生成编程文件

产生能够下载到FPGA中的编程文件,赛恩斯FPGA使用的编程文件后缀是bit,俗称bit流

点击Generate Bitstream

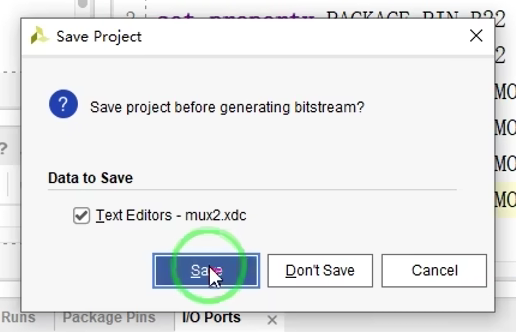

点击Save

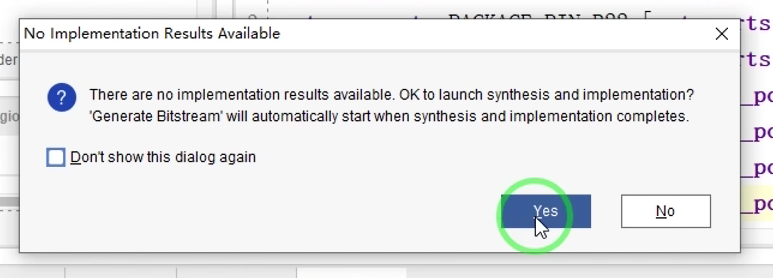

点击Yes

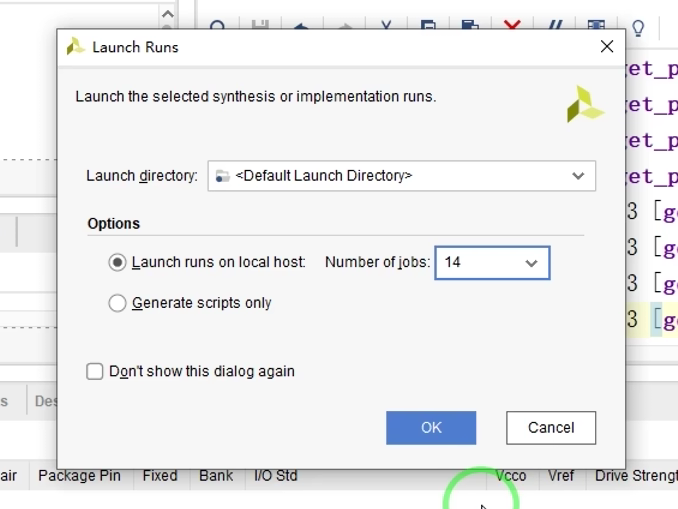

Number of jobs是询问使用第三个线程,或多少个CPU核进行编译,jobs代表CPU核心,理论上用的核心数越多编译速度越快,不同电脑可选择的CPU核的数不同,是因为每个电脑所使用的CPU核心数量不一样。

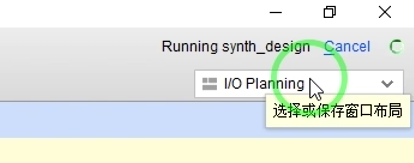

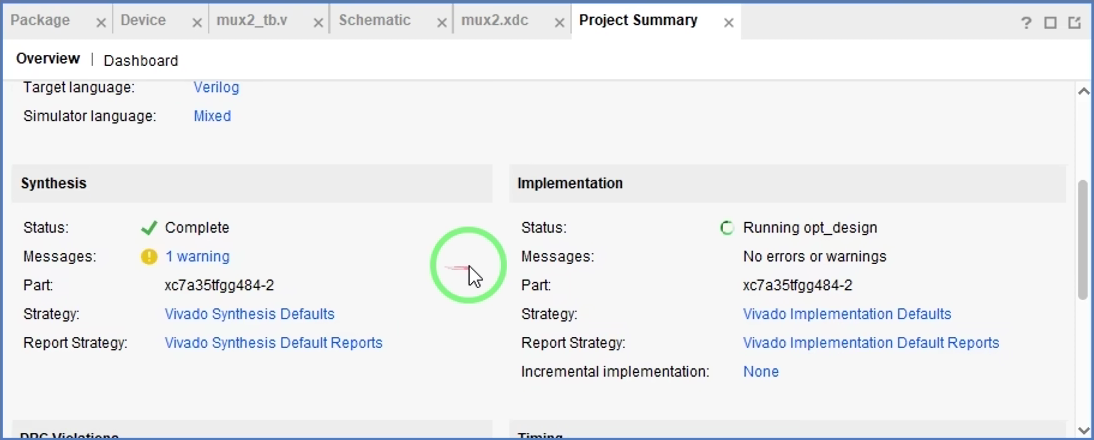

点击OK后进入软件进入了编译并生成编程文件的过程,软件的右上角会显示编译过程

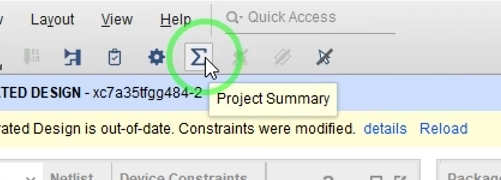

若想看到编译的详细过程,可以直接点Project Summary

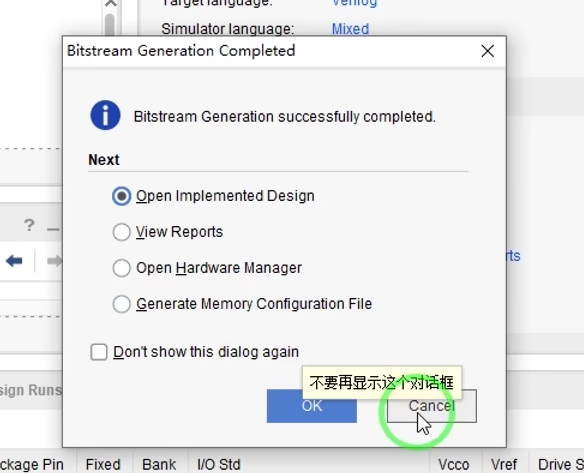

编译完成后会出现很多选项

第一个可以打开已经实现完成的设计,可以查看时序、拓扑图、底层的电路图、结构图等

第二个可以打开设计编译报告的窗口,查看编译报告中用了多少资源,有无报错、警告等

第三个可以打开硬件管理器,可以连接开发板并进行下载和调试,将编译好的bit文件下载到板子中进行板机运行

第四个可以生成配置内存文件

这里直接点Cancel即可

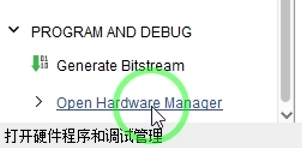

5.将编程文件下载到开发板中

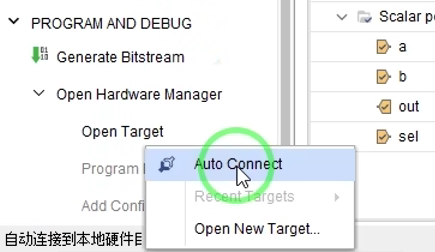

在软件的左下角点击Open Hardware Manager

找到Auto Connect

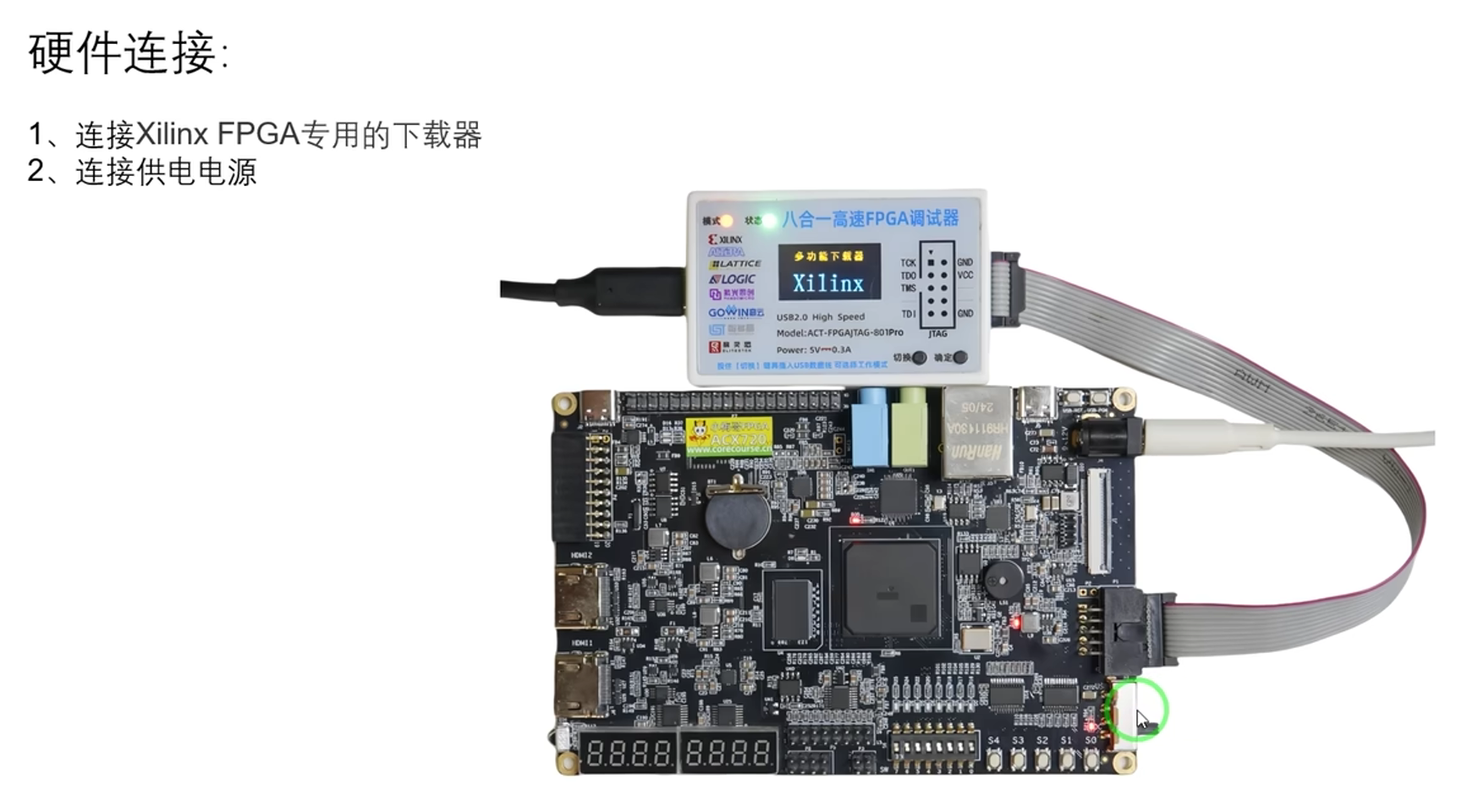

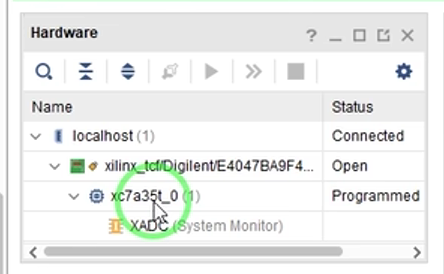

硬件连接

1.使用Xilinx FPGA专用下载器将电脑和开发板进行连接

2.连接供电电源

3.右下角的开关要确保拨至DC供电端(三段开关,上面是使用USB接口供电,中间是关电,下面是使用直流接口供电)

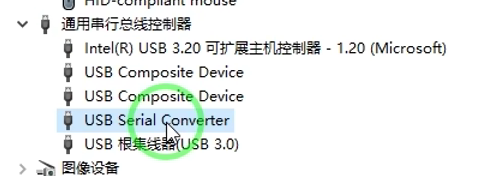

4.确保下载器的驱动已经安装完成

打开设备管理器,在通用串行设备中寻找Serial Converter的设备

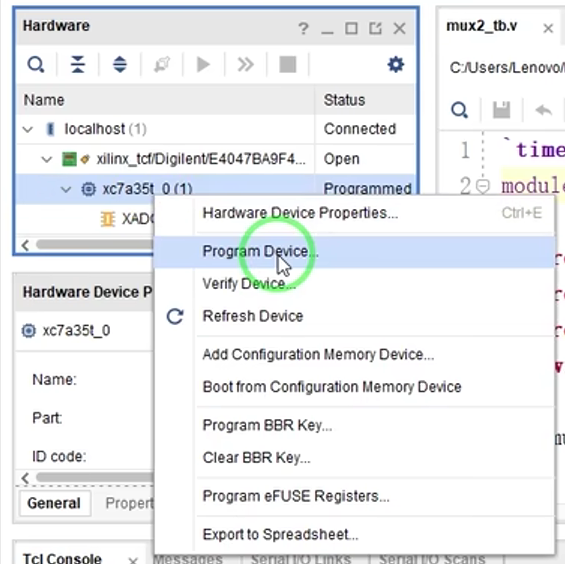

6.进行编程

右键选中芯片,点击Program Device

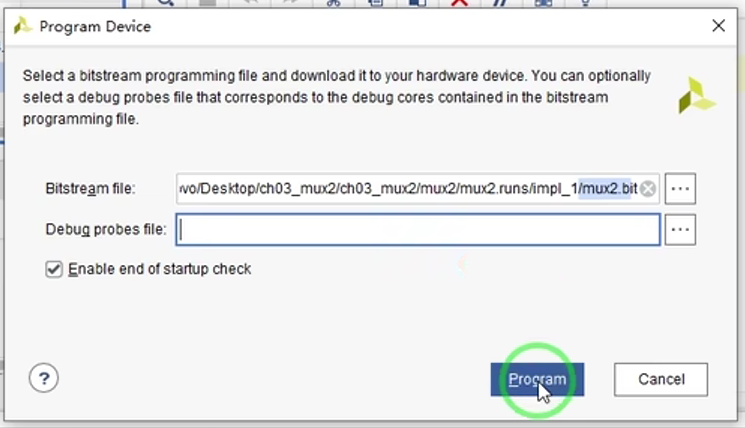

这里需要留意一下bit文件所存在的路径

如果在设计时加入了调试信息,第二栏是用来下载调试配置信息的,没有空着即可

确认好后点击Program

根据在仿真的test bench中的顺序来依次调整A B SEL的电平观察OUT的输出情况即可