一、前言

1.1 高扇出信号

在 FPGA 中,高扇出信号(High Fanout Signal) 是指一个信号驱动大量的负载(通常几十到数百甚至上千个)。常见的高扇出信号包括:全局复位 reset/enable、时钟使能信号 (CE)、总线控制信号、广播信号、同步清零、片选信号、某些顶层的地址/状态信号。

1.2 影响

高扇出信号比低扇出信号的路径延时更大,时序收敛更难,可能无法满足高频设计,甚至导致工程布线失败。因此,对比高扇出信号的处理方法是时序收敛操作的必备技能。

二、示例设计

下面是一个寄存器sig_q输出驱动64个负载的简单例子,实际设计中高扇出都是单个信号驱动成千上万的负载,本处设置64只为方面说明

module high_fanout #( parameter N = 64)

(

input wire clk,

input wire rst_n,

input wire in_sig,

output wire [N-1:0] out_sig

);

reg sig_q;

always @(posedge clk or negedge rst_n) begin

if (!rst_n)

sig_q <= 1'b0;

else

sig_q <= in_sig;

end

genvar i;

generate

for (i = 0; i < N; i = i + 1) begin : FAN

assign out_sig[i] = sig_q;

end

endgenerate

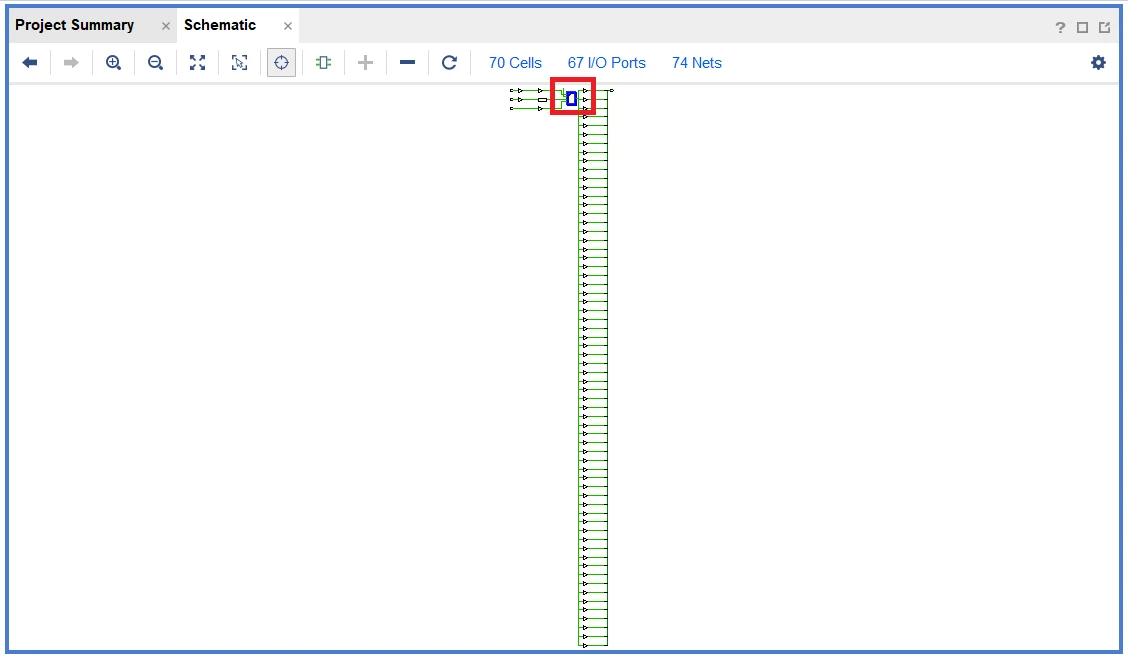

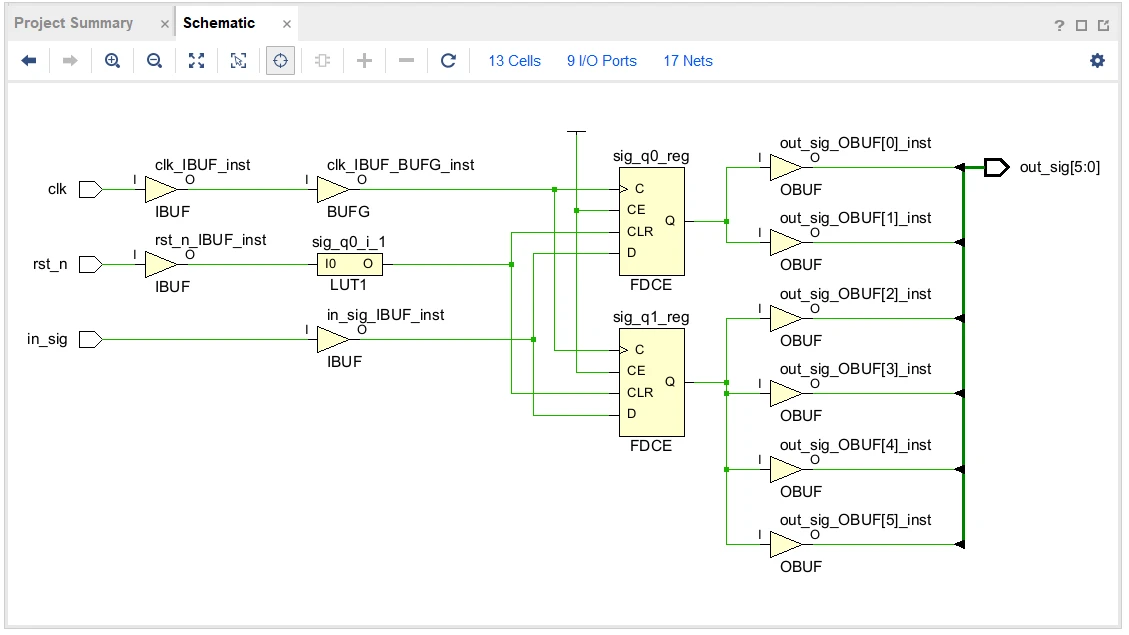

endmoduleschematic如下图,红色方框内的为sig_q_reg,驱动着后面所有负载

三、高fanout优化方法

上述工程示例中,寄存器sig_q输出驱动了64个负载,下面结合各种优化场景进行示例说明优化的具体操作

3.1 max_fanout属性

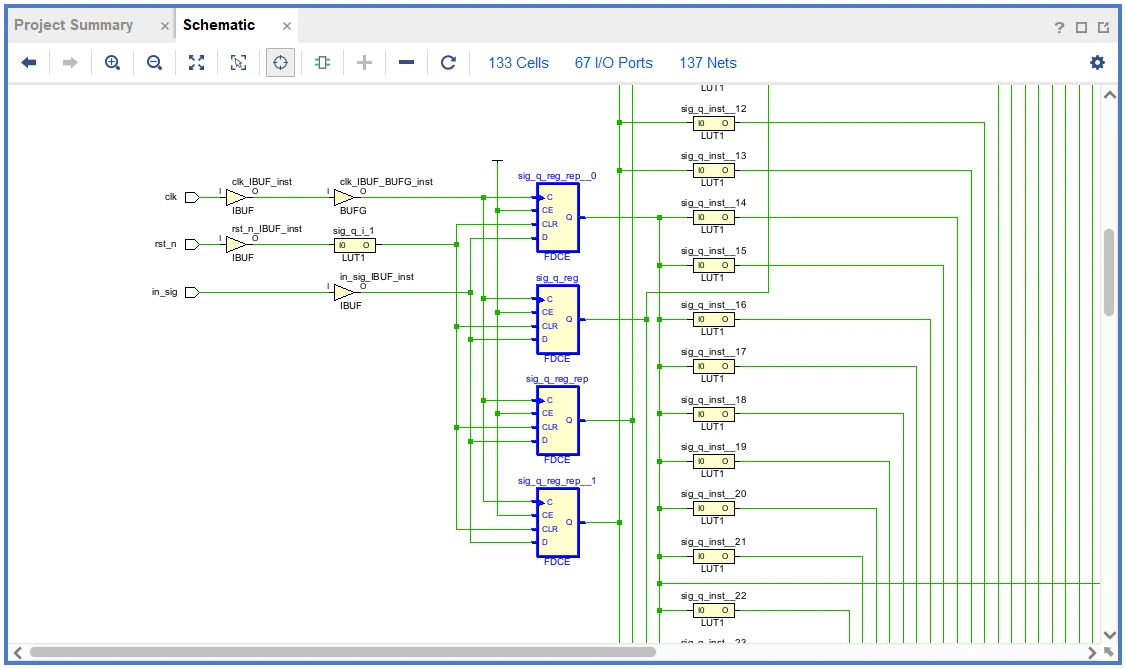

在设计中对高fanout信号添加max_fanout属性,如下图对寄存器驱动的最大扇出为16

(* max_fanout = 16 *) reg sig_q;schematic结果如下图,除了原设计中的寄存器sig_q_reg,软件还自动复制出了sig_q_reg_rep,sig_q_reg_rep_0,sig_q_reg_rep_1三个寄存器来分担驱动的负载

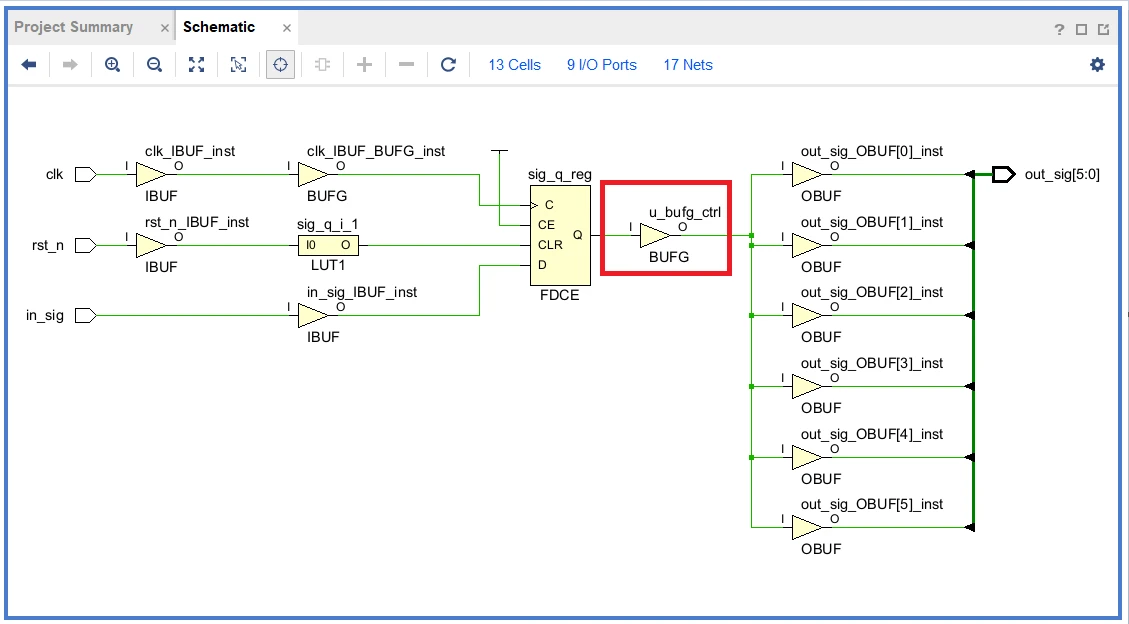

3.2 BUFG驱动

方法二是让驱动信号上BUFG,因为BUFG的驱动能力更强,延时小

assign n_sig_q=sig_q;

// 使用 BUFG 全局缓冲

BUFG u_bufg_ctrl (

.I(n_sig_q),

.O(n_bufg)

);schematic中sig_q_reg后经过了BUFG单元再驱动后面的负载

3.3 参数控制复制

对于高扇出信号,也可通过参数控制来设置复制寄存器的数量

module high_fanout #(

parameter N = 6

)(

input wire clk,

input wire rst_n,

input wire in_sig,

output wire [N-1:0] out_sig

);

(* DONT_TOUCH = "TRUE" *) reg [N-1:0] sig_q;

wire n_sig_q;

always @(posedge clk or negedge rst_n) begin

if (!rst_n)

sig_q <= {N{1'b0}};

else

sig_q <= {N{in_sig}};

end

assign out_sig = sig_q;

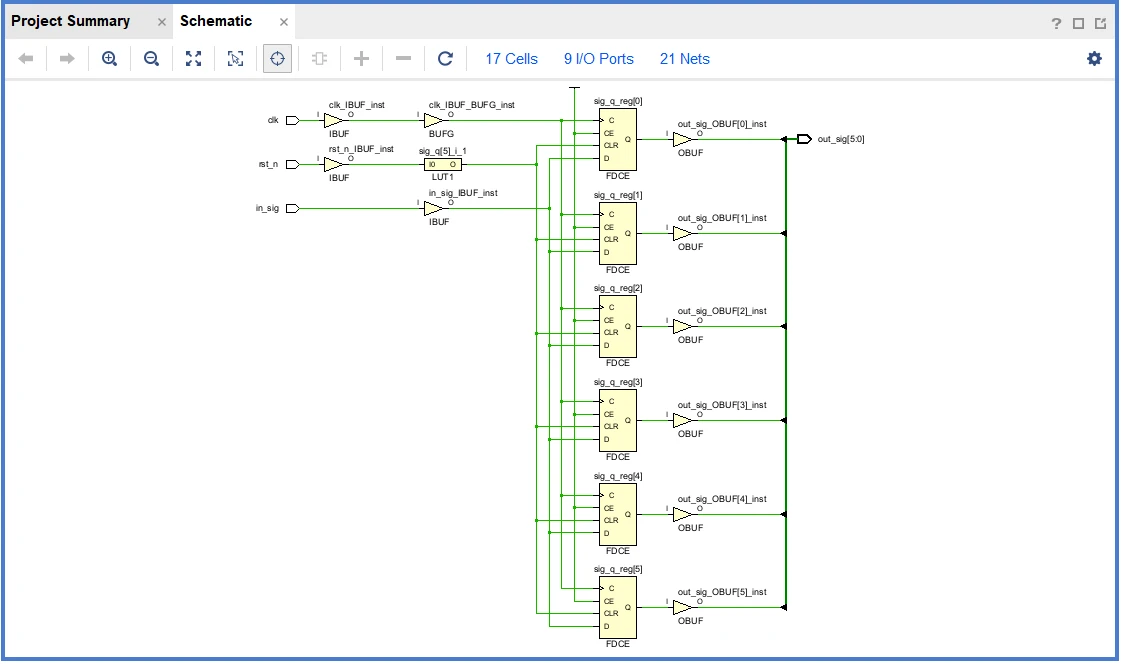

endmodule看schematic结果,in_sig信号中每一位都由一个寄存器驱动

3.4 手动复制寄存器

相比与参数控制复制寄存器,手动复制寄存器的方式更加灵活,如下图设计增加一个寄存器,并且将负载out_sig[1:0]由一个寄存器驱动,out_sig[6:2]由另一个寄存器驱动

module high_fanout #( parameter N = 6)

(

input wire clk,

input wire rst_n,

input wire in_sig,

output wire [N-1:0] out_sig

);

(* DONT_TOUCH = "TRUE" *) reg sig_q0;

(* DONT_TOUCH = "TRUE" *) reg sig_q1;

always @(posedge clk or negedge rst_n) begin

if (!rst_n)

begin

sig_q0 <= 1'b0;

sig_q1 <= 1'b0;

end

else

begin

sig_q0 <= in_sig;

sig_q1 <= in_sig;

end

end

// 把 fanout 分给两个寄存器

assign out_sig[0] = sig_q0;

assign out_sig[1] = sig_q0;

assign out_sig[2] = sig_q1;

assign out_sig[3] = sig_q1;

assign out_sig[4] = sig_q1;

assign out_sig[5] = sig_q1;

endmoduleshematic图如下,和预期的一致

3.5 寄存器复制数量参考

根据设计经验,对于使用寄存器复制的数量可参照下图