该工程实现了PL通过HP接口(8个字节)下使用AXI协议往DDR中写数据。PS读取处理 。

这种就是不断地读那块资源。CPU资源浪费下节是DMA

当前简单的传输1.PS并不知道什么时候传输数据,需要PL给一个中断,然后PS读取中断以后,在进行读取。2PL端口要告诉PS从哪个地址写入的数据,都需要PL告诉PS 端口

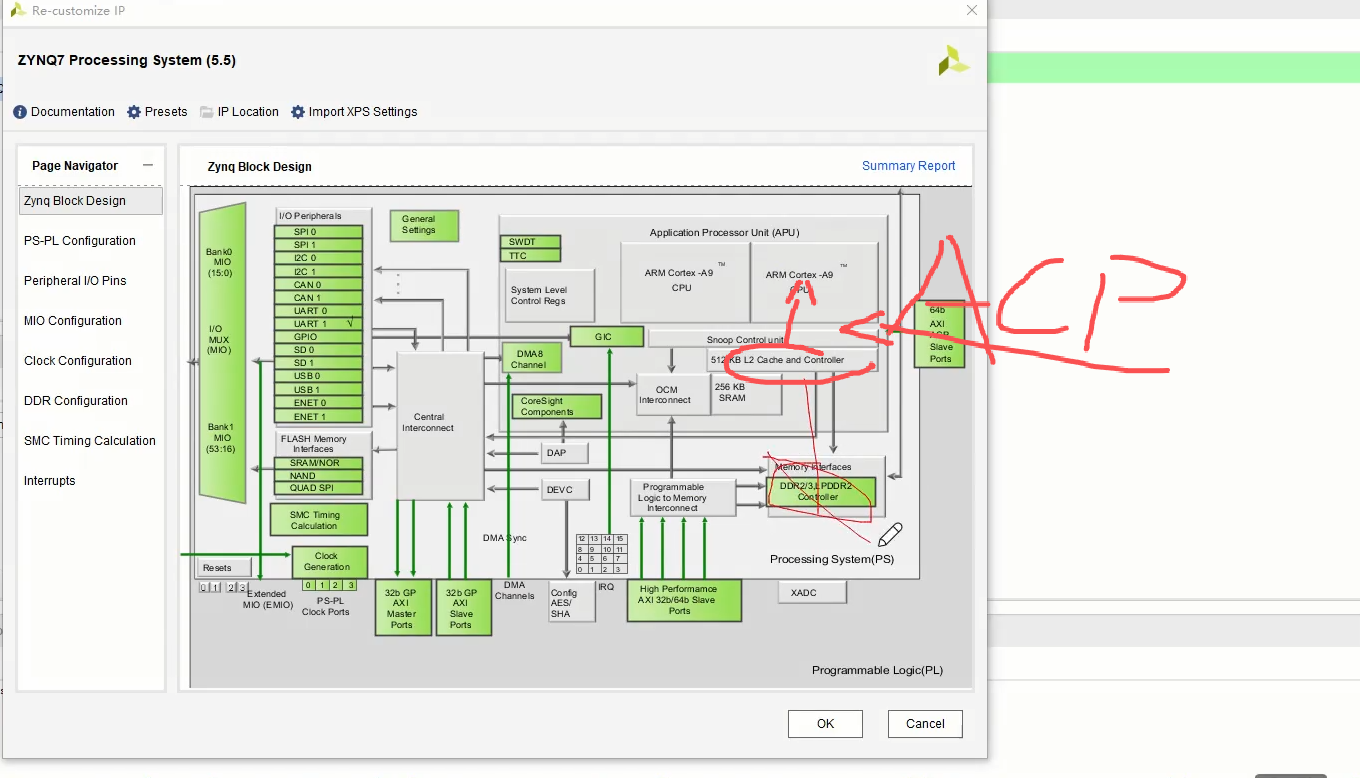

GP接口是PS和PL 少量数据的接口。

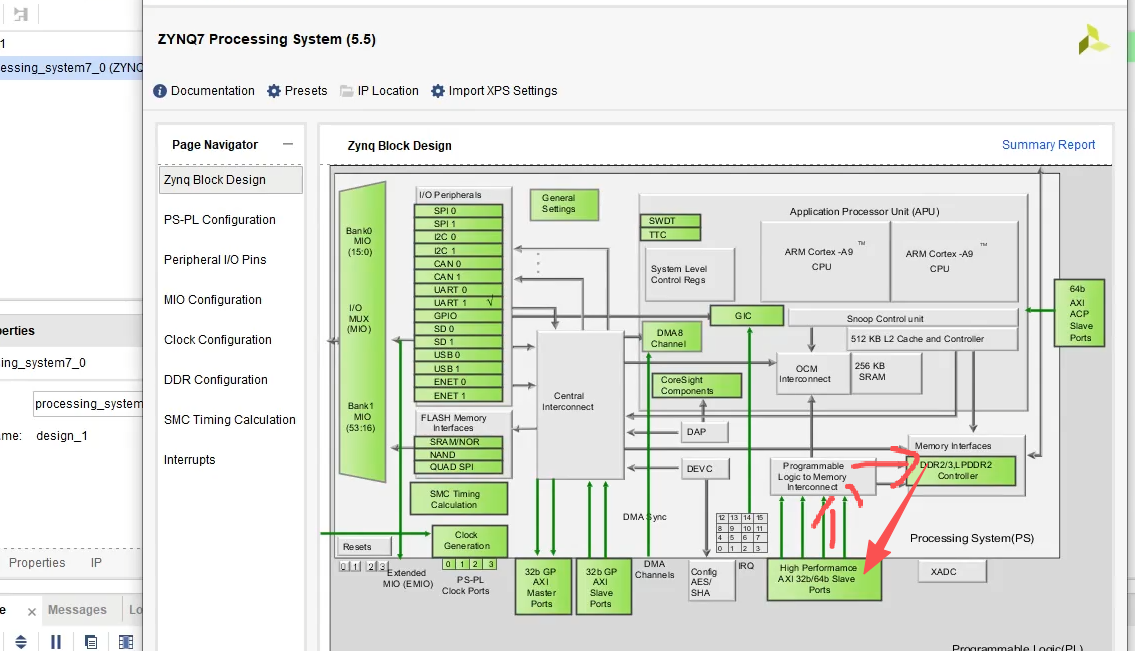

但是要大数据交互需要用到高性能总线 HP接口 把数据送给DDR

还有一种速度较快的ACP接口 外部数据通过ACP接口通过CACHE送给CPU进行操作。 但是不好操作DMA,一般用HP接口。

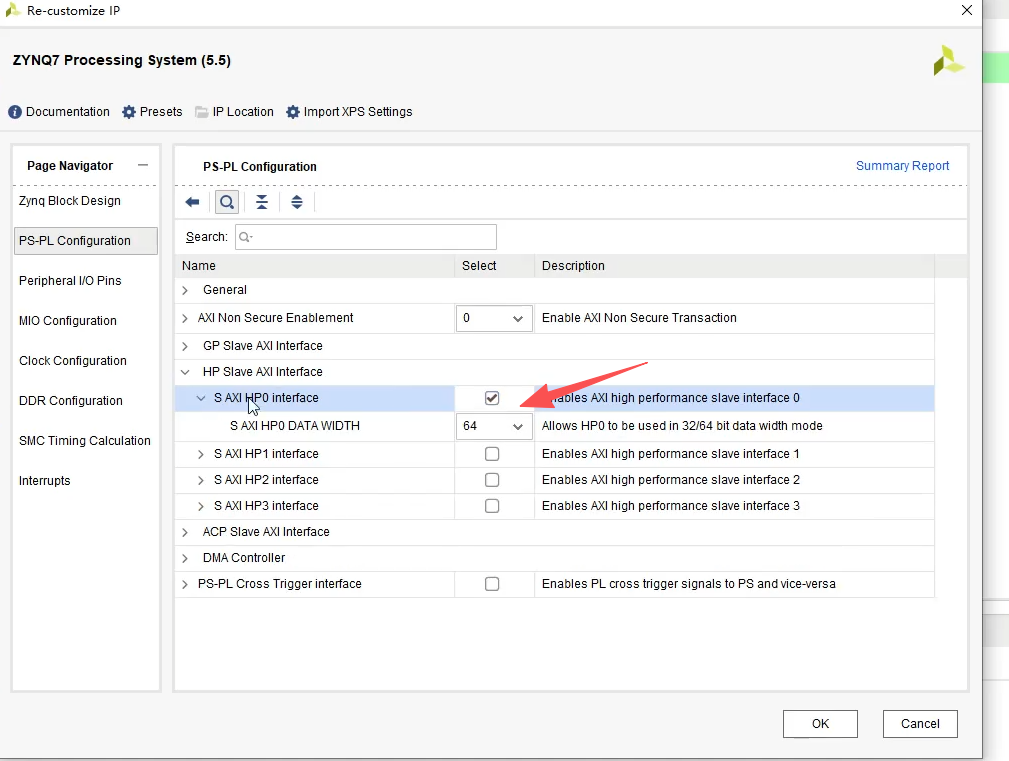

1设置HP接口

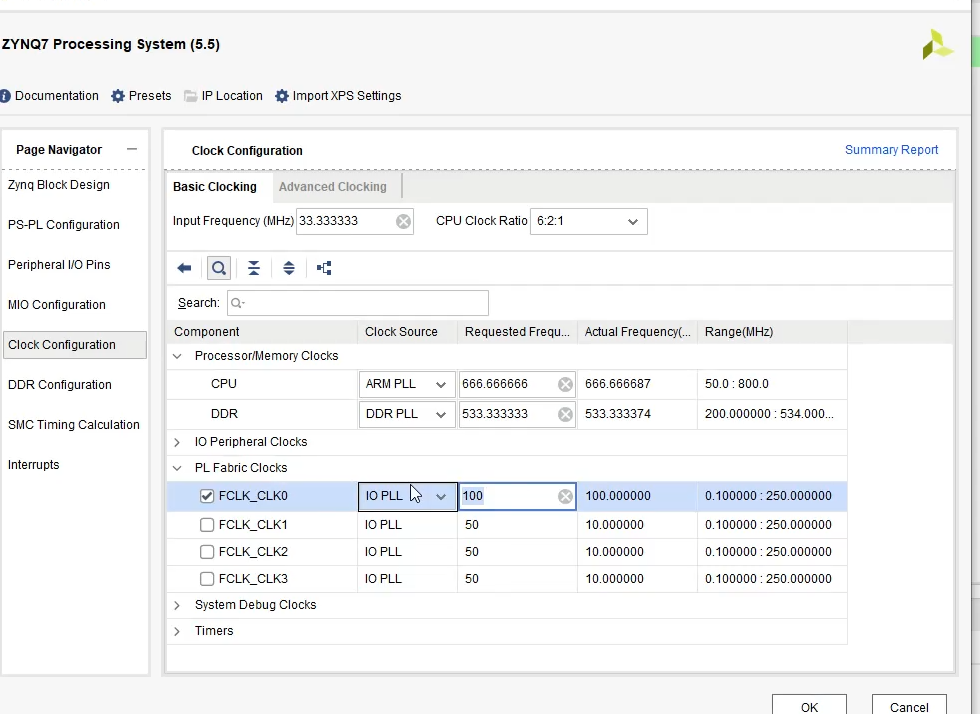

设置时钟和复位

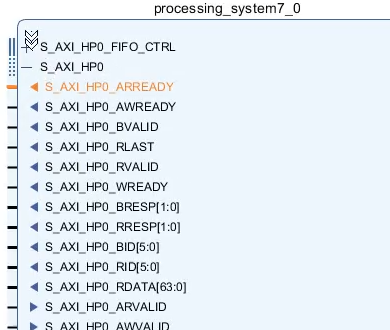

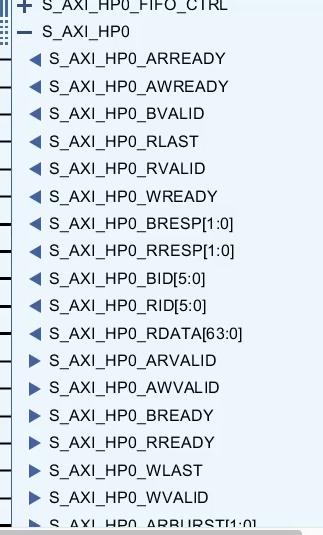

可以看到HP接口是axifulll协议

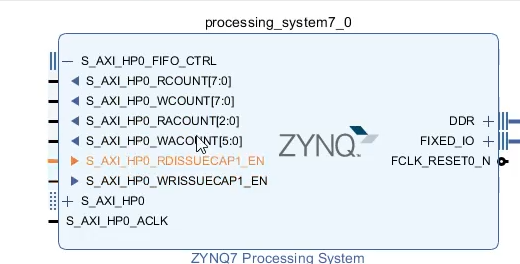

存入多少数据等等呢个

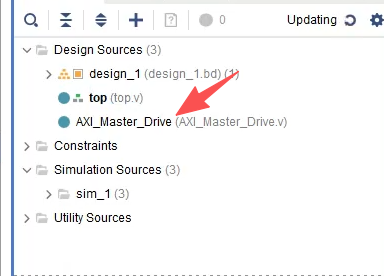

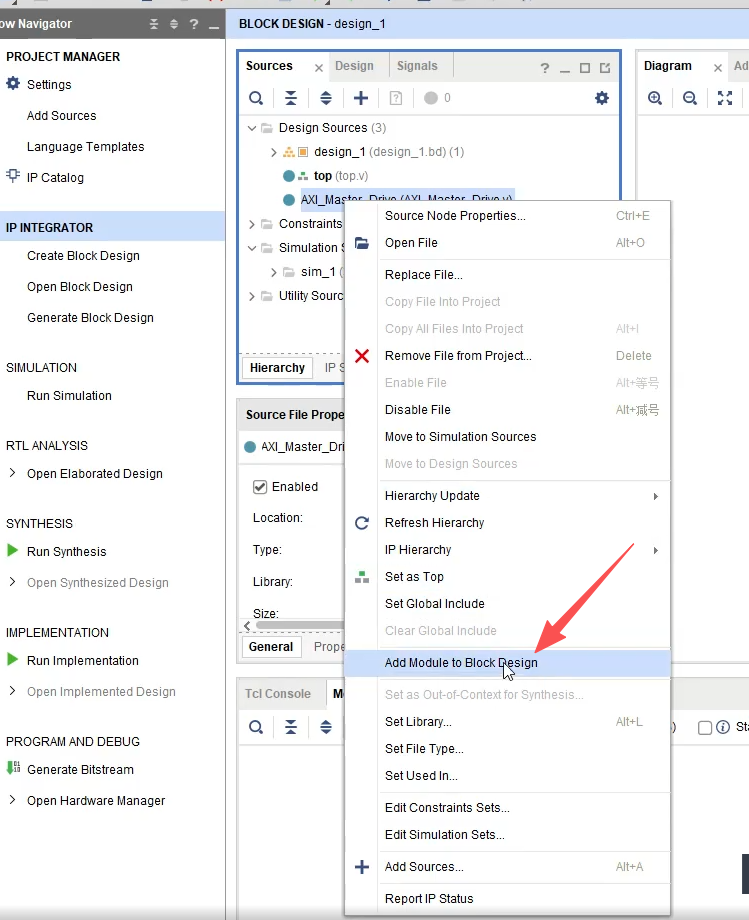

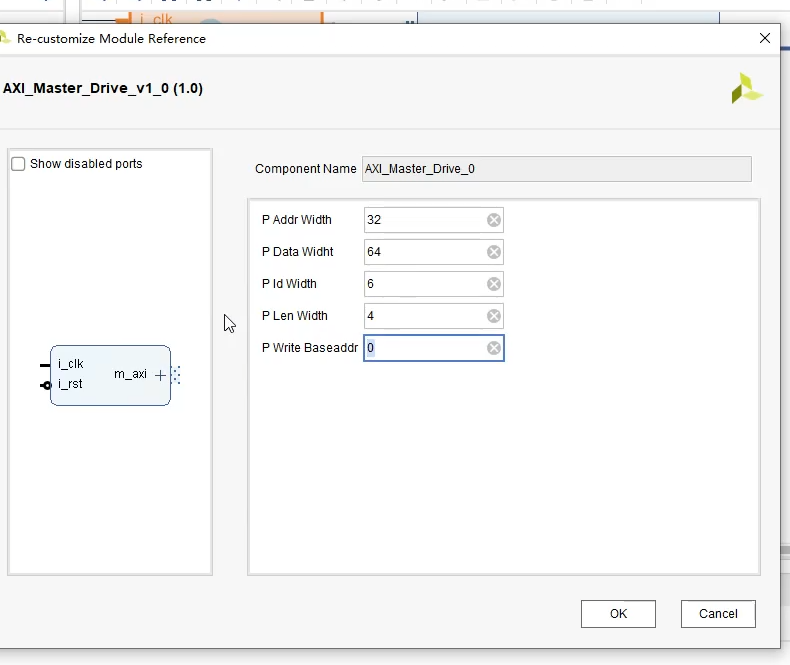

创建一个AXI主机接口添加到工程

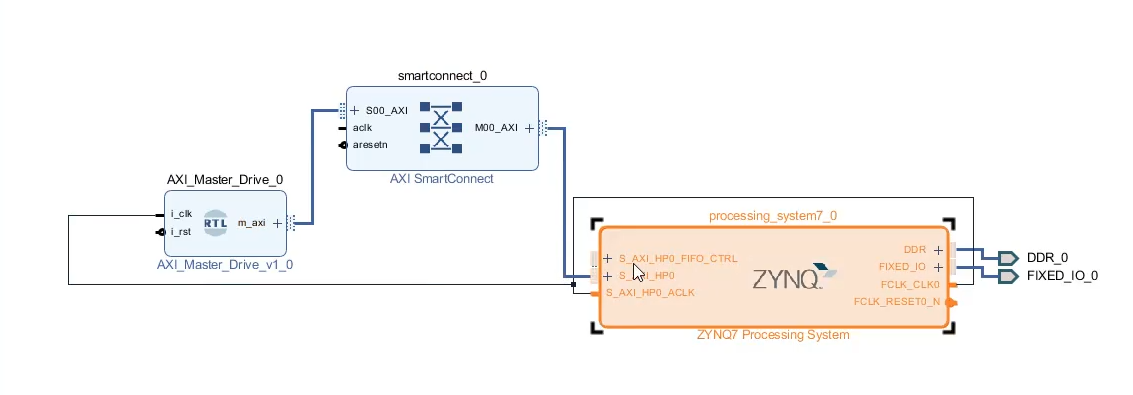

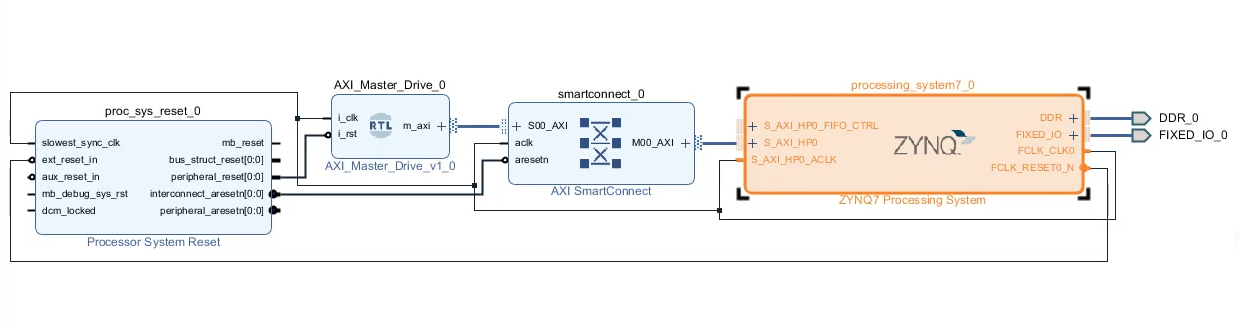

MASTER的Drive 需要互联模块。在添加复位模块

连接完成后

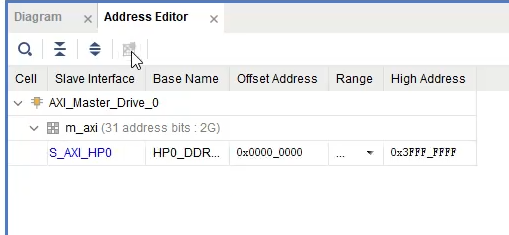

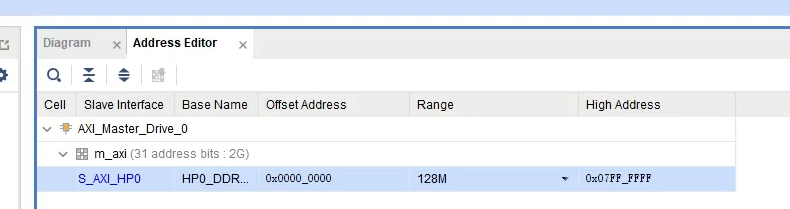

分配地址。

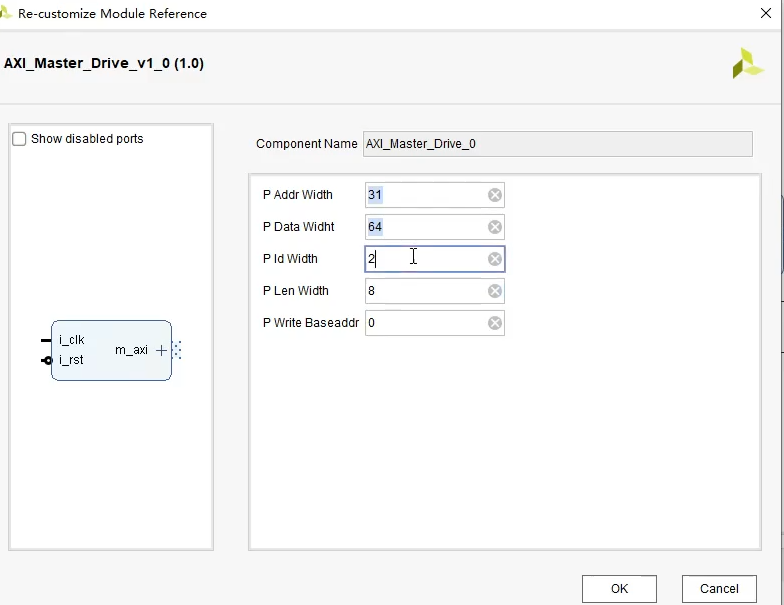

在rtl中的PARAMETER可以在 ps中进行设计

根据HP接口的位宽 设置自己写的模块

根据HP接口的位宽 设置自己写的模块

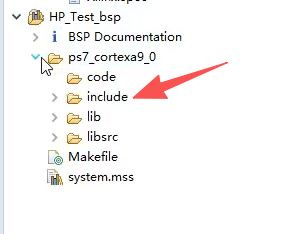

2.启动SDK

建立工程

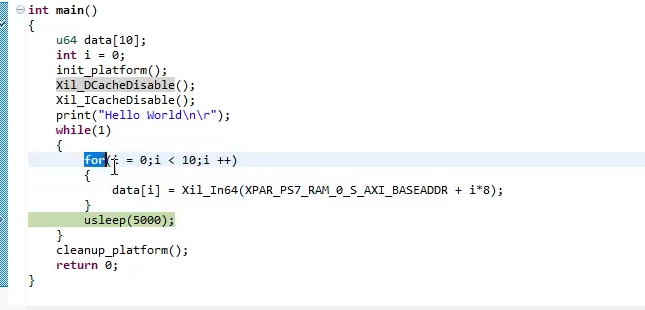

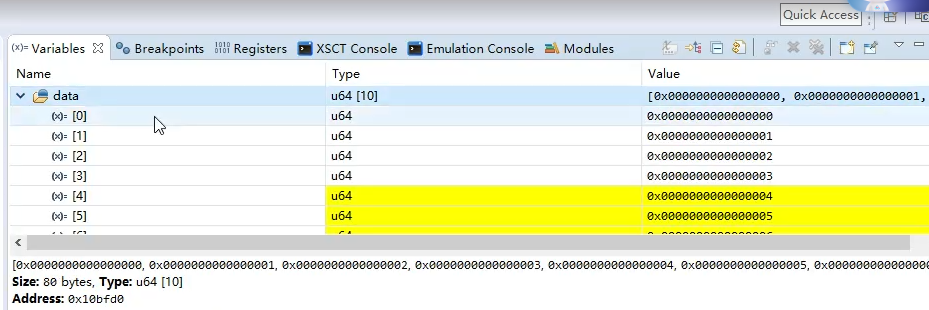

上一次工程是读BRAM的内存 DDR也是一个内存 是一样的逻辑

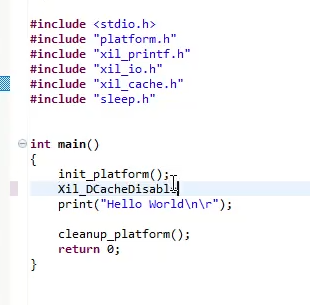

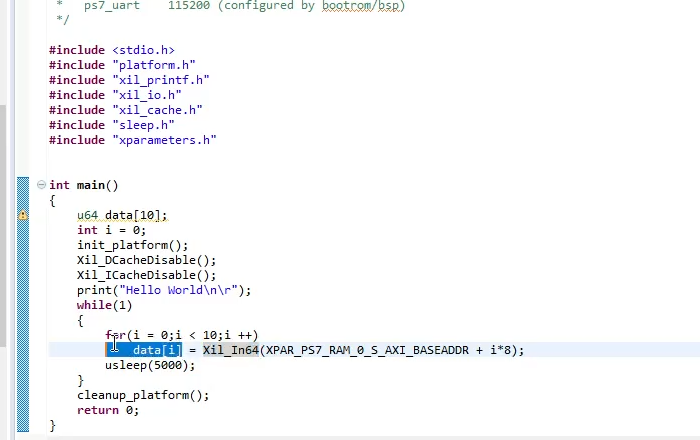

将头文件添加进去

这里需要禁用cache 不知道什么时候刷新cache所以禁用 ,如果刷新了但是PL的DDR中没有数据,就会取数据错误。

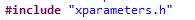

在读数据的时候HP接口是64位的数据,所以用到IN64函数 ,送入的地址,可以在ps端口进行看到分配的内存,还可以 ,在bBsP 参数中找到参数

,在bBsP 参数中找到参数

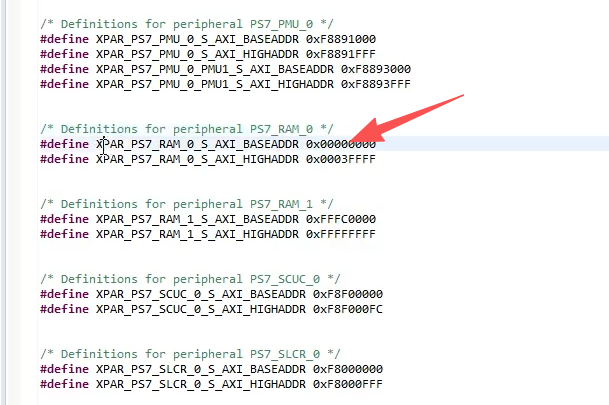

AXIHP从机模块的基址

因为一次写入的是64个bit 也就是8个字节 (这里需要看下PL测写入的是一次地址是8个地址)下一次取的地址就需要加8

PL(可编程逻辑)侧完成一次64字节的数据传输后,下一次写入的起始地址通常是当前基地址加上64(即十六进制的0x40)

为了让你快速把握全局,下表详细列出了在不同传输场景下,下一次写入地址的计算方式:

| 传输场景 | 本次写入起始地址 | 本次写入数据量 | 下一次写入起始地址 | 核心原理说明 |

|---|---|---|---|---|

| 单次突发(Burst)传输 | 0x0000 | 64字节 | 0x0040 (0x0000 + 64) | AXI协议基于字节寻址。每次突发传输结束后,主设备(PL)需要重新发起一次新的传输,并手动设置新的起始地址 |

| 连续突发传输(自动递增) | 0x0000 | 64字节 | 由AXI控制器自动计算 | 在配置为突发模式时,AXI IP核(如Datamover)的内部逻辑会在一次事务中自动根据突发长度(Burst Length)递增地址,但整个突发事务本身只使用一个起始地址。事务结束后,若需再次传输,地址仍需手动设置为0x0040 |

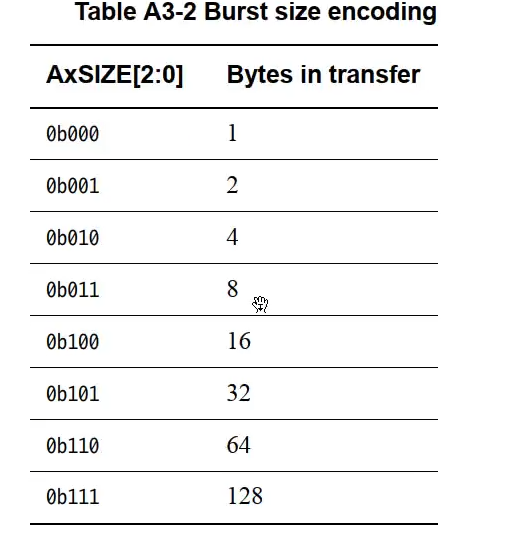

AXI 设置一次突发的多少个字节HP接口是8个字节 直接送到DDR是32个字节

AXI 设置一次突发的多少个字节HP接口是8个字节 直接送到DDR是32个字节

数组中的数据

3.开发经验

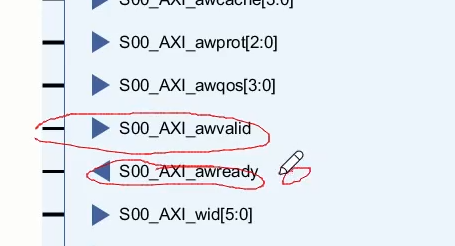

在axi传输中 PS一侧的从机HP接口,如果主机给Valid拉高但是从机的ready没有反应这时候可能是在字节 突发的等等不对。