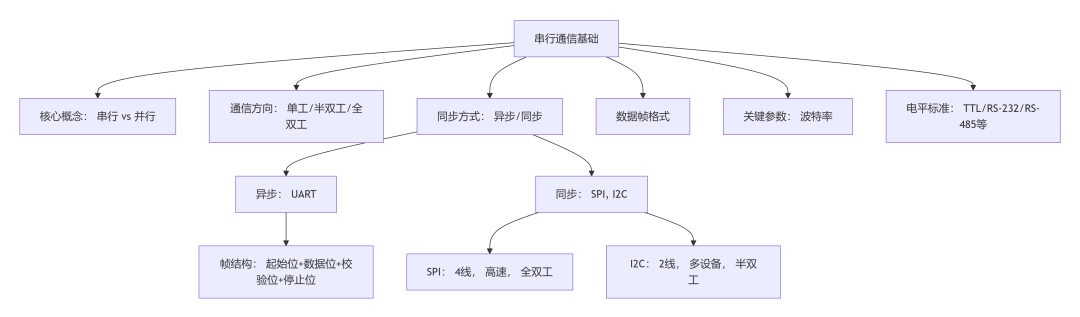

串行通信是电子设备中数据交换的基石。最常见的串行通信协议有UART,SPI,I2C等。

本文将介绍串行通信相关的基础知识。为后面用FPGA实现这些串行协议的案例做准备。

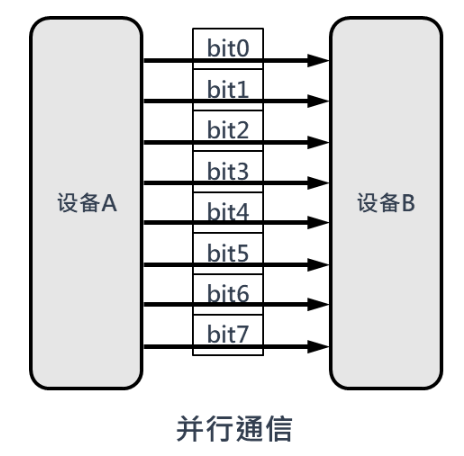

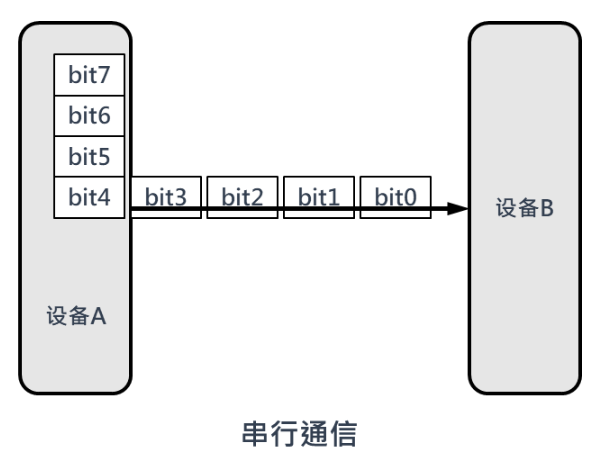

- 并行通信和串行通信

并行通信:数据各个位用多条数据线同时进行传输 (传输速度快,但占用引脚资源多)。

串行通信:数据分成一位一位的形式在一条数据线上逐个传输(通信线路简单,占用资源少,但速度慢)。

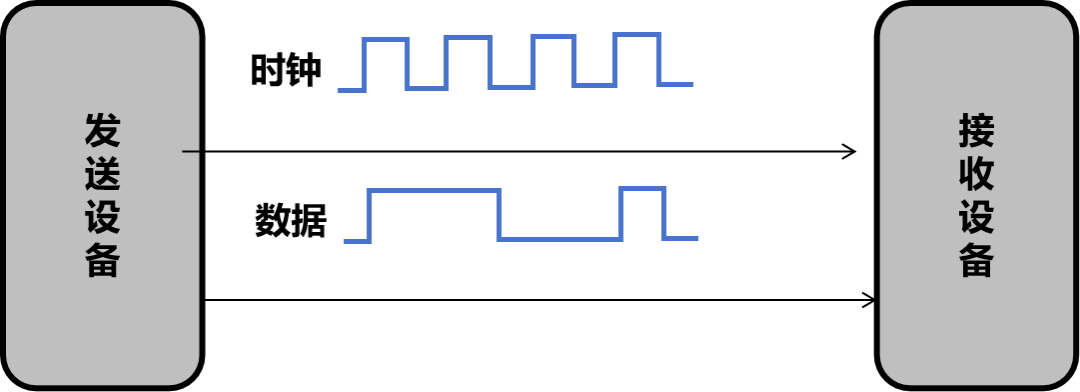

- 同步通信和异步通信

同步通信:带时钟同步信号的数据传输,发送方和接收方在同一时钟的控制下同步传输数据。

异步通信:不带时钟同步信号的数据传输,发送方和接收方使用各自的时钟控制数据的发送和接收过程。

在没有时钟同步的情况下,收发双方约定好 ,比如发送方在每秒传输 115200个 数据,那么,接收方也在每秒接收 115200个 数据。

异步通信需要起始位和停止位来界定一个数据帧。双方时钟误差累积会导致误码,故单次传输数据量不宜过大(通常≤10位)。

- 单工、半双工、全双工

串行通信的传输方向有如下三种:

单工通信:数据只能单向传输;

半双工通信:数据可以双向传输,但不能同时进行(如I2C);

全双工通信:数据可以同时双向传输(如UART、SPI)。

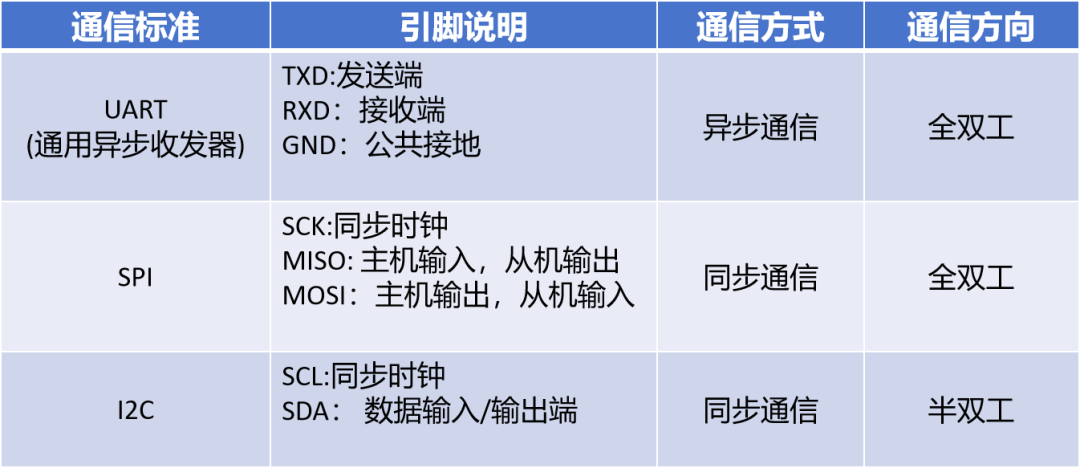

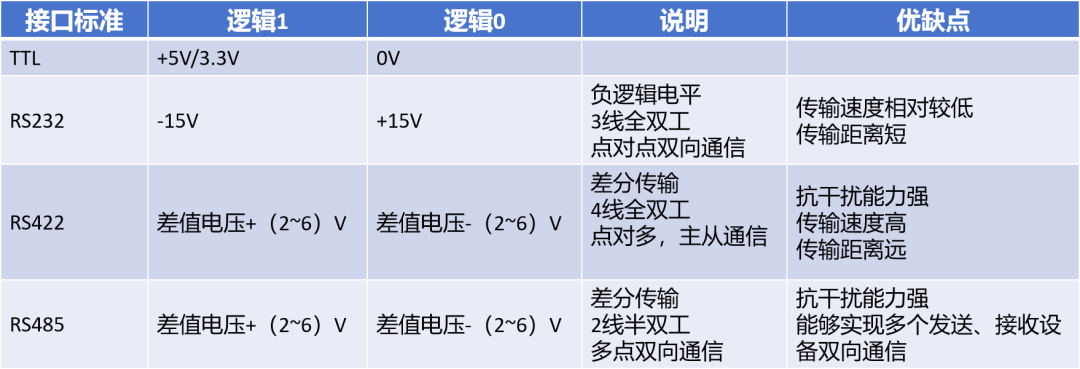

常见的串行通信接口:

前面已经发布过FPGA实现SPI协议的相关案例,有兴趣可以参考:

05-基于FPGA和LTC2308的数字电压表设计-用FPGA实现SPI协议通讯

04-基于FPGA和LTC2308的数字电压表设计-SPI协议详解

近期将发布不同FPGA开发板上的串口应用案例的设计。

后期还将发布基于FPGA的HDMI发送器(ADV7513)的I2C协议控制相关的设计,敬请期待。

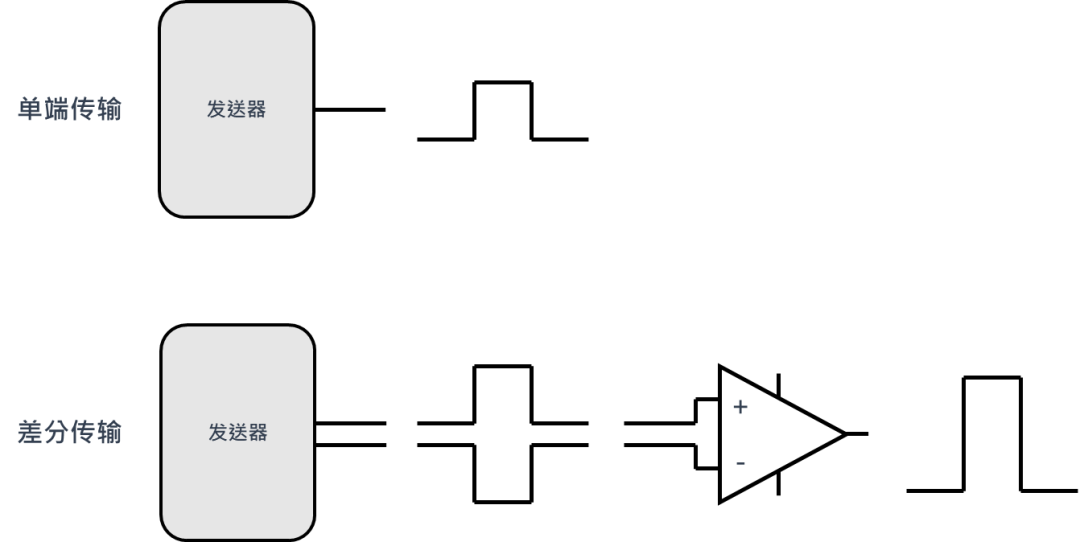

- 单端传输和差分传输

单端传输:用信号线对GND的电压值来表示逻辑"0"和"1";

差分传输:用两根信号线来传输一路信号,两根信号线上传输的信号幅值相等,相位差为180°(极性相反),用它们的差值来表示逻辑"0"和"1"。

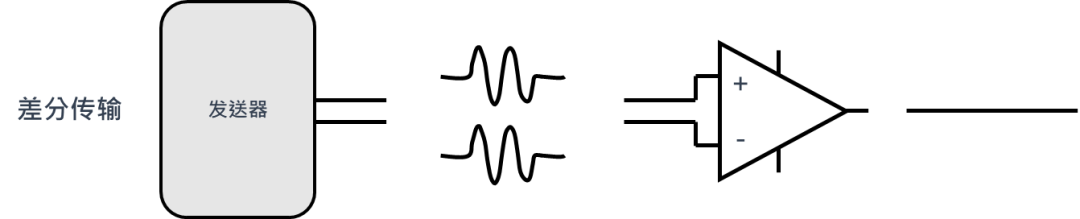

差分传输利于消除共模干扰(共模干扰是指在导线与地之间产生一个与有用信号同向的无用电信号,如下所示)。

从两信号线差值可知引入的噪声并不会影响接收端判断传输的数据。

- UART协议

UART 是universal asynchronous receiver-transmitter的缩写,是一种采用全双工异步串行通信的通信方式。

UART传输格式

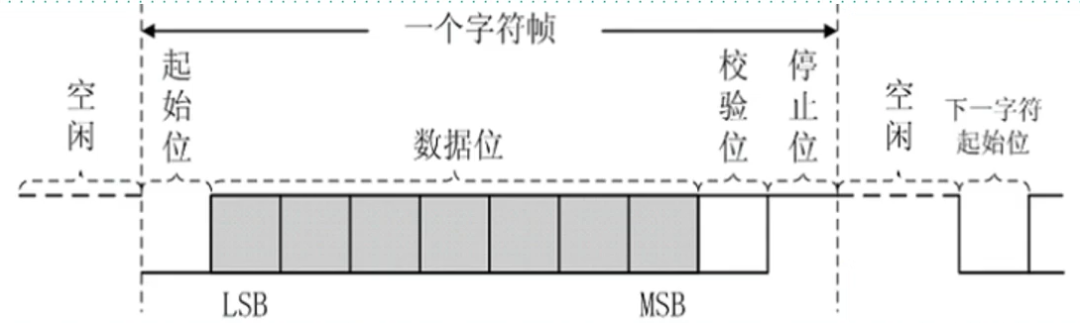

UART协议层的通信协议数据格式如下:

空闲:高电平(总线空闲);

起始位:低电平;

数据位:先发低位,后发高位,数据位可以是5位,6位,7位,8位(数据位具体是多少位由串口收发双方提前约定好);

校验位:分奇校验和偶校验,该位可省略;

停止位:1位、1.5位、2位可选。

UART传输速率

串口通信的速率用波特率表示,它表示每秒传输的符号数,单位是Bd。

因为UART编码方式(采用NRZ)非常简单,一个符号就是一个比特。所以,当人们说"串口速率为115200"时,实际指的是波特率为115200 Baud,同时比特率也是115200 bps。

常用的波特率有9600、19200、38400、57600 、115200。

串口传输的位周期

位周期代表串口传输一个bit所占用的时间。假设系统时钟是50MHz,波特率是115200Bd,那么串口发送和接收时,数据的每个位将占用1/115200=8.68us,每个位占用50000000/115200 ≈ 434个系统时钟周期。

奇偶校验

奇偶校验(Parity Check)是一种验证数据传输正确与否的方法。

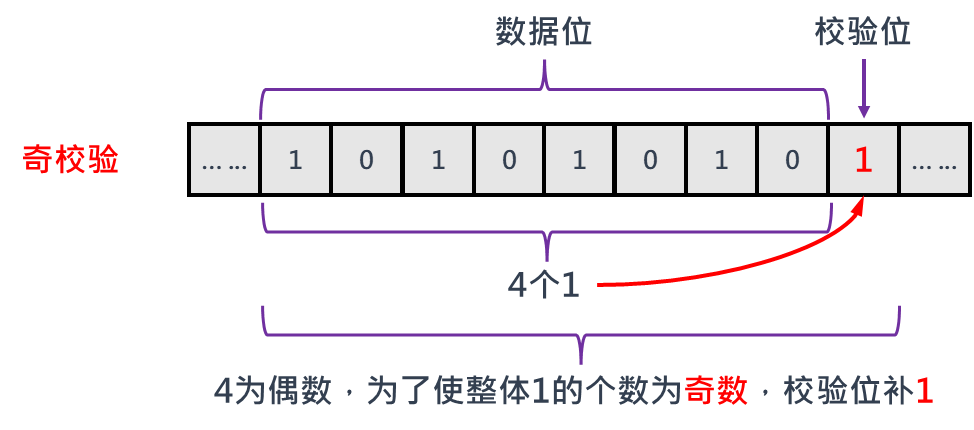

奇校验(Odd Parity):通过设置校验位为"1"或"0",让传输的数据(包含校验位)中"1"的个数为奇数。

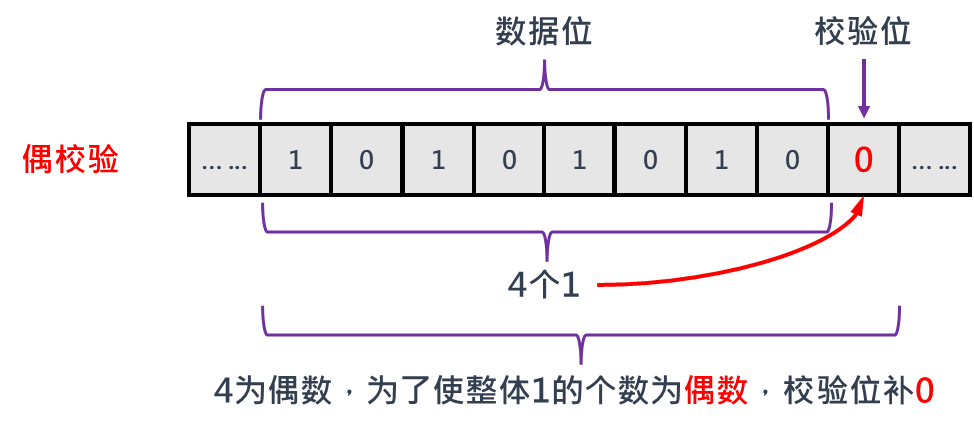

偶校验(Even Parity):通过设置校验位为"1"或"0",让传输的数据(包含校验位)中"1"的个数为偶数。

以发送数据"10101010"为例(数据中包含4个"1"),奇校验时校验位应设置为"1":

偶校验时校验位应设置为"0":

奇偶校验的缺点:无法检测双位错误;没办法确定哪一位出错;不能修正。所以一般应用中有的人会直接舍弃校验位。

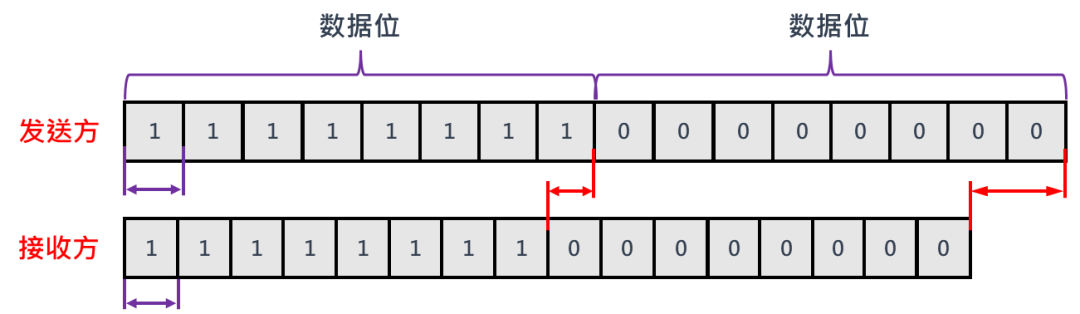

消除累计误差

UART发送方和接收方使用各自的时钟,在这种情况下容易产生累计误差。比如发送方首先发送1-bit数据,它计时了1s后开始发送第二个1-bit数据,可是接收方在接收第一个1-bit数据时,它只计时了0.9s,发送方在发送完一个8-bit数据后,会产生误差;如果第二次发送数据时又紧接着发,那误差累计就会导致误差越来越大。

为了消除累计误差,UART一次只能发送一个字节的数据,不能连续发送多个字节数据。

- 电平转换

UART是通信协议,它定义了数据的格式。UART通常以 TTL/CMOS 电平在芯片之间传输。其逻辑 1 是 3.3V/5V,逻辑 0 是 0V。它只在板级或极短距离内有效,因为 TTL 电平抗干扰能力差,传输距离短。

想要UART通信抗干扰能力强,传输距离变远,在物理层上需要采用RS-232, RS-422, RS-485标准进行UART信号传输。

FPGA 的 UART 模块(TTL 电平)不能直接接 RS-232 或 RS-422/485 网络,需要一个 "电平转换芯片" 作为桥梁。

就拿DE2-115开发板上的RS232接口来说,RS232的电平使用负逻辑电平,和FPGA 的电平(TTL)不一样,需要中间的转换芯片,DE2-115开发板采用的是ZT3232LEEY,将+-15v的逻辑电平转换为TTL电平。

RS-232 、 RS-422和RS-485的物理接口一般采用DB9接口或者凤凰头接口(接口形式不固定,也有其他物理接口比如网口等)。

DB9接口:

凤凰头接口:

这是 RS-232、RS-422 和 RS-485 标准在最常见的 DB9 接口上的物理接口引脚定义表格:

但DB9的体积比较大,为了节省开发板的空间,现在大多用USB口替代,比如C5G和TSP开发板,分别用FT232R和CP2102N来作为USB电平和TTL电平之间的转换,以及uart协议和USB协议之间的转换。

具体流程如下:

-

FPGA 仍通过 UART (TTL) 发送数据。

-

数据发送给 USB转UART芯片。

-

该芯片将简单的 UART 协议数据打包成复杂的 USB 协议数据包。

-

电脑接收到 USB 数据包后,需要安装驱动程序,将其解包还原成 UART 数据,并在操作系统中创建一个虚拟串口(如 COM3)。

这样,上位机软件就可以像操作传统串口一样,通过这个虚拟串口与 FPGA 通信了。

所以,当我们在设计FPGA串口收发的时候,只需要按UART协议收发数据,CH340G、FT232R和CP2102N芯片会帮我们完成uart与外部USB设备之间信号转换。

TSP开发板的USB转UART桥接芯片采用CP2102N,C5G开发板采用FT232R,DE10-Standard开发板采用CH340G,DE23-Lite开发板采用FT2232H。

后续即将发布:

2-基于TSP 开发板的FPGA 串口通信设计 (CP2102N)

3-基于DE10-Standard 开发板的FPGA 串口通信设计 (CH340G)

4-基于DE23-Lite 开发板的FPGA 串口通信设计 (FT2232H)

5-基于C5G 开发板的FPGA 串口通信设计 (采用Nios II控制Intel Uart IP进行串口收发)

本文知识点总结如下: