1. 概述设计

通用的通感算控算存一体化平台,采用GPU+RFSOC+VU13P/VU9P通用整机设备设计,满足通信、雷达、电子对抗、通感控算、AI无线感知等领域的通用方案设计,满足客户快速搭建验证整机平台,完成试验验证与测试的条件。系统整体构架方案如下图所示:

2. 系统组成设计

通用的通感算控算存一体化平台由1个RFSOC核心板(RFSOC XCZU47DR)、1个XCVU13P/XCVU9P核心板、1 GPU核心板、1个接口扩展载板组成。

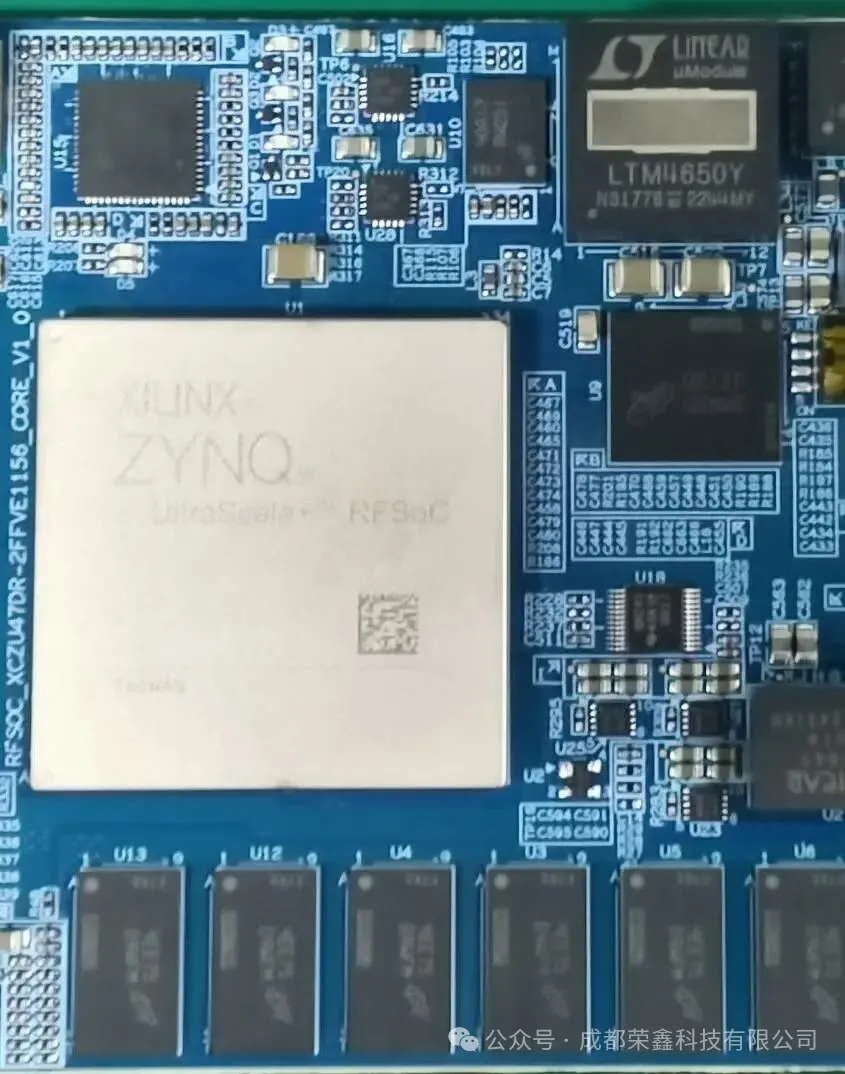

2.1 RFSOC核心板设计

RFSOC 核心板采用射频直采架构,带有8个独立的发射器和接收器通道。集成可编程Xilinx RFSoC FPGA最小系统,支持软件无线电开发架构,具备大带宽和大规模运算处理能力,可用于无线通信原型验证、频谱监测、信号智能及宽带信号采集存储回放等。可以广泛应用5G射频基带、相控阵系统、雷达系统、软件无线电、频谱监测、医疗系统等领域。RFSOC核心板配备19.2MHz恒温晶体振荡器(OCXO)参考时钟,提高了频率精度和同步性。

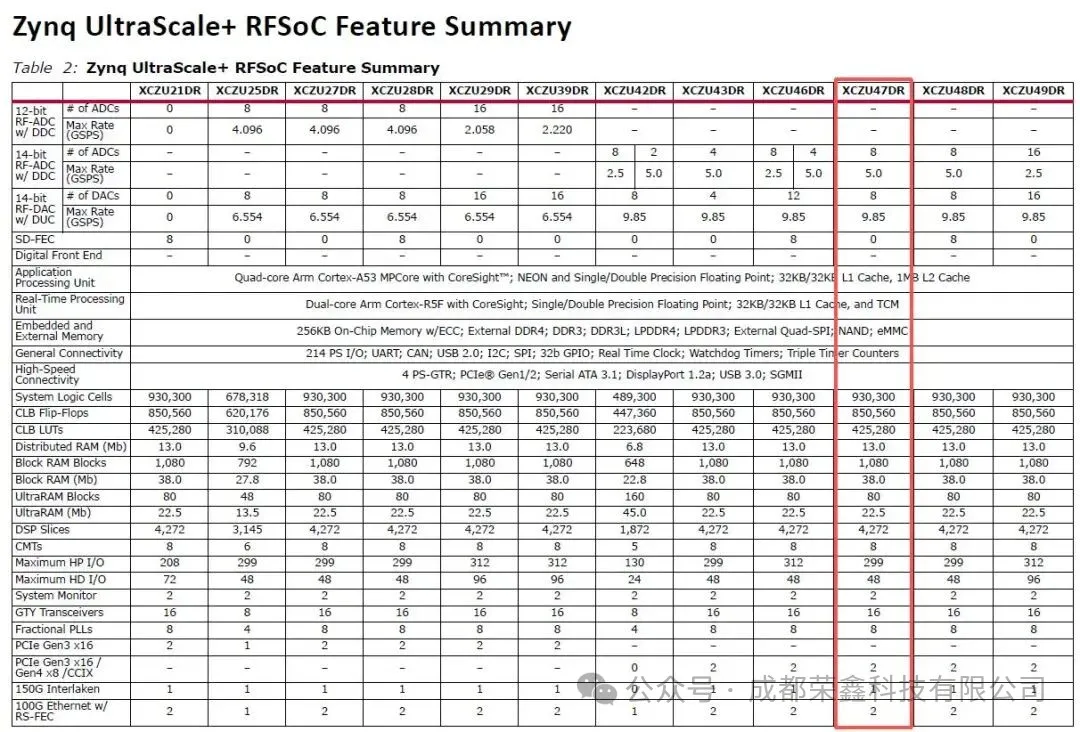

RFSOC XCZU47DR资源列表

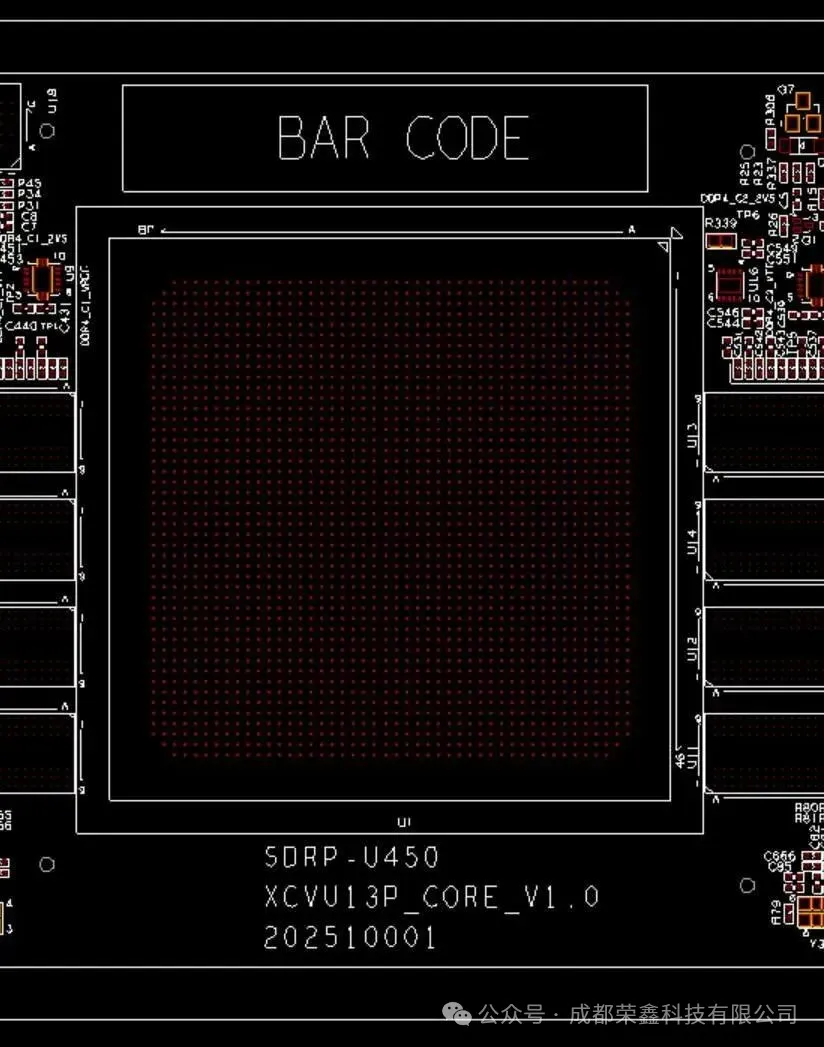

2.2 XCVU13P/XCVU9P核心板设计

Xilinx公司Virtex Ultrascale+ XCVU13P/VU9P核心模块,模块将XCVU13P-2FHGB2104I/XCVU9P-2FLGB2104I芯片及其最小系统集成在了一个85*125mm的核心板上,可以作为一个紧凑的核心,进行功能的扩展,能够快速的搭建起一个高性能的FPGA的信号处理平台,缩短用户的产品研发周期。

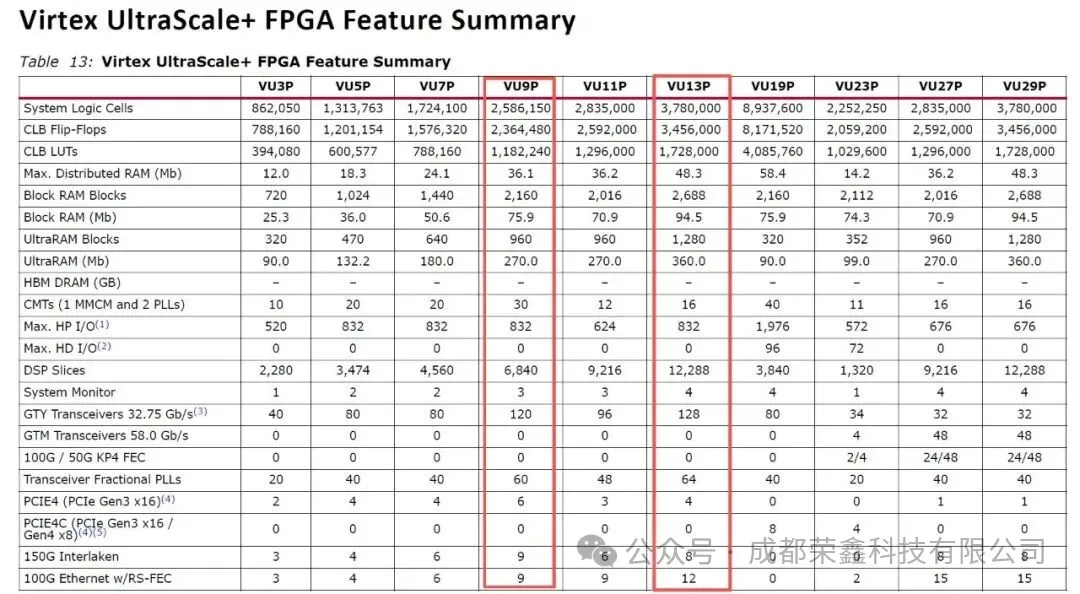

XCVU13P/VU9P FPGA详细资源分配表:

2.3 GPU模块设计

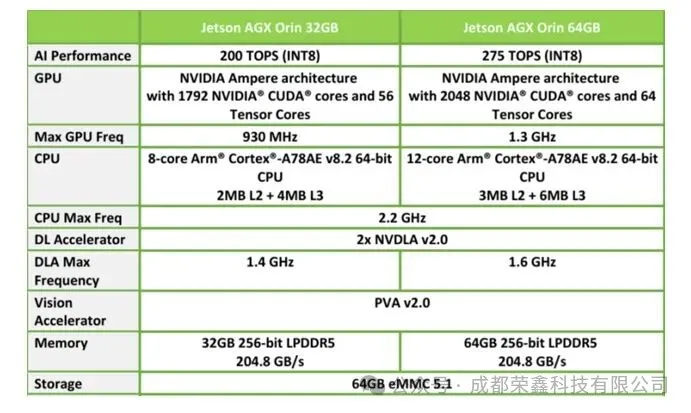

GPU采用NVIDIA Jetson AGX Orin模组可提供高达 275TOPS 的AI性能,功率可在15瓦到60 瓦之间进行配置。

此模组的外形规格与 Jetson AGX Xavier相同,但其性能可高达后者的 8 倍以上。Jetson AGX Orin有64GB、32GB版本。

GPU资源配置图:

2.4 接口扩展载板

a. 核心板之间互联接口

(1)VU13P/VU9P核心板与RFSOC核心板之间1路GTYx4接口和10个GPIO接口;

(2)VU13P/VU9P核心板与GPU之间1路PCIEx4接口和GPIO接口。

b. 射频接口

载板RFSCO核心板8路ADC和8路DAC全部扩展出来:

(1)8 路ADC巴伦电路射频接口SMA;

(2)8 路DAC 巴伦电路射频接口SMA。

c. 存储接口

载板上配置有M.2 SSD存储接口,用于大容量数据存储:

(1)RFSOC核心板扩展1路 FPGA PL PCIEx4和1路PS PCIEx2存储盘;

(2)VU13P核心板扩展4路PCIEx4存储盘;

(3)GPU扩展1路PCIEx4存储盘。

d. QSFP高速接口

VU13P核心板扩展2路QSFP高速接口,速率支持40G/100G高速传输。

e. 千兆网口

(1)RFSOC核心板PS端1路千兆以太网接口;

(2)GPU扩展1路千兆以太网接口。

f. USB接口

(1)RFSOC核心板扩展1路USB接口;

(2)GPU扩展两路USB接口。

g. HDMI接口

GPU扩展1路HDMI接口。

h. 外部参考时钟

载板一个外部输入时钟接口。

i. BD/GPS接口

载板扩展1路BD/GPS接口,接入到VU13P核心板。

j. TRIG接口

载板扩展1路TRIG触发接口,接入到VU13P核心板。

k .J30J扩展接口

载板J30J IO扩展接口,接入到VU13P核心板和RFSOC核心板。

l .FMC扩展接口

标准FMC扩展卡接口,接入到VU13P核心板。

m. 调试接口

载板预留出RFSOC核心板、VU13P核心板以及GPU的调试接口以及串口。

3. 供电设计

设备供电采用12V/30A设计供电要求。

4. 重量及体积设计

(1)重量:≤2kg;

(2)尺寸大小:300mmx200mm。

5. 环境适应性设计

(1)工作温度:-40℃~+55℃;

(2)存储温度:-50℃~+70℃;

(3)湿热:20°~40°(95°)。

成都荣鑫科技原创内容,欢迎技术交流及合作,盗者必追究