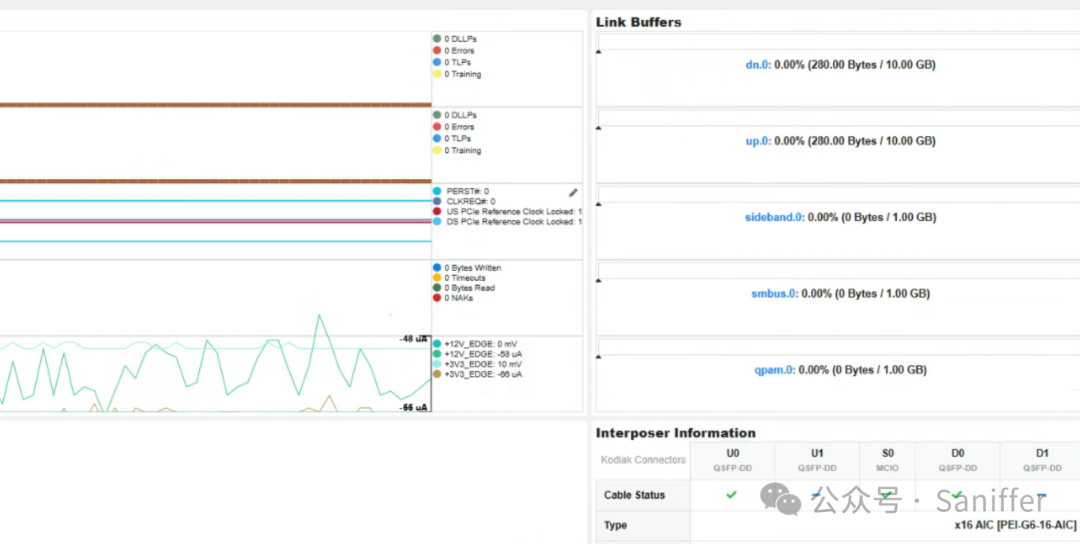

我们经常看到很多设备,包括示波器,PCIe协议分析仪可以监控sideband信号,包括RefClk信号,参看下图为SerialTek PCIe 5.0和6.0协议分析仪监控RefClk以及PERST#信号的情况,实际上该SerialTek PCIe分析仪可以监控所有的sideband信号,包括图片上显示的12V/3.3V功耗(电压、电流)。

那么我们今天来看一下pcie插卡上面的reference clock的信号,电压,频率,差分信号等等,如何来测试这个信号?如果该信号不完全符合标准的电压等要求,对于下游downstream pcie device有什么影响等。

一、PCIe 里的 reference clock 到底干什么?

PCIe 链路本身是高速差分串行,每条 Lane 自己嵌入时钟 (8b/10b 或 128b/130b 编码后由 CDR 恢复),传输数据时并不依赖外部 refclk。

但 refclk 主要给两类东西用:

-

给 SerDes PLL 提供基准频率(大多数实现是这样):

-

100 MHz 差分时钟进 PHY,

-

PHY 内部分频/倍频 → 2.5/5/8/16/32 GT/s 等 Line Rate。

-

-

给控制逻辑 / LTSSM / 计时器等数字部分提供主时钟(或用于生成这些时钟)。

早期 PCIe 1.0/2.0 基本都是系统级共享时钟 (Common Refclk, SRIS=0):

-

RC(Root Complex)和所有 Endpoints 共享一套 100 MHz refclk;

-

插槽上的 CLK+/- 就是 root 端 clock buffer 扇出的一路。

后来 PCIe 3.0+ 之后多了 SRIS/SRNS(独立时钟) 模式:

-

每个端点可以用自己的 100 MHz 或其他频率本振(通过 SSC 等保持频偏在规范内);

-

对 refclk 的布线拓扑要求就不一样了。

你问的是"插卡上的 reference clock 信号、电压、差分信号,以及如何连接到对端",主要就是指 Common Refclk 模式下 slot 上那对 100 MHz 差分时钟 CLK+ / CLK-。

二、典型电气参数:频率、电压、差分特性

1. 频率

-

名义频率:100 MHz

-

允许偏差:±300 ppm(具体看 PCIe Base Spec 和 CEM Spec,带 SSC 时会有额外的调制范围要求)。

-

很多系统会加 SSC(Spread Spectrum Clocking):

-

一般是 −0.5% 左右下展宽调制,

-

减少 EMI,但会让接收端的 CDR / PLL 设计稍微复杂一点。

-

2. 信号制式

常见几种:

-

HCSL(High-Speed Current Steering Logic)

-

这是最典型的 PCIe refclk 格式。

-

端接通常是每根线对地 50 Ω(或等效)+ 电流源驱动。

-

差分摆幅大约 0.7--1.0 Vpp-diff 量级(不同 clock buffer 会有略微差异)。

-

-

LVDS / LVPECL / CML 等

-

某些板级会把 HCSL 转换为 LVDS/LVPECL 等再送往芯片。

-

CEM 规范更多针对 HCSL;板内可以做电平转换,但要保证接收端 sees 一个满足规范的差分时钟。

-

在插槽层面,你可以简单理解为:

PCIe slot 上的 CLK+ / CLK- 是一对 100 MHz 差分 clock,逻辑上类似 HCSL/LVDS 差分时钟,摆幅在几百 mV 到 1 Vpp-diff 之间。

3. 差分信号的关键参数

对 refclk 这种 低数据率(100 MHz)但对抖动敏感的信号,主要关心:

-

差分摆幅 Vpp-diff(太小会导致接收器接收门限不够,太大则可能导致过冲 / EMI 问题);

-

共模范围(RC/EP PHY 输入的 common-mode 范围,一般几百 mV 到 1.x V 左右);

-

上升/下降时间(slew rate,需要足够快以保证有效时钟边沿,但不能过快以免产生过多 EMI 和反射);

-

周期抖动 / 周期--周期抖动 / 积分抖动(RMS、peak-to-peak 等)

- 抖动直接决定 PLL 能否锁定,以及 SerDes CDR 的容差 margin;

-

对称性 / 占空比(一般 50% ± 5--10%)。

三、拓扑:refclk 是怎么"从 upstream 传到 downstream 的"?

这里容易被概念混淆。简单区分:

-

数据链路方向 (upstream/downstream):

-

Downstream Port:在 RC、Switch 侧(比如 Root Port、Switch Downstream Port);

-

Upstream Port:在 Endpoint / Switch Upstream 侧。

-

-

Refclk 拓扑

- 通常是 RC → 多路 clock buffer → 各个下游 slot / Endpoint。

也就是说:

refclk 从"更高层级"的 clock 源经过 buffer 扇出到每个 slot / 芯片, 并不是沿着 PCIe data lane 方向"上/下游传递"的信号。

典型几种情况:

-

主板 Common Clock

- CPU RC、PCH、PCIe Switch、插槽(x16/x8/x4 等)。

-

主板上有一个或多个 100 MHz clock generator;

-

经 buffer / fanout 芯片分成 N 路;

-

分别走差分线到各个:

-

独立时钟(SRIS/SRNS)

-

插卡自己有一个晶振/PLL 产生 100 MHz;

-

主板给自己的 RC/Root 另一个本振;

-

双方只要求频偏在规范允许范围内,链路仍能训练成功。

-

这种模式下,slot 上的 refclk 引脚可能空着,或定义为 SRIS。

-

-

Slot 级:

-

主板通过 slot 的 CLK+ / CLK- 把 refclk"送给"插卡,

-

插卡上 PHY/桥片再用这个 clock 做 PLL。

-

对于标准 CEM 插卡,如果是 Common Refclk 模式:

-

方向是:"主板 → 插卡",而不是"上游数据端口 → 下游数据端口"。

-

所以你可以记住一句话:

refclk 是 系统时钟拓扑 的一部分,不是 PCIe 上下行方向里的一员; 它的"方向"更多是 从 clock 发生器 → 各元件/插卡 的扇出,而不是从 upstream 端口到 downstream 端口。

四、工程上如何测试这对 refclk 差分信号?

1. 测什么?

通常至少要看:

-

波形与摆幅

-

差分 Vpp、单端振幅、共模电平;

-

上升/下降时间。

-

-

抖动

-

周期抖动 (Tj)、周期--周期抖动 (C--C jitter)、RMS Jitter;

-

积分抖动在指定带宽内(比如 12 kHz--20 MHz)。

-

-

频率与 SSC

-

实际频率(含 ppb / ppm 偏差);

-

是否存在 Spread Spectrum,折线/三角波形态、调制深度等。

-

-

信号完整性

-

眼图、过冲、下冲、反射;

-

拐角、阻抗不连续导致的 ringing;

-

差分对 skew(时序偏移)。

-

2. 用什么仪器?

-

示波器(带差分探头)

-

带宽 1 GHz 以上基本够看 100 MHz refclk 的波形和抖动;

-

使用 高阻抗差分探头,避免过多 load。

-

-

频谱仪 + 相位噪声分析(更严谨的 jitter / phase noise 测试)。

-

时钟/抖动分析仪(专用 clock jitter analyzer)。

在实践里,大多数板级 bring-up:

用 高带宽示波器 + 差分探头 就足够判断"是不是明显不对劲"。

3. 在什么地方测?

-

如果想看主板输出质量:

-

在 slot 就近的 test pad / 0 Ω 电阻位置测量;

-

或在 refclk buffer 的输出脚附近测。

-

-

想看插卡上"看到的 clock":

- 插卡上如果有 refclk input net,可以在其 series 终端电阻 / 预留测试点处测。

注意:

不要直接撬开芯片脚焊盘测,一是危险,二是探头电容太大,可能改变信号形态。

五、refclk 不满足规范时,对 downstream PCIe 设备有什么影响?

从"轻微问题"到"致命问题",大致是这一串:

1. 轻微超差:频偏 / 抖动稍大

-

可能表现为:

-

上电偶尔训练时间变长;

-

链路可以 up,但在高温/低温或电压边界条件下不稳定;

-

用协议分析仪看,error counter / replay 增多。

-

-

对下游 Endpoint 来说:

-

PLL 锁定 margin 变小;

-

CDR 层面的 jitter budget 被压缩,导致对数据抖动不够"宽容"。

-

2. 摆幅太小 / 共模不对 / 边沿太缓慢

-

接收端可能:

-

PLL 根本锁不上 refclk → LTSSM 停留在 Detect/ Polling 反复;

-

上电时序极不稳定,有时上,有时不上。

-

-

在 BIOS 或 OS 里可能看到:

-

根本枚举不到这条 PCIe 设备;

-

或者频繁 link training failed / surprise down。

-

3. 抖动太大 / SSC 异常 / 时钟形态畸变

-

即使能锁定,也会:

-

Link Training 失败率提高;

-

训练出错,降速 / 降宽;

-

high BER(高 bit error rate),触发大量重传,性能严重下滑。

-

你可以把 refclk 看成:

SerDes PLL/PHY 稳定性的"地基" 地基不稳 → 上面的 2.5G/5G/8G/16G/32G 数据链路,迟早会出问题。

4. 系统级奇怪 Bug

在一些大系统上,你会看到这种现象:

-

单板测试没问题,多板安装在大型 backplane 后,某些槽位的设备:

-

偶尔不上电;

-

仅在某个插槽不稳定;

-

只要换到另一个槽位就好。

-

很多时候,问题根源就是某些槽位的 refclk 布线更长 / 负载更重 / 反射更严重,边缘槽位的 refclk 质量最差 → 某些 Endpoint PHY 对 refclk 质量更敏感,表现为"与型号相关的插槽问题"。

六、工程角度的小建议

-

设计/调试阶段:把 refclk 当成 high-priority 信号

-

差分走线等长、阻抗控制、尽量少换层;

-

远离强干扰源(电源 FET、DC-DC 开关节点等)。

-

-

确认 Clock Tree 设计

-

Clock generator → buffer → fanout → slot / chip 的拓扑是否清晰;

-

Buffer 输出电平模式(HCSL / LVDS)与接收端输入匹配。

-

-

多板 / 不同长度 slot

-

对最差路径(最长那条 refclk 差分线)做 SI 仿真 & 实际测量;

-

看 worst case 抖动、摆幅、边沿。

-

-

如果你在做测试工具 / 协议分析仪 / 插卡类产品

-

允许更大的摆幅区间和共模范围;

-

对抖动的容差留更大 margin;

-

必要时考虑板上 re-clock / jitter cleaner 芯片。

-

你的卡往往会插在"各种非常糟糕的主板"上 →

-

自己板上的 refclk 接收要尽量"robust":

-