bash

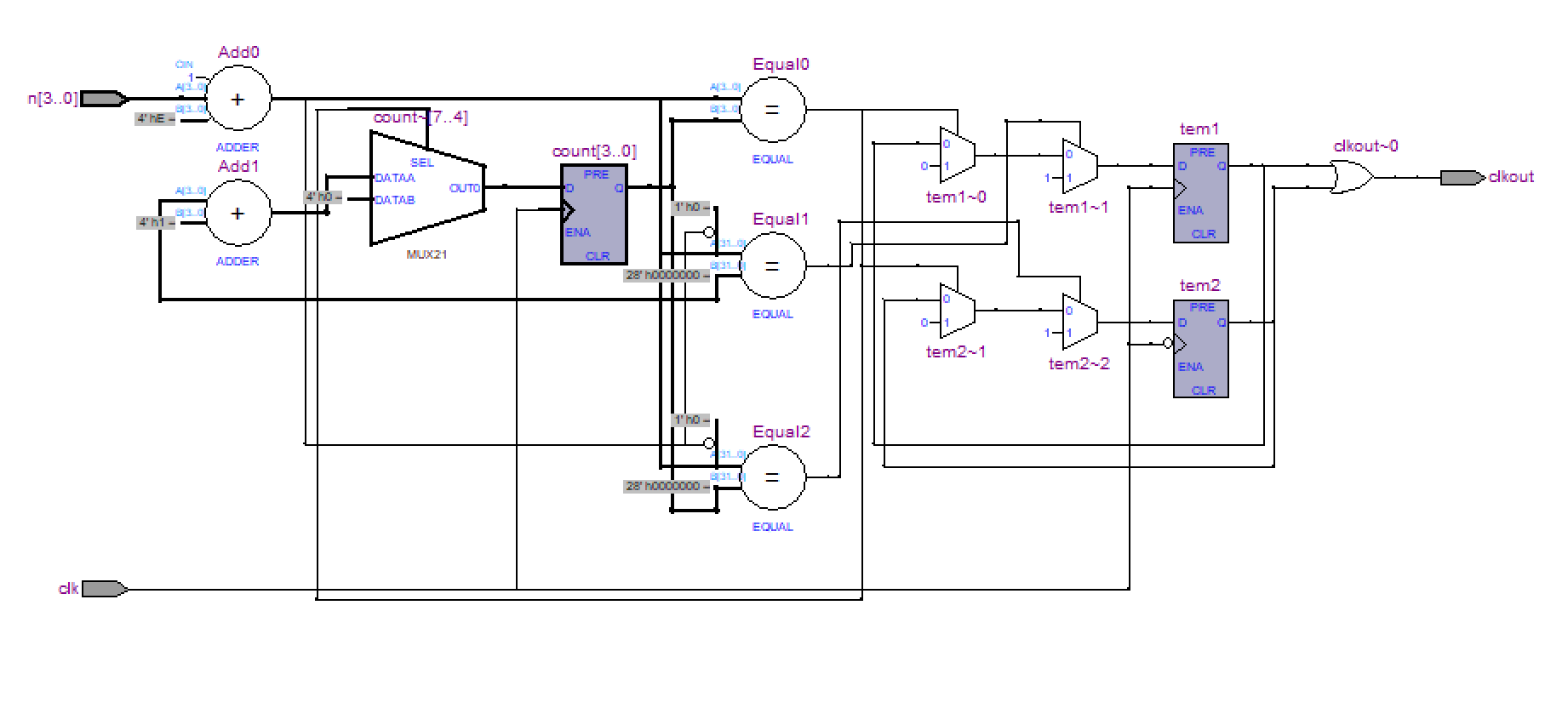

module divn(

input clk,

input [3:0]n,//n is an odd number less than 16

output clkout

);//n frequency division

reg [3:0] count;

reg tem1,tem2;

always@(posedge clk)begin

if(count==n-1'd1)count<=0;

else count<=count+1'd1;

end

always@(posedge clk)begin

if(count==(n-1'd1)/2)tem1<=1'd1;

else if(count==(n-1'd1))tem1<=1'd0;

else tem1<=tem1;

end

always@(negedge clk)begin

if(count==(n-1'd1)/2)tem2<=1'd1;

else if(count==(n-1'd1))tem2<=1'd0;

else tem2<=tem2;

end

assign clkout=tem1||tem2;

endmodule

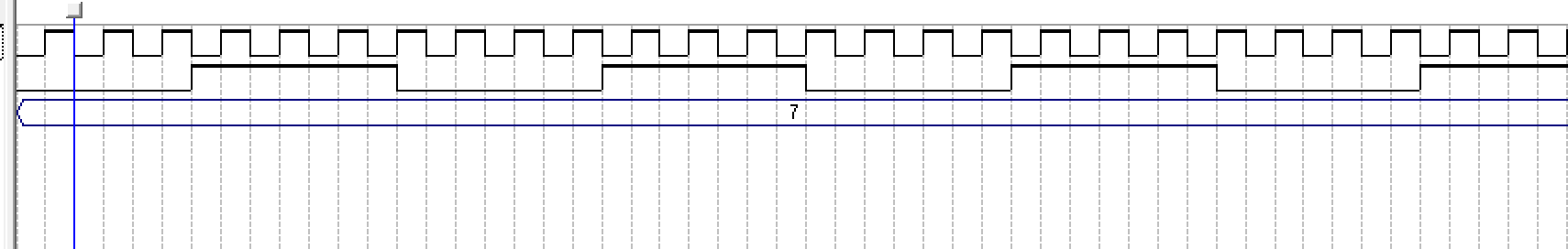

奇数分频器设计总结(50%占空比)

一、核心问题

-

奇数N无法直接实现50%占空比(N/2非整数)

-

单边沿触发只能做到近似占空比

二、解决方案

双边沿组合法:

-

主计数器:模N计数(0到N-1)

-

上升沿信号:在计数到(N-1)/2时置1,N-1时清0

-

下降沿信号:相同逻辑,但下降沿触发

-

输出组合:两信号相或(OR)

三、关键公式

-

分频比 = N(奇数)

-

高电平位置:count ≥ (N-1)/2 且 < N-1

-

单信号占空比:(N-1)/2N → 非50%

-

组合后占空比:50%

本质:用两个相位错开的非对称信号,通过逻辑组合实现对称输出。