背景:最近在调试瑞萨 CCE4503 IOLINK芯片,期间调试遇到了一些串口相关的基础知识,各家对串口底层的数据位停止位的描述不一致,故在此作笔记一篇。

一、IOLINK通信规定,串口配置模式为8bit数据位+1bit偶校验位

1、ST家的芯片配置时,USART_InitStructure.USART_WordLength = USART_WordLength_9b;

此处的9bit包含了8bit的数据位与1bit校验位

USART_InitTypeDef USART_InitStructure;

RCC_APB1PeriphClockCmd(RCC_APB1Periph_UART4, ENABLE);

USART_InitStructure.USART_BaudRate = 115200;

USART_InitStructure.USART_WordLength = USART_WordLength_9b;

USART_InitStructure.USART_StopBits = USART_StopBits_1;

USART_InitStructure.USART_Parity = USART_Parity_Even;

//USART_Parity_No USART_Parity_Even USART_Parity_Odd

USART_InitStructure.USART_HardwareFlowControl = USART_HardwareFlowControl_None;

USART_InitStructure.USART_Mode = USART_Mode_Rx | USART_Mode_Tx;

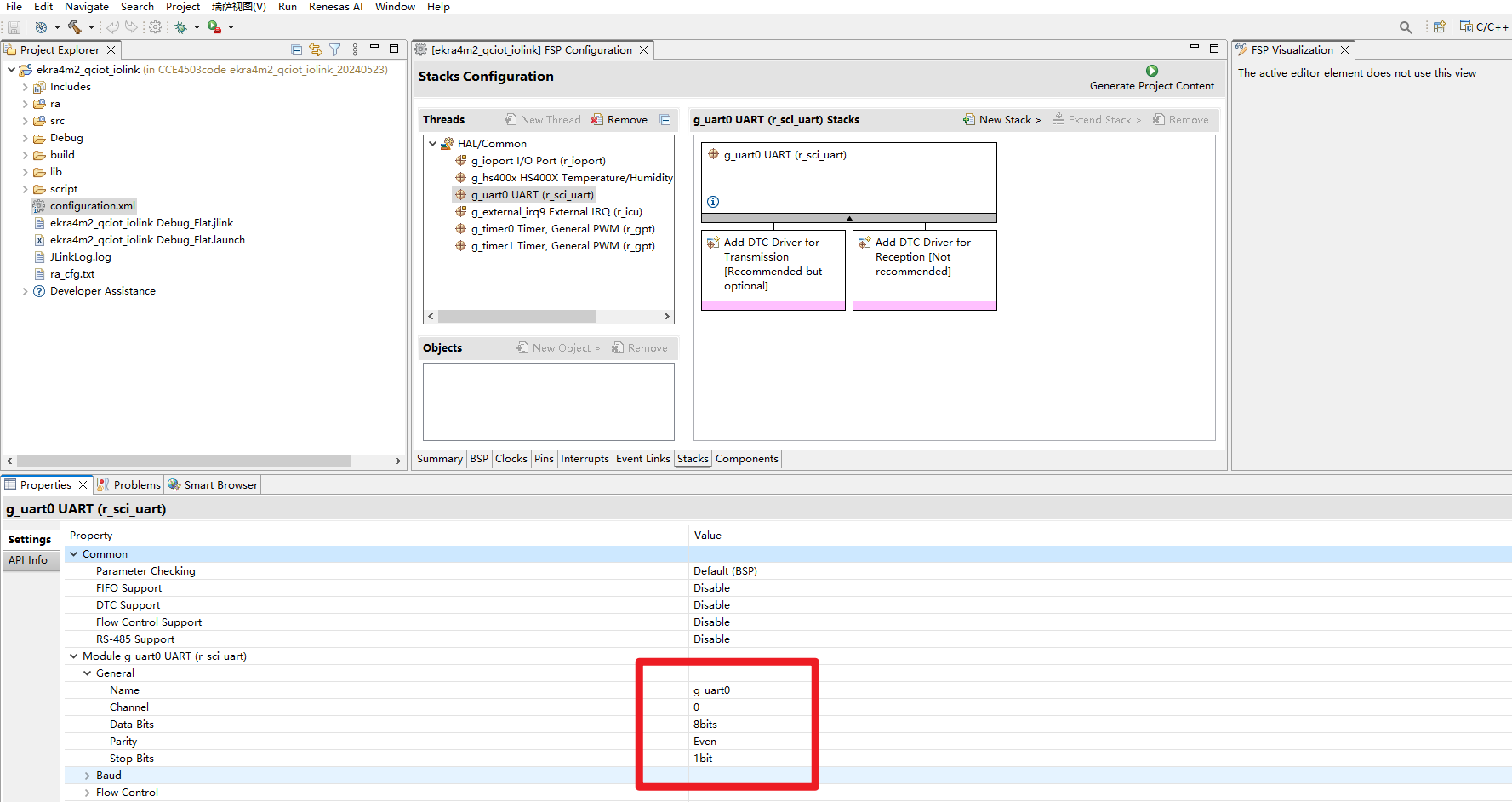

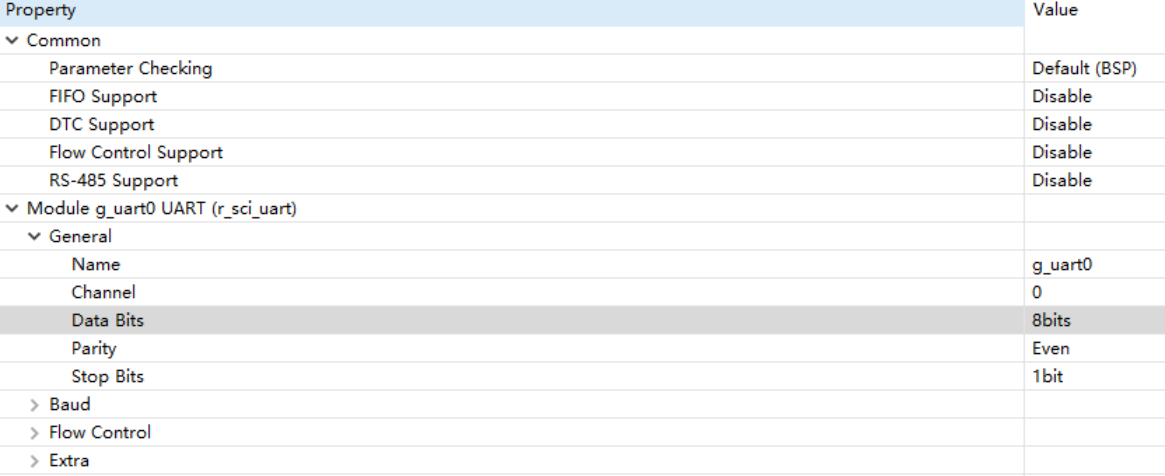

USART_Init(UART4, &USART_InitStructure);2、Renesas 旗下E² stidio配置界面,此处的数据位与校验位分开描述,与ST配置时不一样,避免混淆

3、调试过程中用到了逻辑分析仪,DSView对数据位、校验位描述时与Renesas一致,也是分开描述

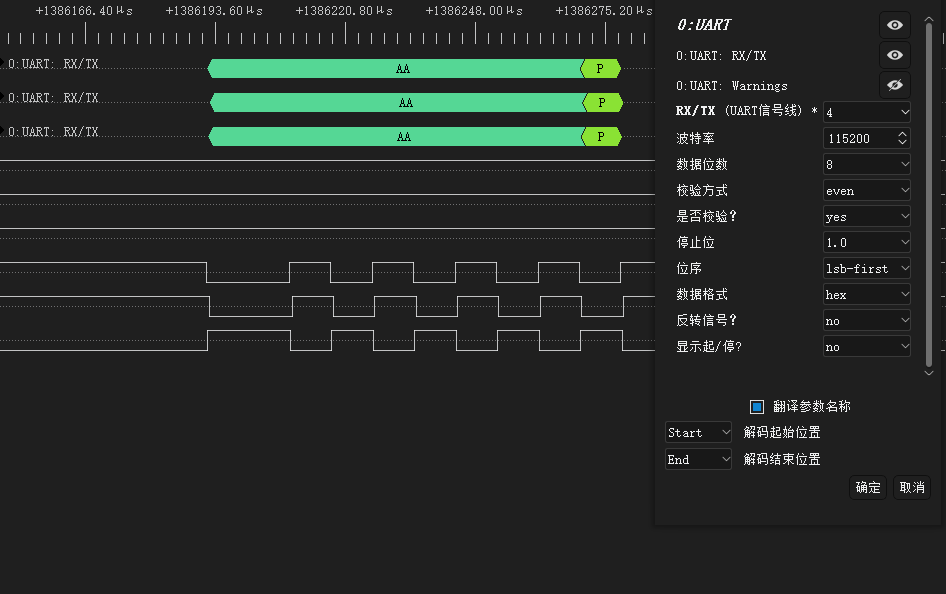

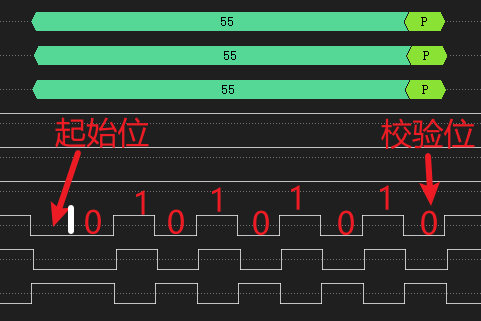

二、关于lsb-first与msb-first与实际波形关联关系

0xAA:10101010 0x55:01010101

lsb-first下代表0xAA

msb-first下代表0x55

其实lsb-first优先传输低位数据,msb-first优先传输高位数据,这也阐释了为什么波形一样,数据不一样,而我们ST芯片内部一般都为lsb-first。

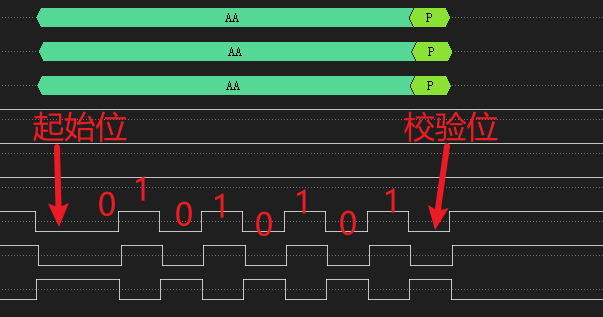

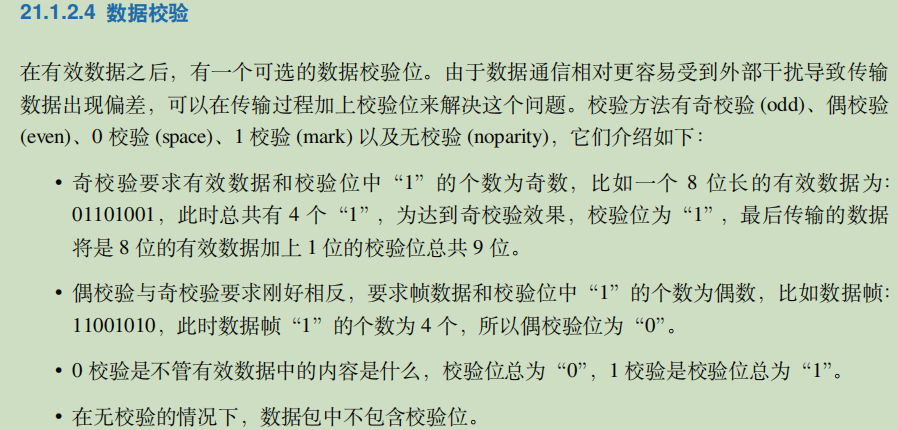

三、关于串口奇偶校验位数据计算

简单来讲,此帧中,1的个数为偶数个,偶检验下检验位为0,奇校验下校验为1;1的个数为奇数个,偶检验下检验位为1,奇校验下校验为0;

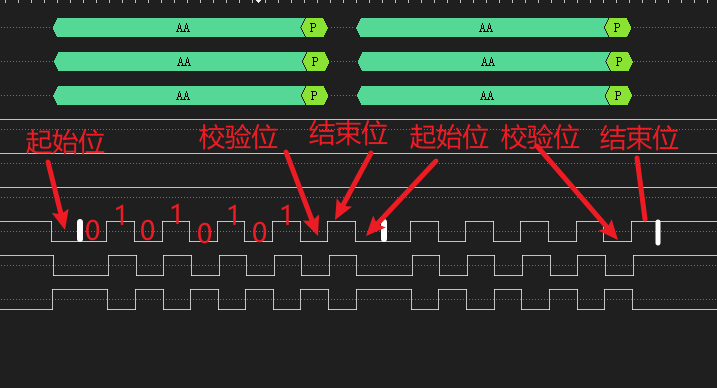

四、补充第二节波形无对停止位标明

总结:当前进度硬件基础通信基本已完成,协议栈还需自己搭建,以参考Renesas DEMO代码的方式去了解与移植IOLINK通信逻辑方法不可取,时间周期太长,移植后因不熟悉代码与握手逻辑调试时会很吃力,对于第一次接触IOLINK通信以这种方式想必会事倍功半,优先找到相关文章书籍,自己搭建握手逻辑。