本文主要交流设计思路,在本博客已给出相关博文一百多篇,希望对初学者有用。注意这里只是抛砖引玉,切莫认为参考这就可以完成商用IP设计。若有NVME或RDMA 产品及项目需求,请看B站视频后联系。

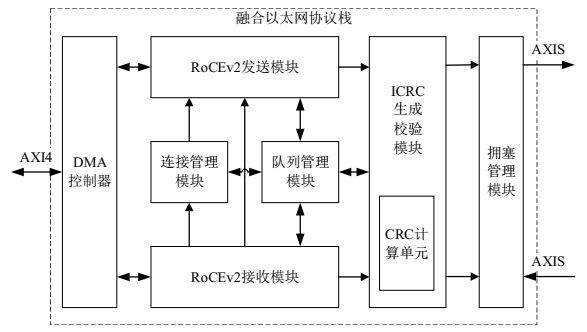

连接管理模块负责管理 RoCE v2 高速数据传输系统与主机之间的连接和断开。

在 RoCE v2 中,有两种建立连接的方式,分别是基于 CM API 的 QP 间建链和基于Socket API 的 QP 间建链。CM API 是一种建立在 Infiniband/RoCE 协议基础之上的通信管理协议;Socket 是基于 TCP/IP 协议的一个中间层,其建链过程需要两个网络节点先建立 TCP/IP 连接,然后通过该连接来交换双方 QP 信息。由于本IP使用 RoCEv2 协议,其是一种基于 UDP/IP 的传输协议。因此,使用 CM API 进行建链的方式可以避免搭建 TCP/IP 协议栈,从而节约系统资源并提高建链效率。

在 CM API 中,每条 CM 指令由多个字段组成,不同指令的包长度及对应字段的含义也不相同。因此当系统控制模块发起建链或断链请求时,连接管理模块将对应寄存器中的信息整合为CM 包,并将该数据包写入发送队列中。在接收到完成队列中的条目后,连接管理模块提取其中的信息并执行指令完成流程。

队列管理模块负责 RoCE v2 发送队列、接收队列和完成队列的创建、存储、仲裁,以及 RoCE v2 指令的提交和完成机制。RoCE v2 队列对是实现 RoCE v2 指令提交与完成机制的核心组件,其队列数量、队列深度和仲裁方式将直接影响数据传输性能。为了适应不同的应用场景,队列管理模块将队列存储与队列指令控制分离,实现了运行时的动态队列配置功能,以更少的资源消耗实现多场景下更优的性能表现。

RoCE v2 发送模块及 RoCE v2 接收模块则负责发送或接收 RoCE v2 数据包。其中,RoCE v2 发送模块从队列管理模块中提取用户指令并将其转换为 RoCE v2 包,然后发送到远程主机。对于包含数据的 RoCE v2 包,RoCE v2 发送模块将同时与 DMA控制器进行数据交换,从系统存储中读取数据后发送到远程主机。同样的,RoCE v2接收模块接收并解析 RoCE v2 数据包,而后根据包类型与 DMA 控制器进行数据交换,进行数据读取或写入操作。同时其也将包信息发送到队列管理模块以实现指令释放。

ICRC 生成校验模块负责 RoCE v2 包 ICRC 的计算、插入、校验和删除工作。其中,对于即将发送的 RoCE v2 包,ICRC 生成校验模块通过内置的 CRC 计算单元计算 ICRC 并插入到包尾部。此模块同样负责对接收到的 RoCE v2 包进行 ICRC 校验,若校验通过,该包进入 RoCE v2 接收模块;若校验未通过,则该包由队列管理模块进行丢弃。

拥塞管理模块采用 DCQCN 算法进行网络拥塞的监测及处理,其由通知单元和响应单元组成。通知单元检测到报文 ECN 标志位有效时,将其转换为 CNP 包反馈给发送方以降低速度。而响应单元收到 CNP 包后降速,未收到时则升速。上述功能仅在含交换机的多主机连接链路中生效。

DMA 控制器则负责对 RoCE v2 发送模块和 RoCE v2 接收模块的数据请求进行仲裁,并将这些请求转换为 AXI4 总线请求,与系统内存储进行交互。DMA 控制器支持突发传输和 Outstanding 功能,以进一步提高数据吞吐量。

B站已给出相关性能的视频,如想进一步了解,请搜索B站用户:专注与守望