(以下内容全部来自上述课程)

目录

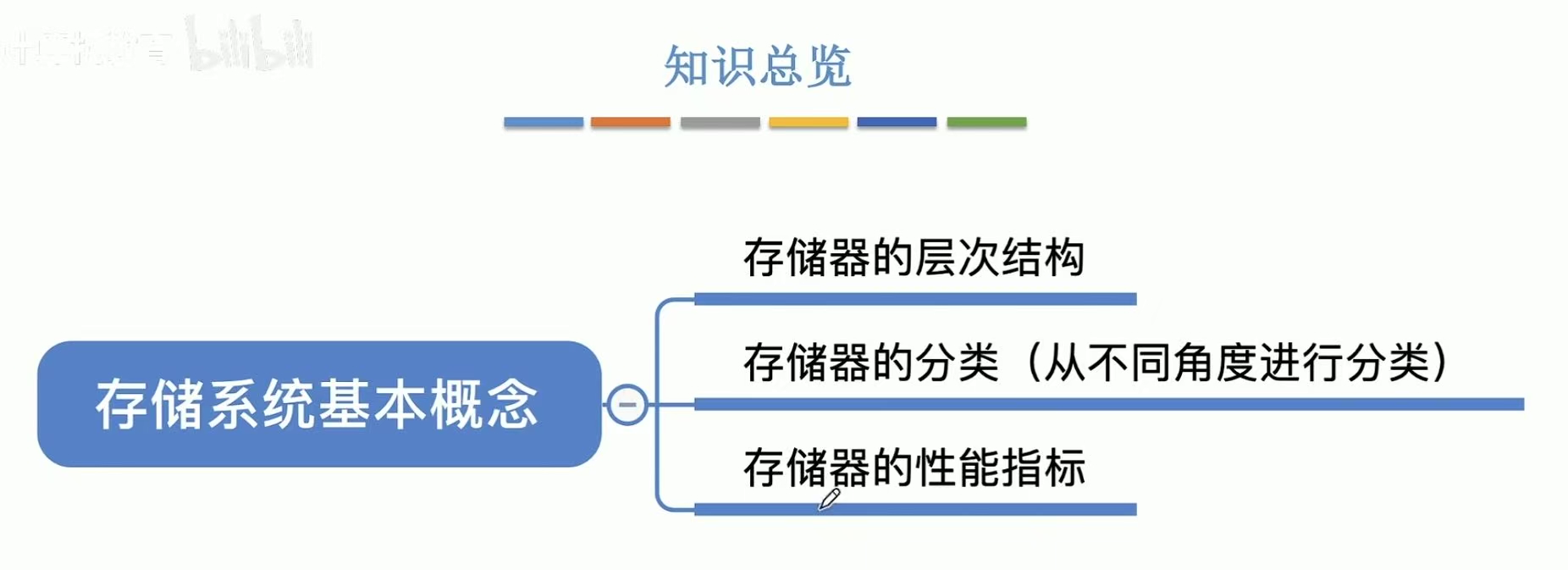

- 存储系统基本概念

-

- [1. 层次结构](#1. 层次结构)

- [2. 分类](#2. 分类)

- [3. 性能指标](#3. 性能指标)

- [4. 小结](#4. 小结)

- 主存储器的基本组成

-

- [1. 半导体元件的原理](#1. 半导体元件的原理)

- [2. 存储器芯片的基本原理](#2. 存储器芯片的基本原理)

- [3. 寻址](#3. 寻址)

- [4. 小结](#4. 小结)

- DRAM和SRAM

-

- [1. 特性差异](#1. 特性差异)

- [2. DRAM的刷新](#2. DRAM的刷新)

- [3. DRAM的地址线复用技术](#3. DRAM的地址线复用技术)

- [4. 小结](#4. 小结)

- ROM

- 双端RAM和多模块存储器

-

- [1. 双端口RAM(了解)](#1. 双端口RAM(了解))

- [2. 多体并行存储器](#2. 多体并行存储器)

- [3. 小结](#3. 小结)

- [4. 拓展](#4. 拓展)

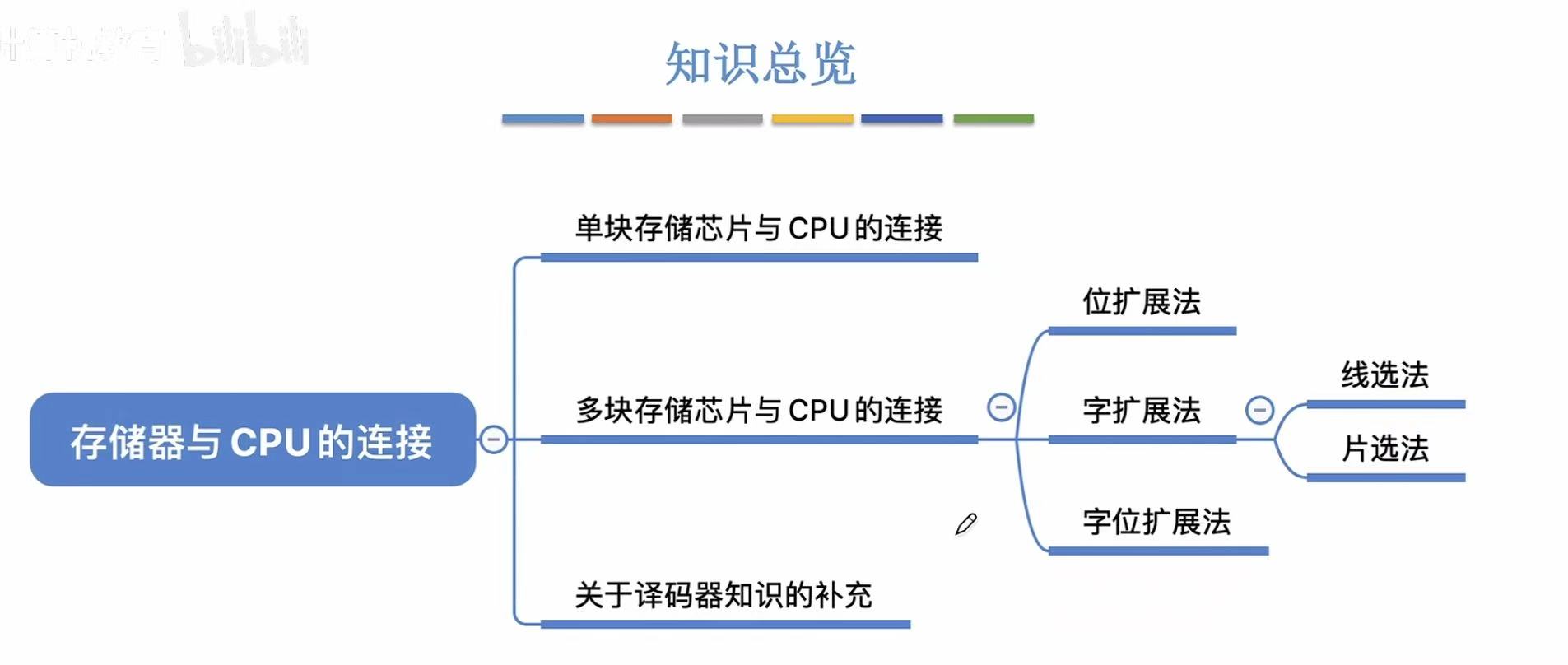

- 主存储器与CPU的连接

-

- [1. 前言](#1. 前言)

- [1. 位扩展](#1. 位扩展)

- [2. 字扩展](#2. 字扩展)

- [4. 字位扩展](#4. 字位扩展)

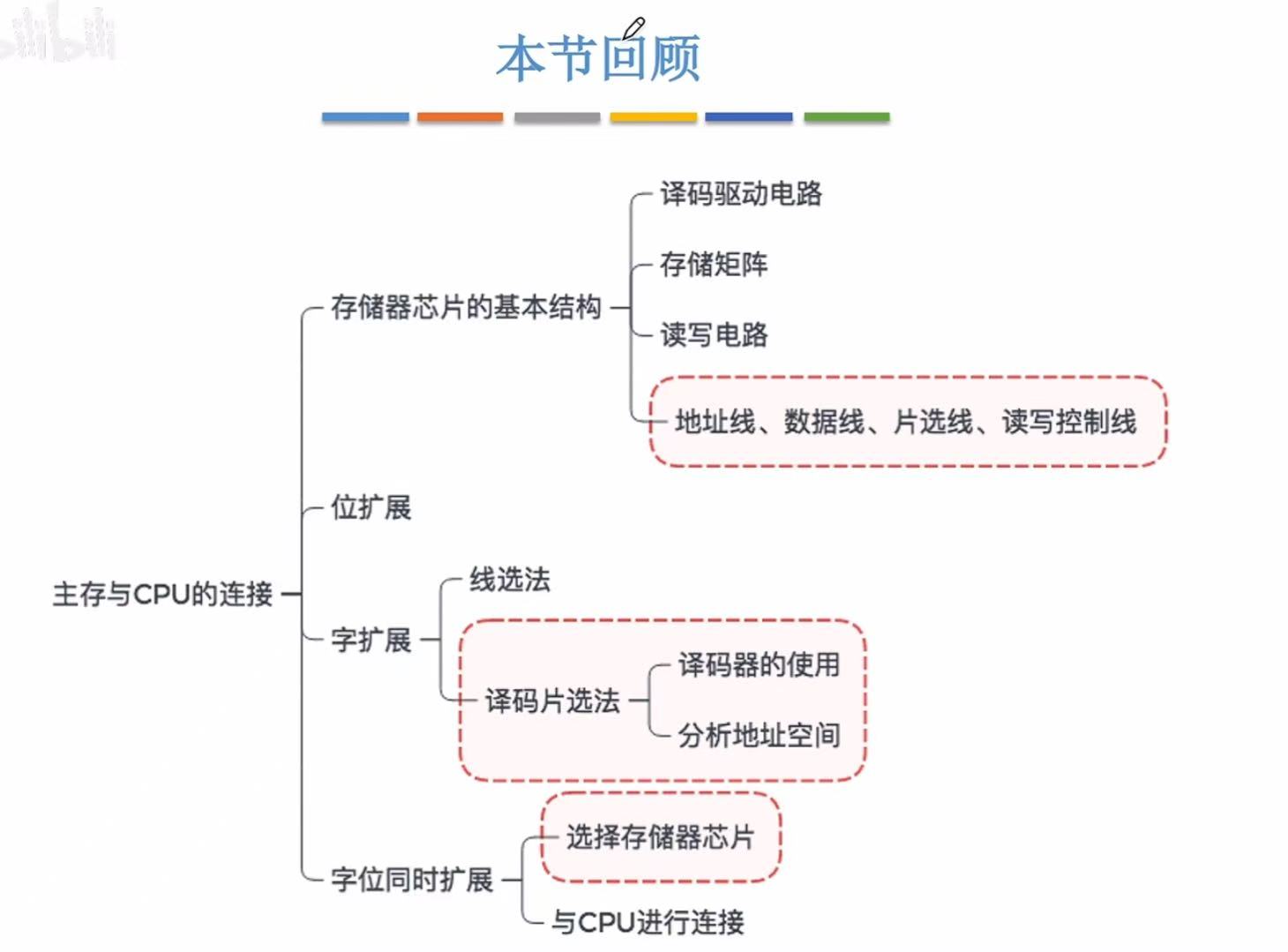

- [5. 小结](#5. 小结)

- [6. 补充-译码器](#6. 补充-译码器)

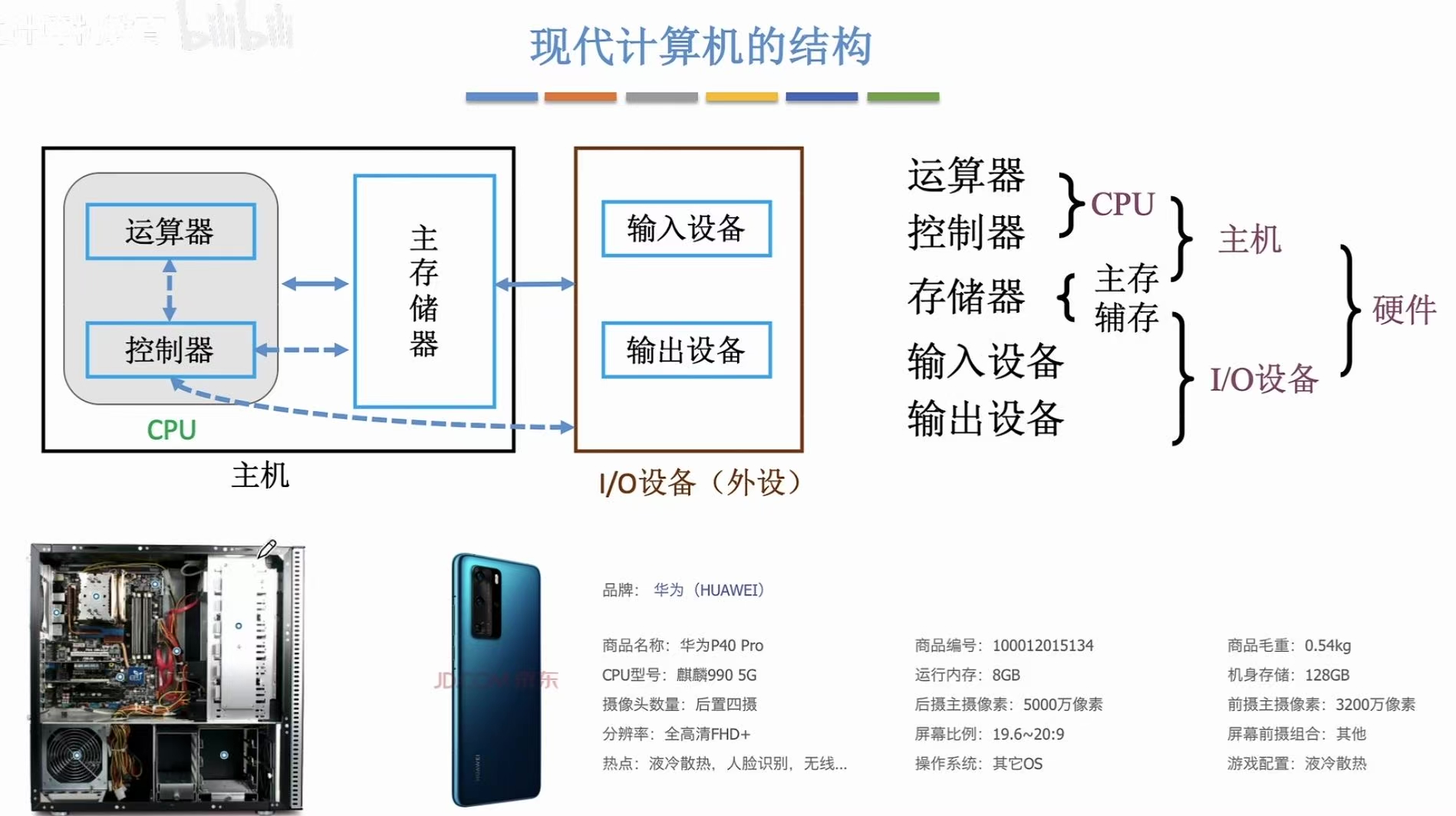

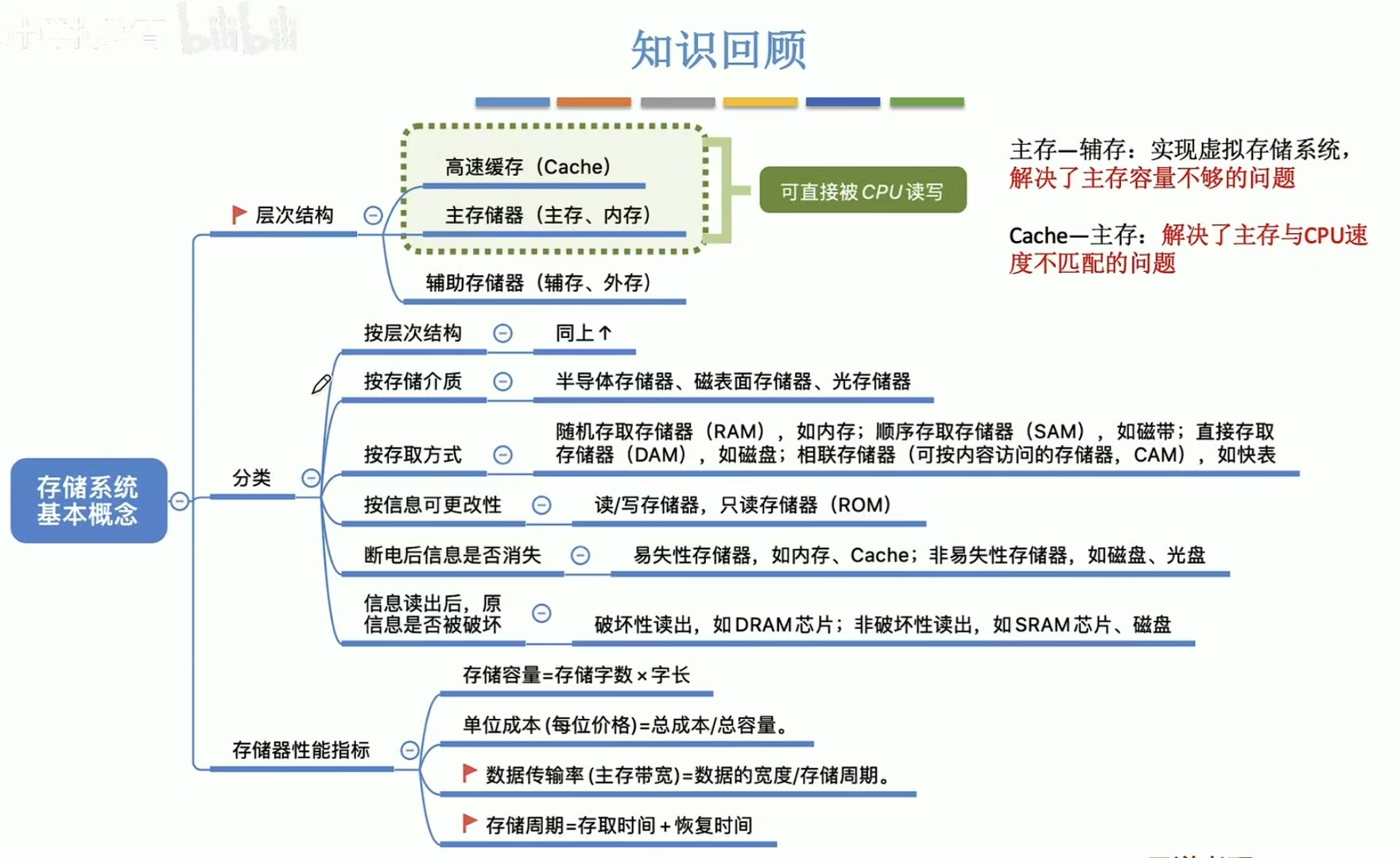

存储系统基本概念

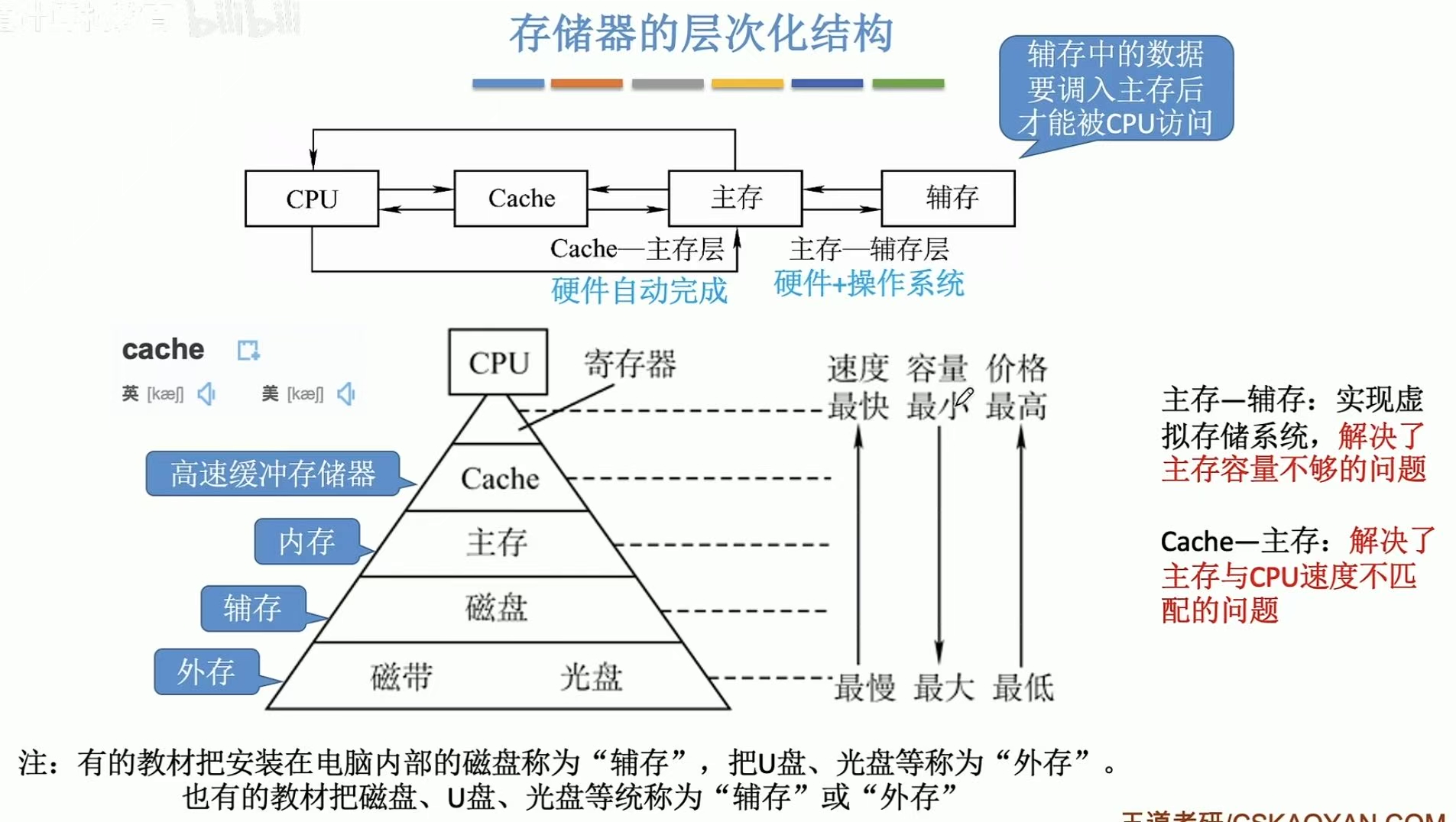

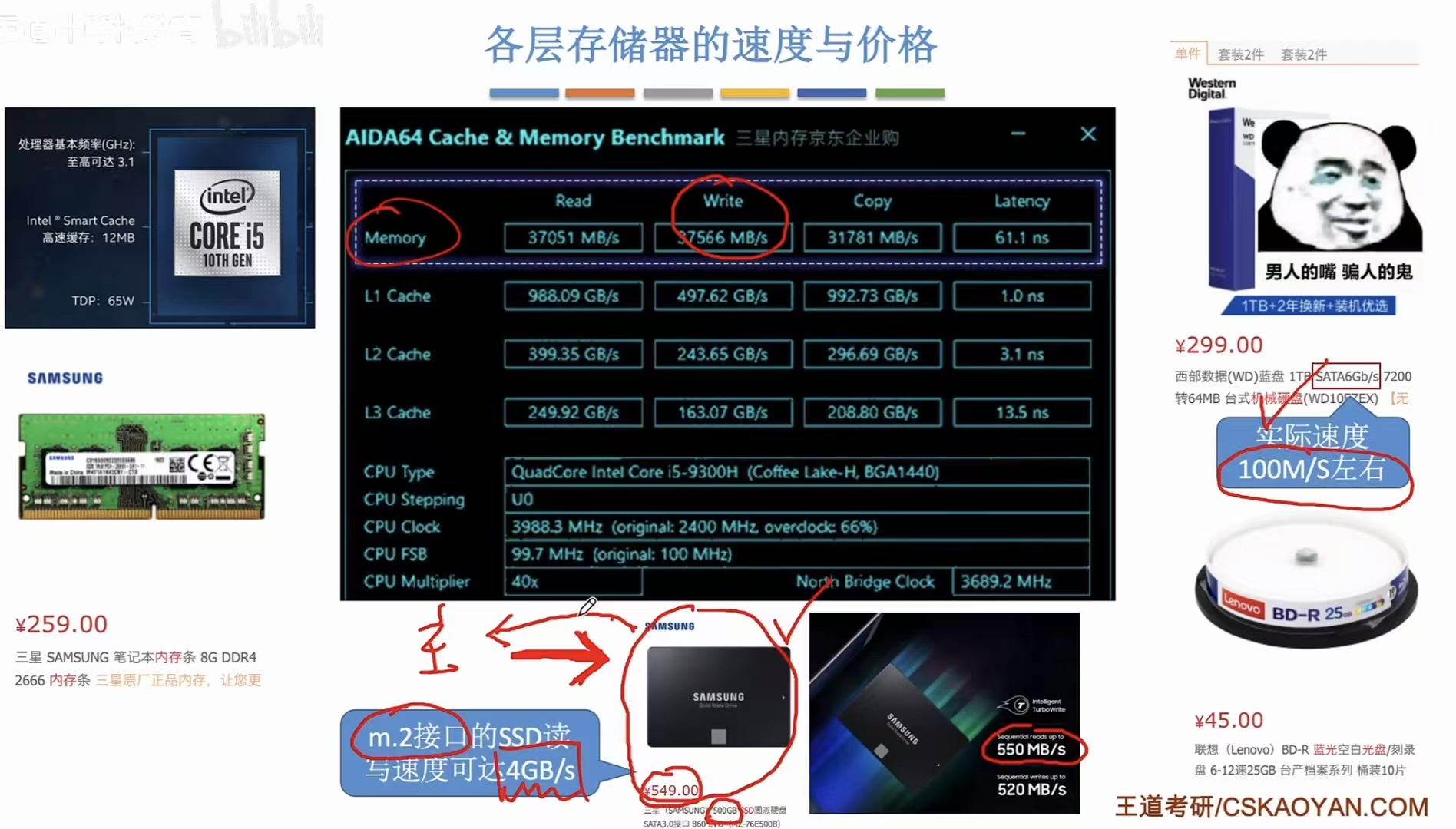

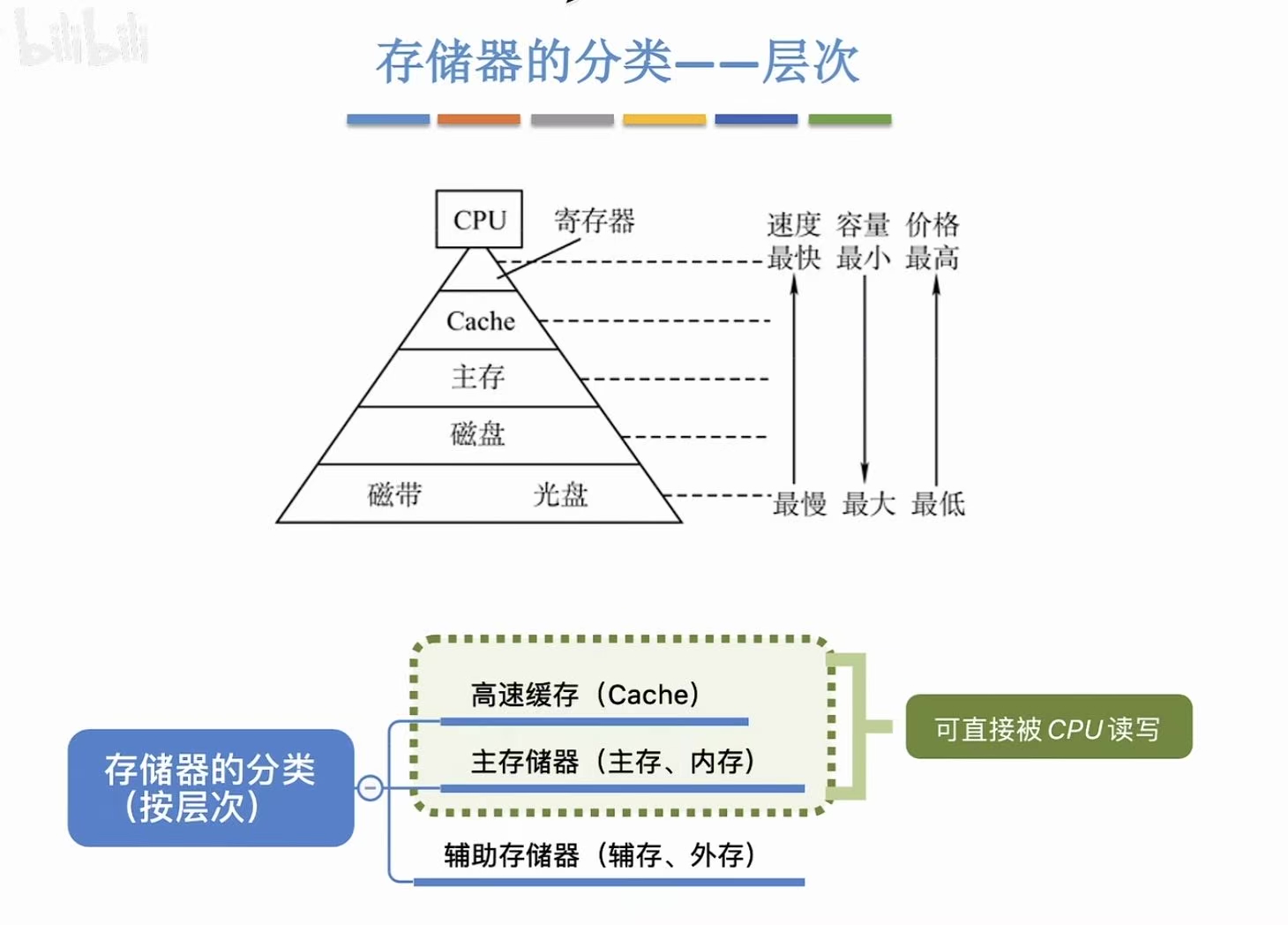

1. 层次结构

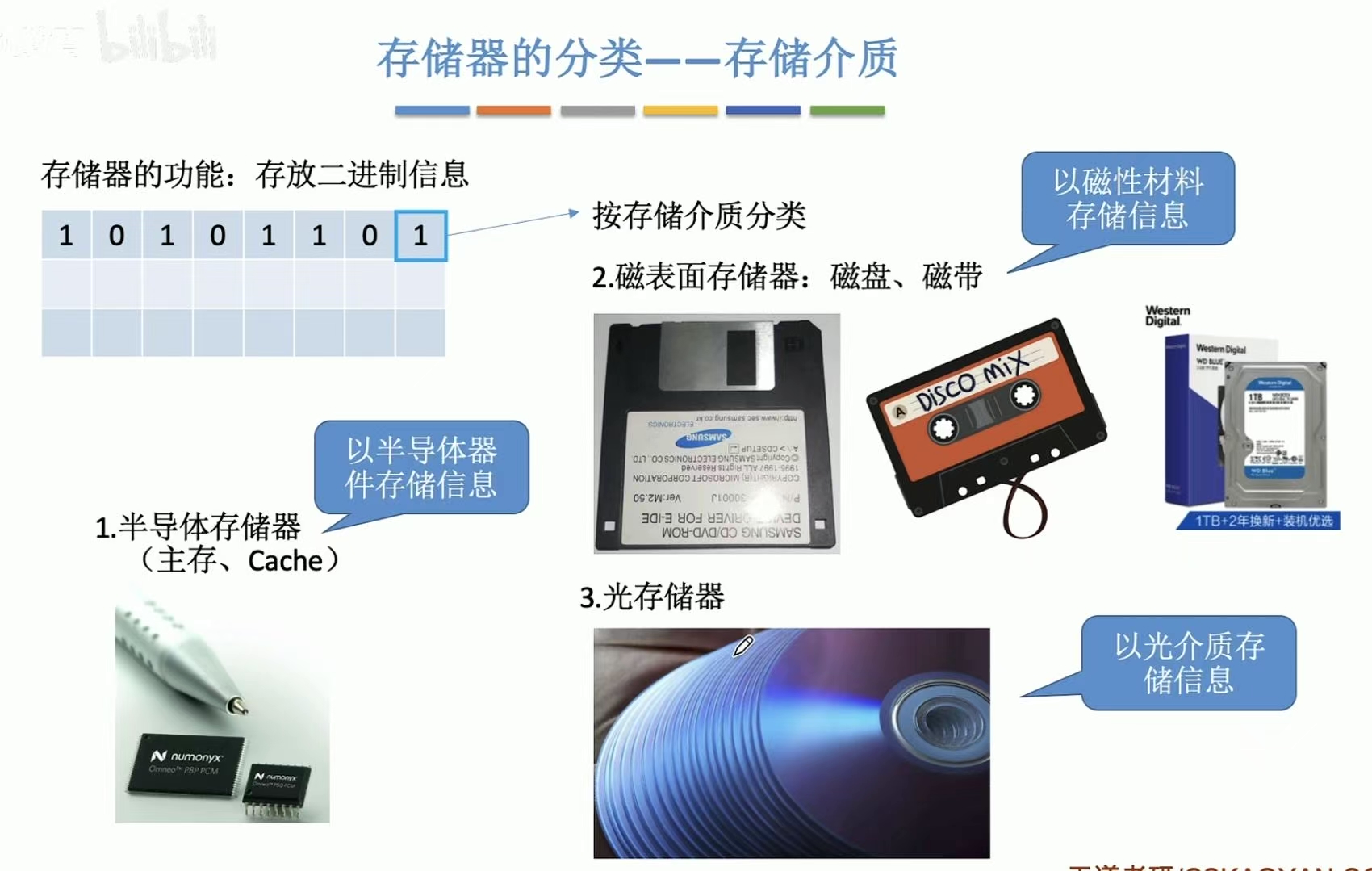

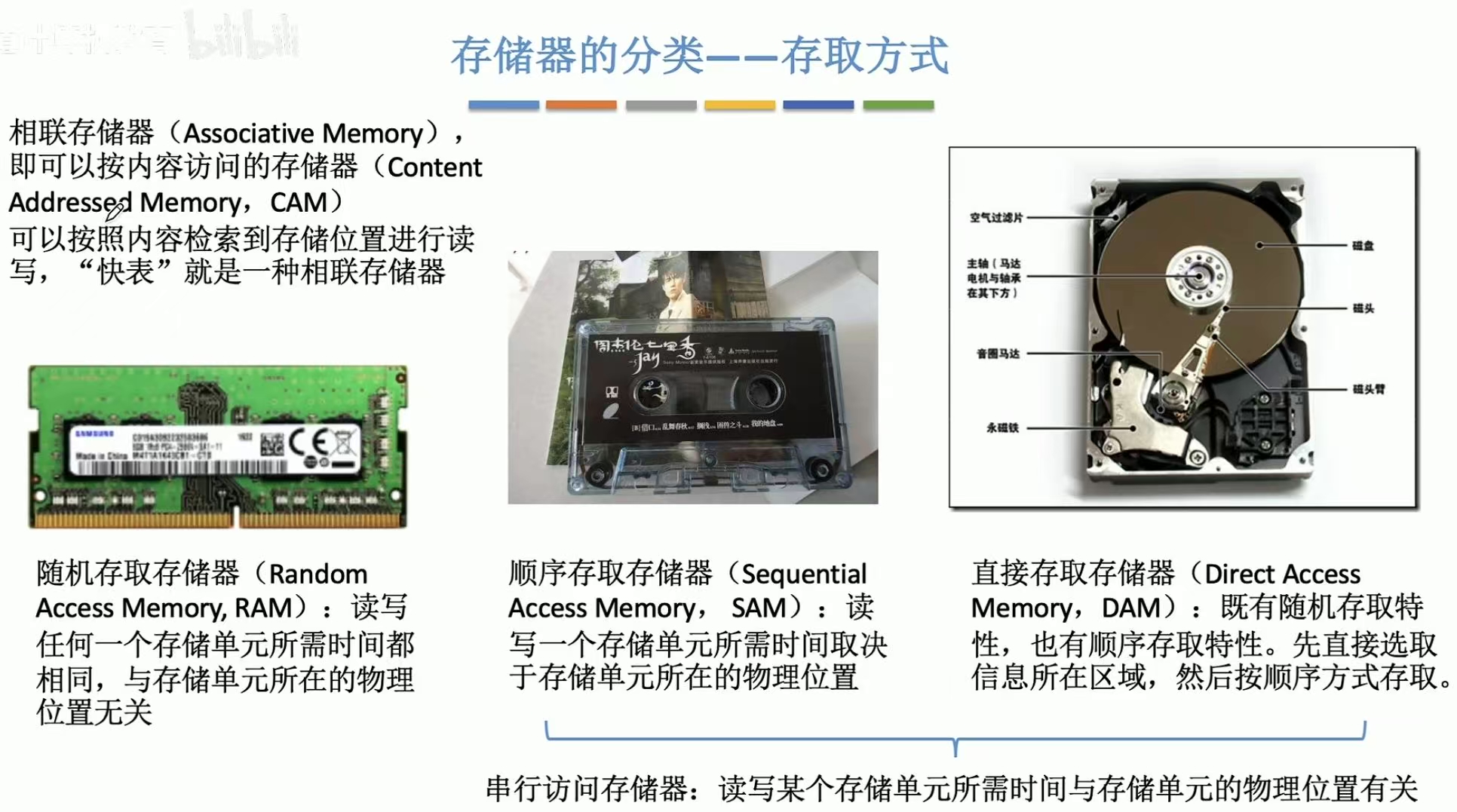

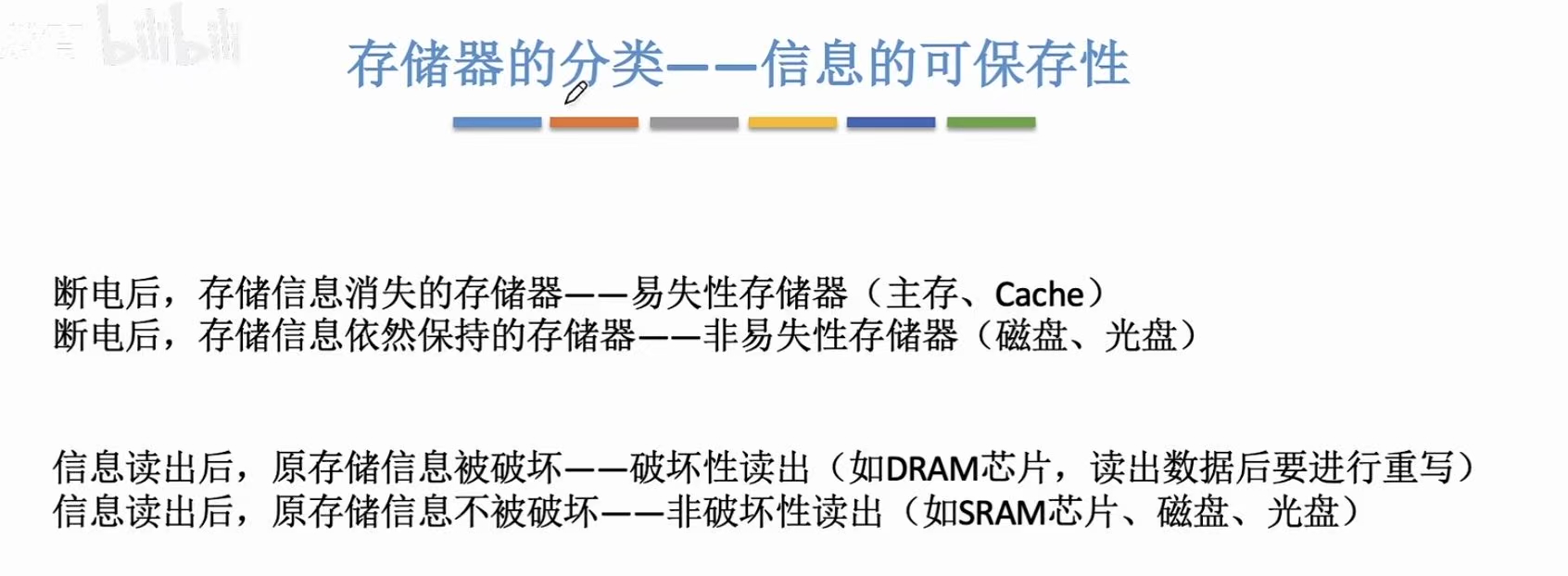

2. 分类

顺序存取存储器:例如磁带,想听哪句歌词只能从头慢慢放。

直接存取存储器:例如唱片,可以拨动磁头,放到任意相放的位置。

串行访问存储器:顺序+直接

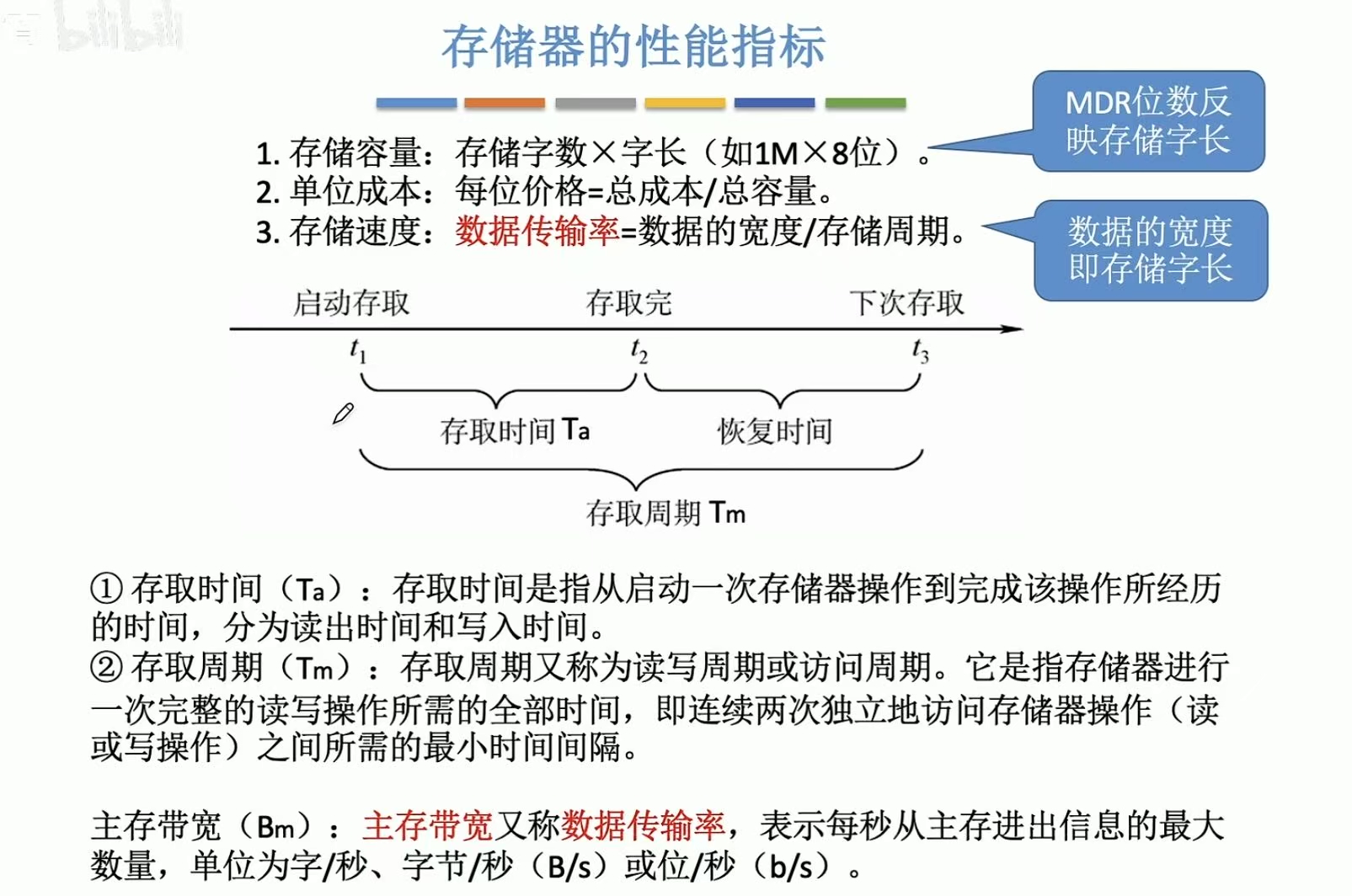

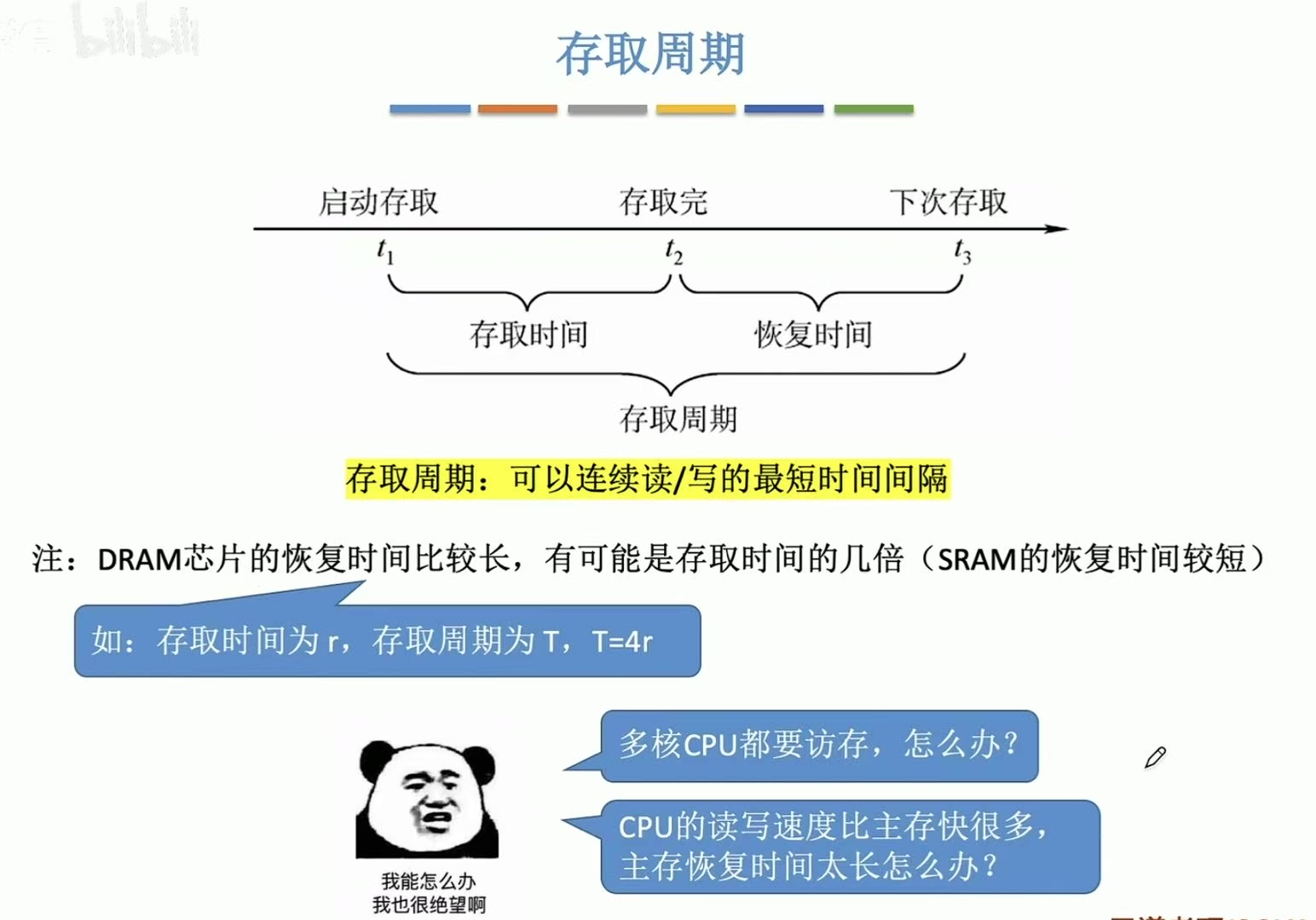

3. 性能指标

4. 小结

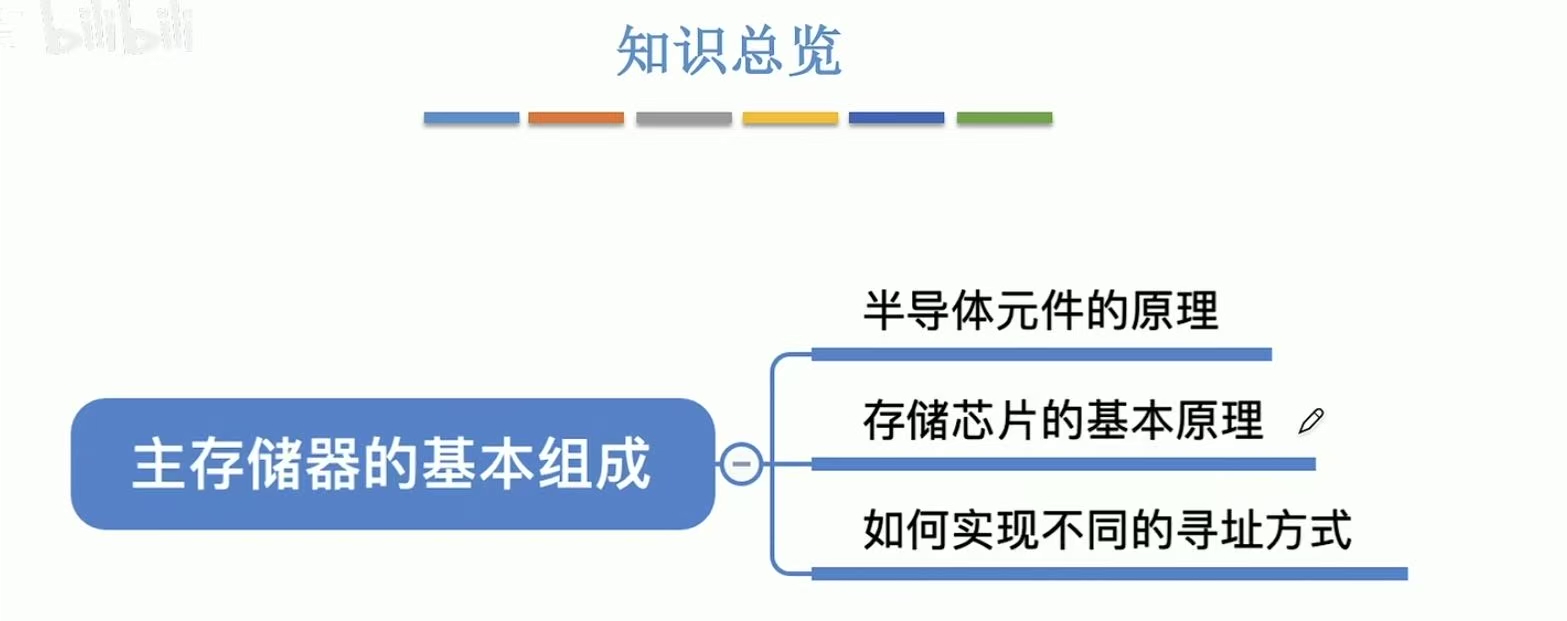

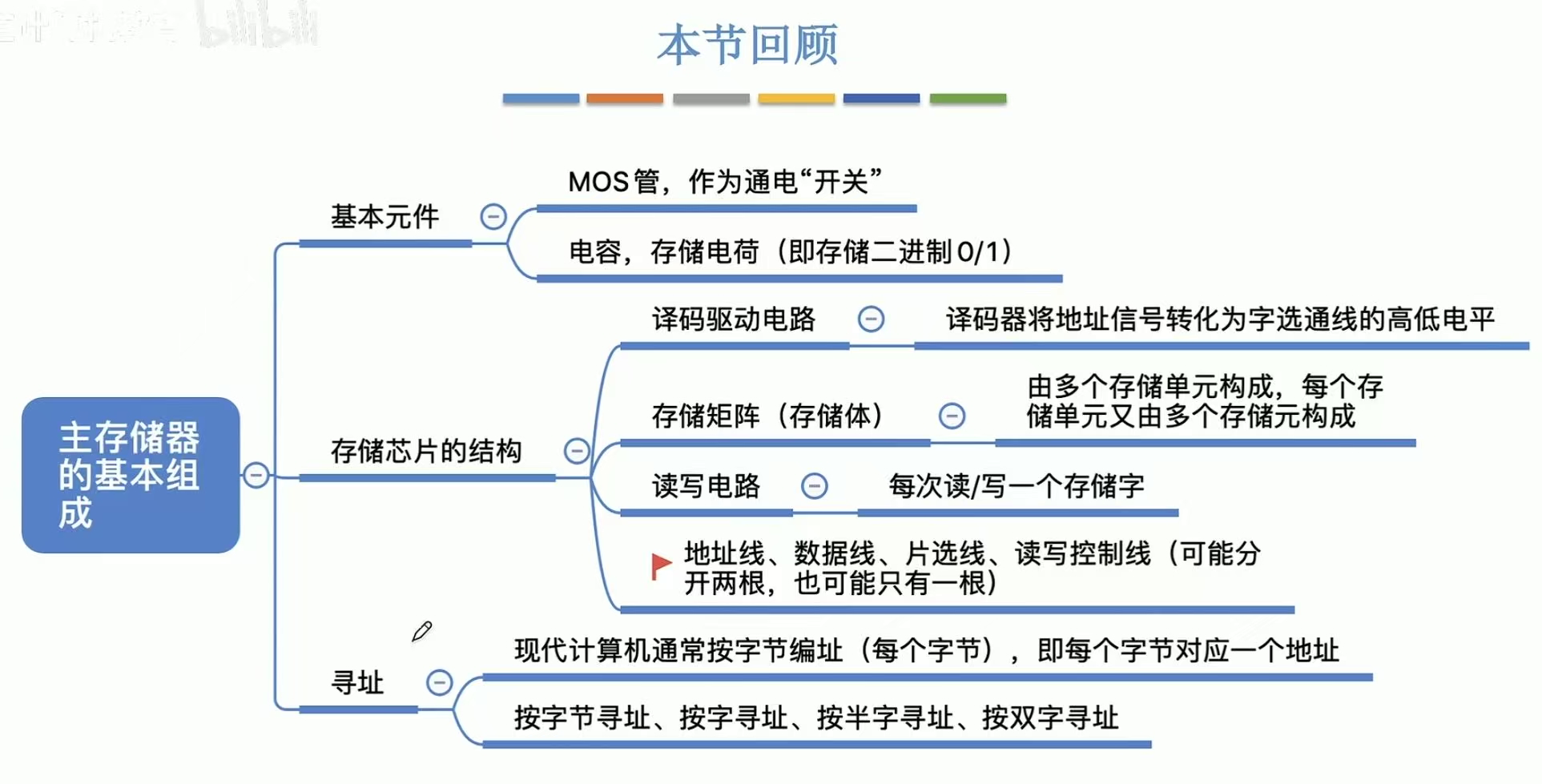

主存储器的基本组成

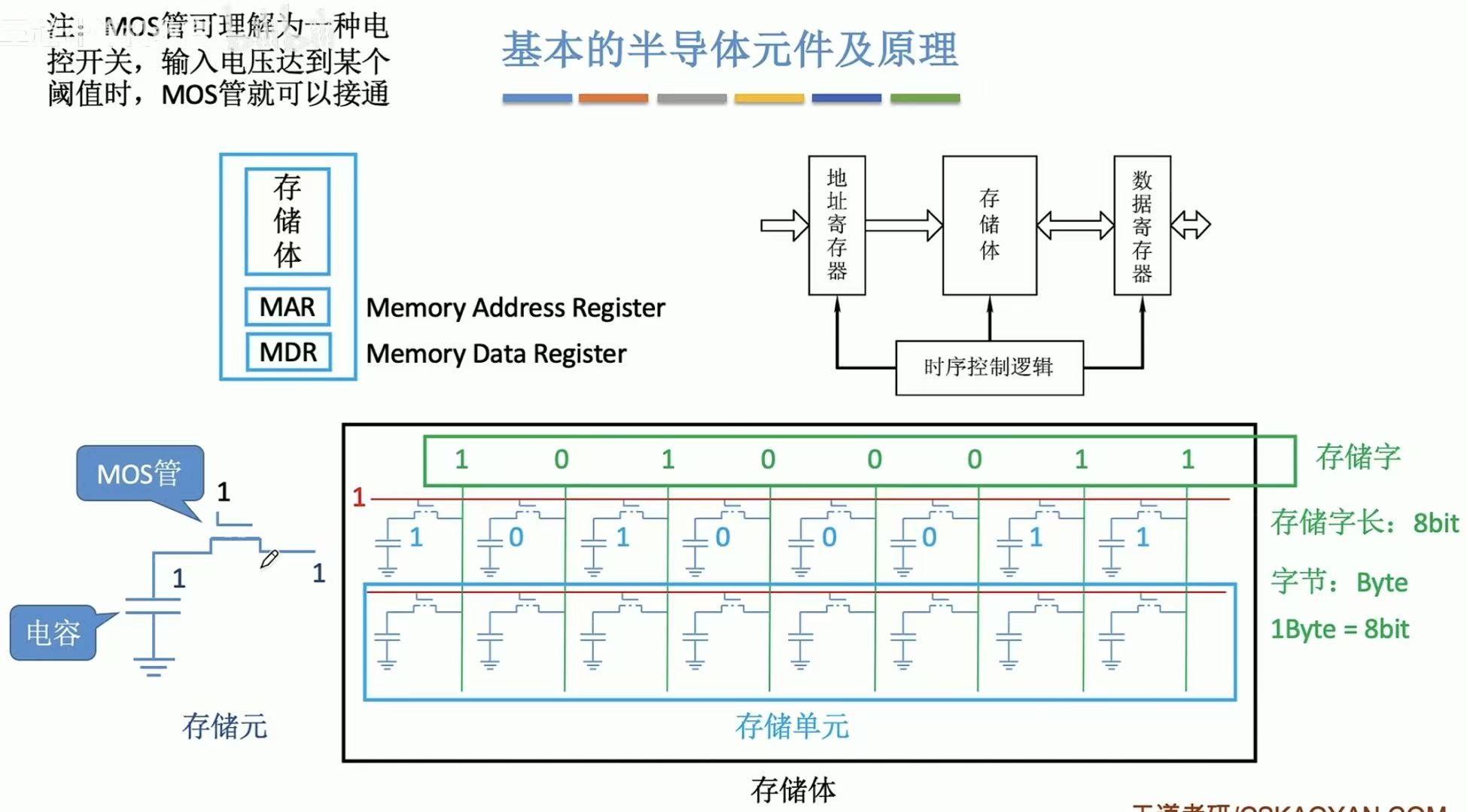

1. 半导体元件的原理

MOS管:开关

MAR:地址寄存器

MDR:数据寄存器

字:一个数字,0或者1,bit

字长=字×个数bit

字节:一个字节=八个数字,Byte

字:字节=1:8

绿色:八个字=一个字节

一个存储元对应一个字

一个存储单元对应八个存储元,也就是八个字,也就是一个字节

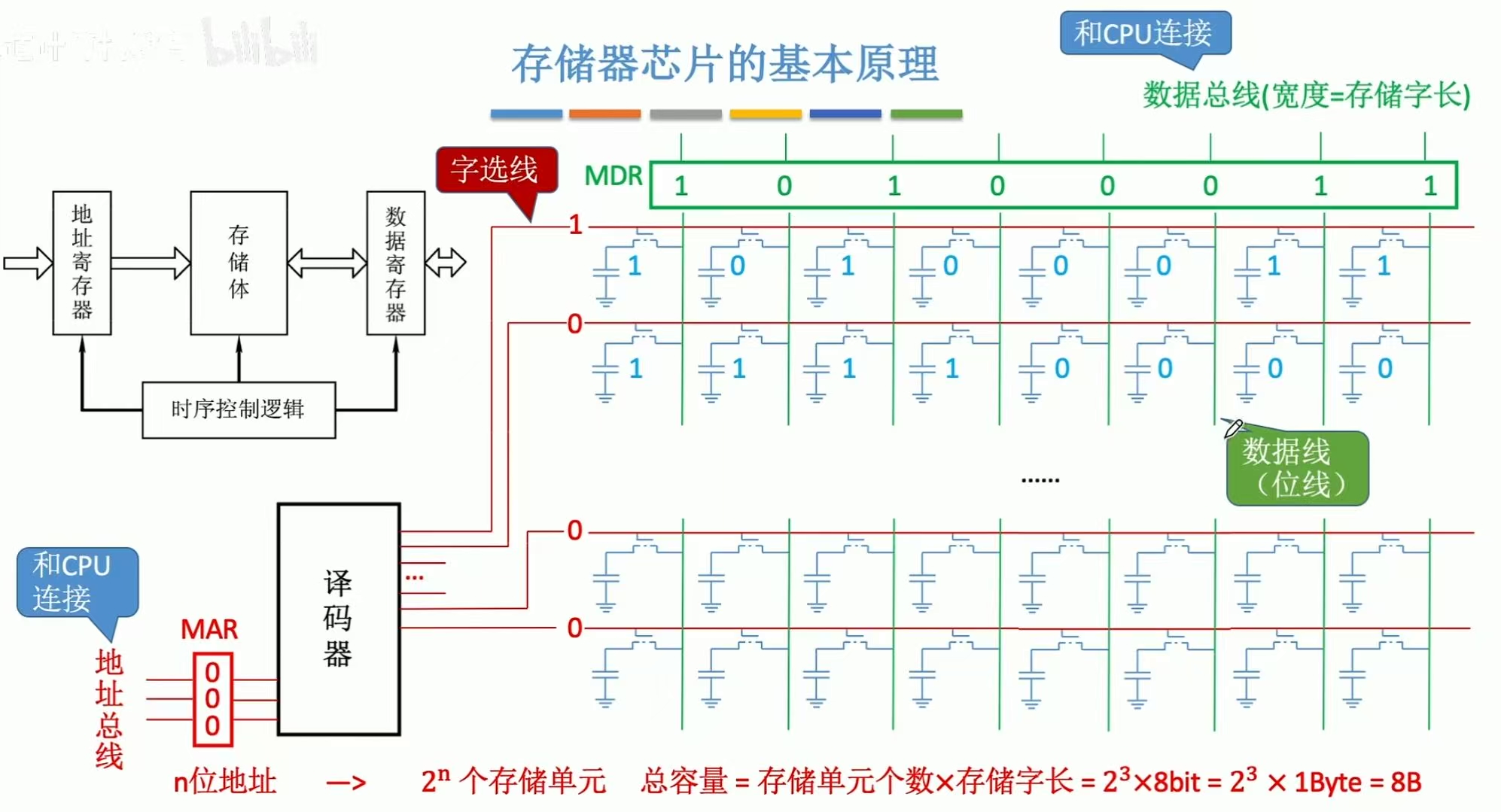

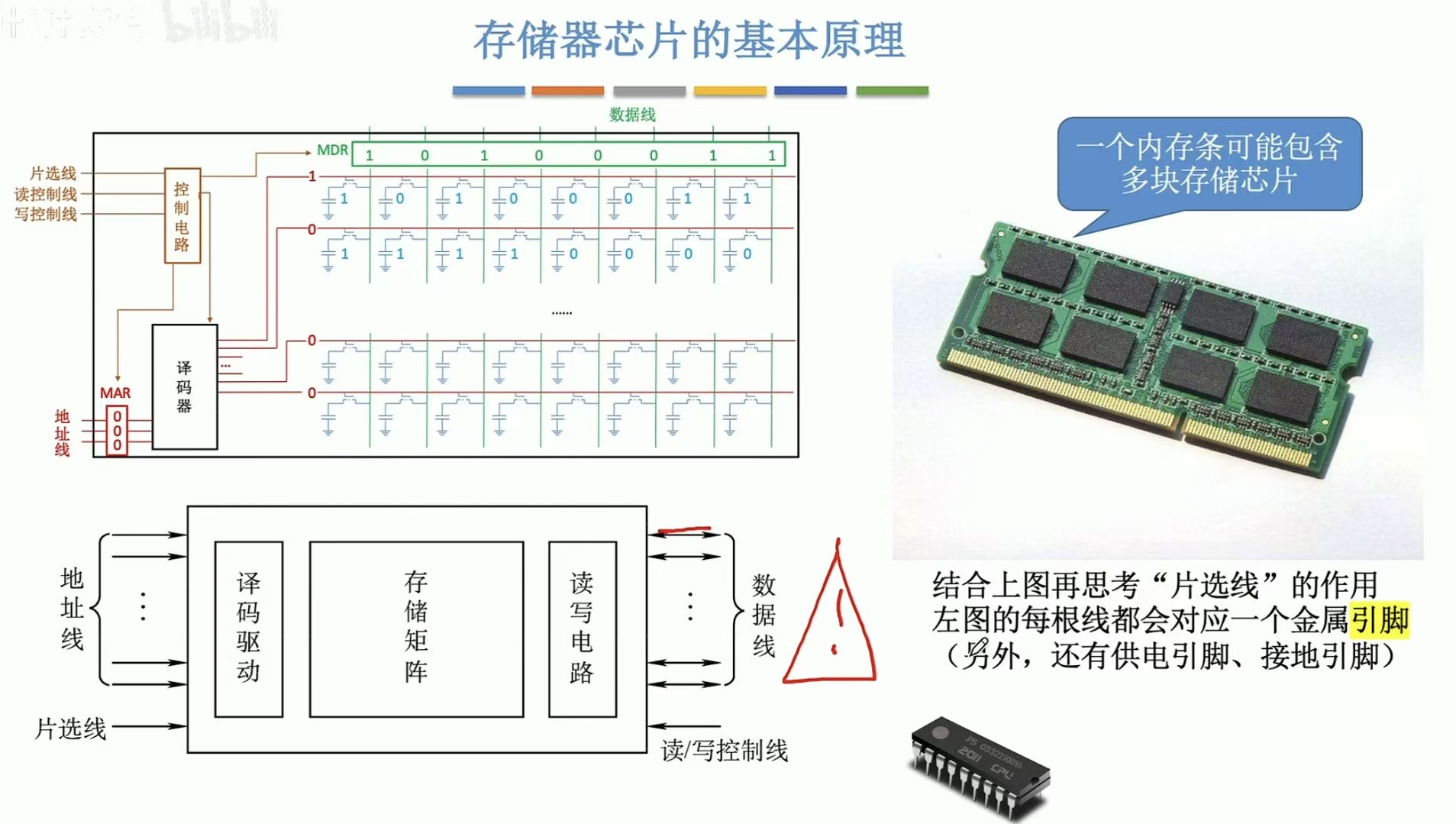

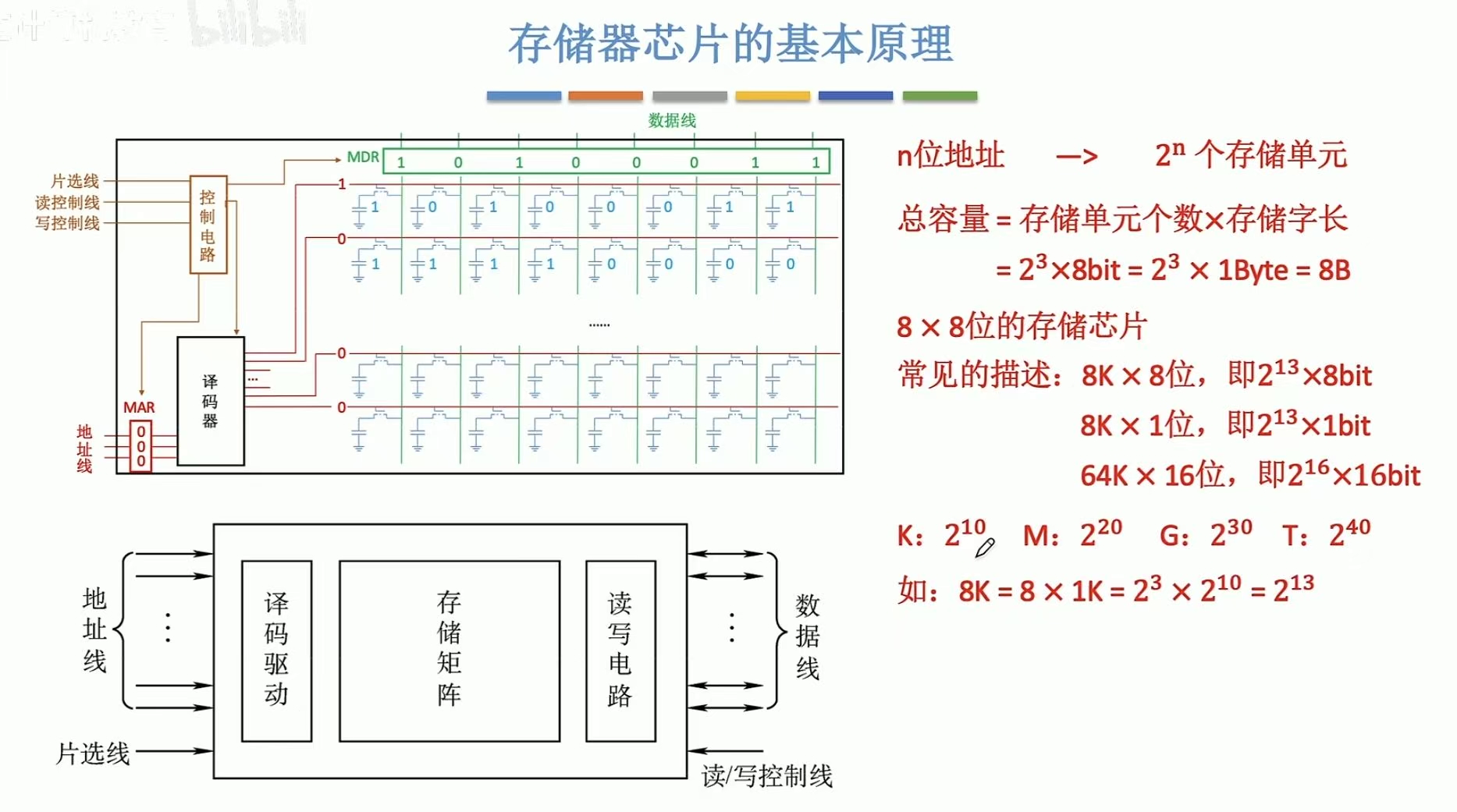

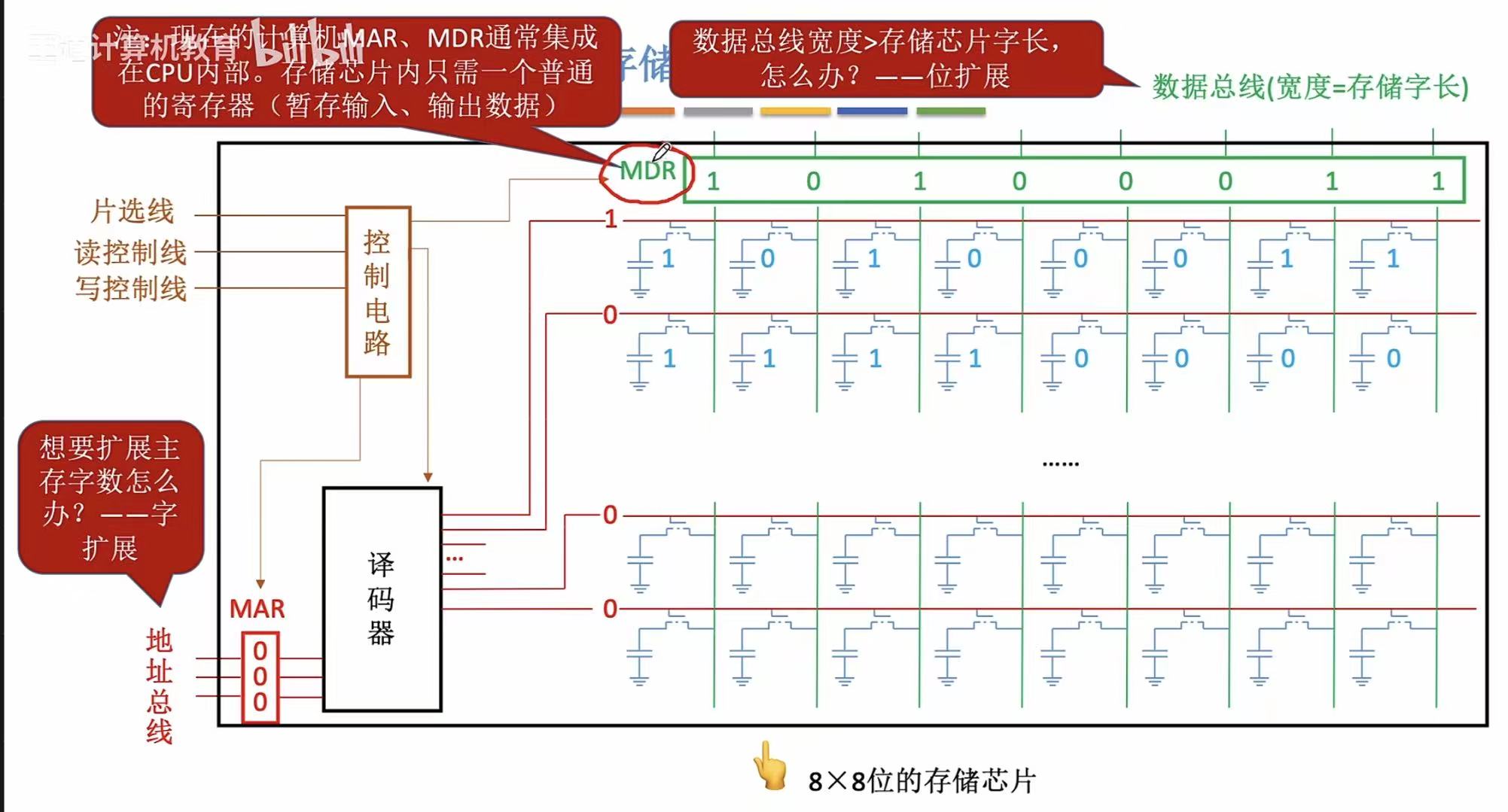

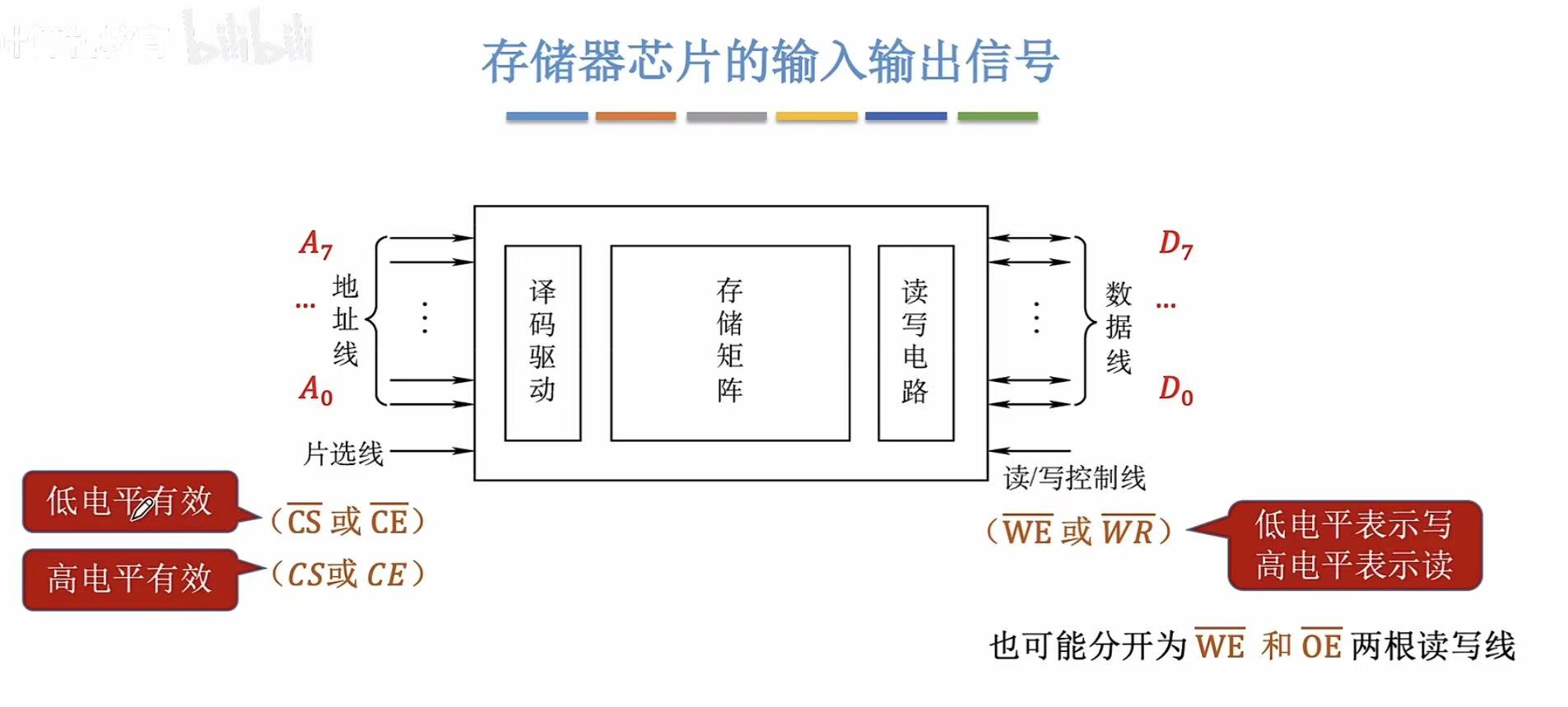

2. 存储器芯片的基本原理

绿色:数据总线,与CPU相连,需要的时候可以调出

红色:地址总线,调出数据的时候用来查找需要调出数据的地址

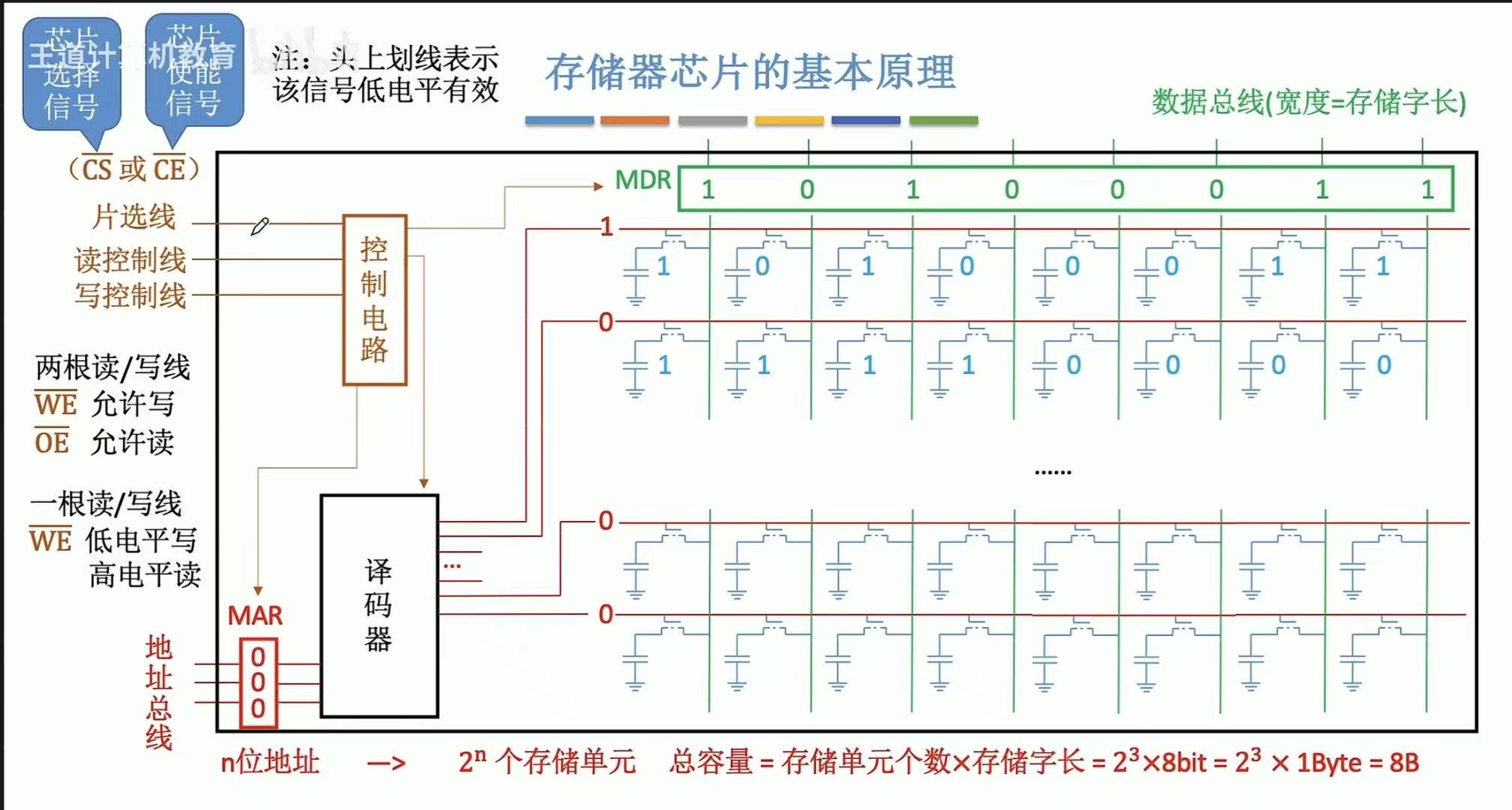

CS:chip select 芯片选择

CE:chip enable 芯片使能

WE:write enable 写使能

OE:output enable 输出使能

注意:头上划线的代表该信号低电平时有效

片选线:因为内存条上会有多块存储芯片,所以需要用片选线确定自己需要的是哪一个存储芯片。

读控制线:控制是否需要输出

写控制线:控制是否需要输入

n位地址-->n根地址线-->2n个存储单元

总容量=存储单元个数(竖着的宽)×存储字长(横着的长)

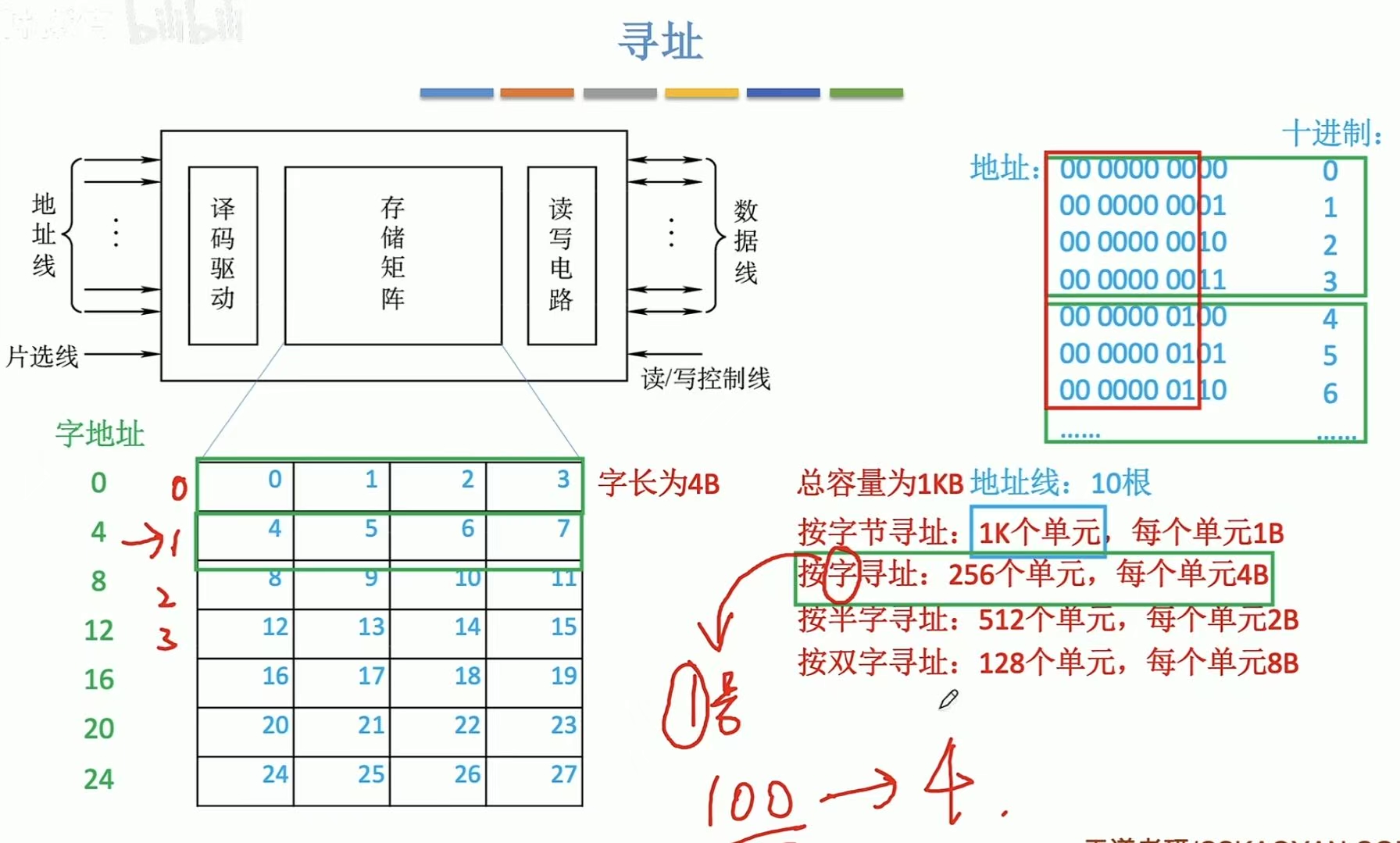

3. 寻址

每个空格是1Byte(8个字节),四个空格就是4B。一行对应一个存储单元,所以一个存储字长是4B-->第二行每个单元4B

字(指存储字长):一个存储单元=一个存储字长=一行=4B

半字:4/2=2B

双字:4×2=8B

总容量1K:

- 第一行:1K×1B

- 第二行:256×4

- 第三行:512×2

- 第四行:128×8

4. 小结

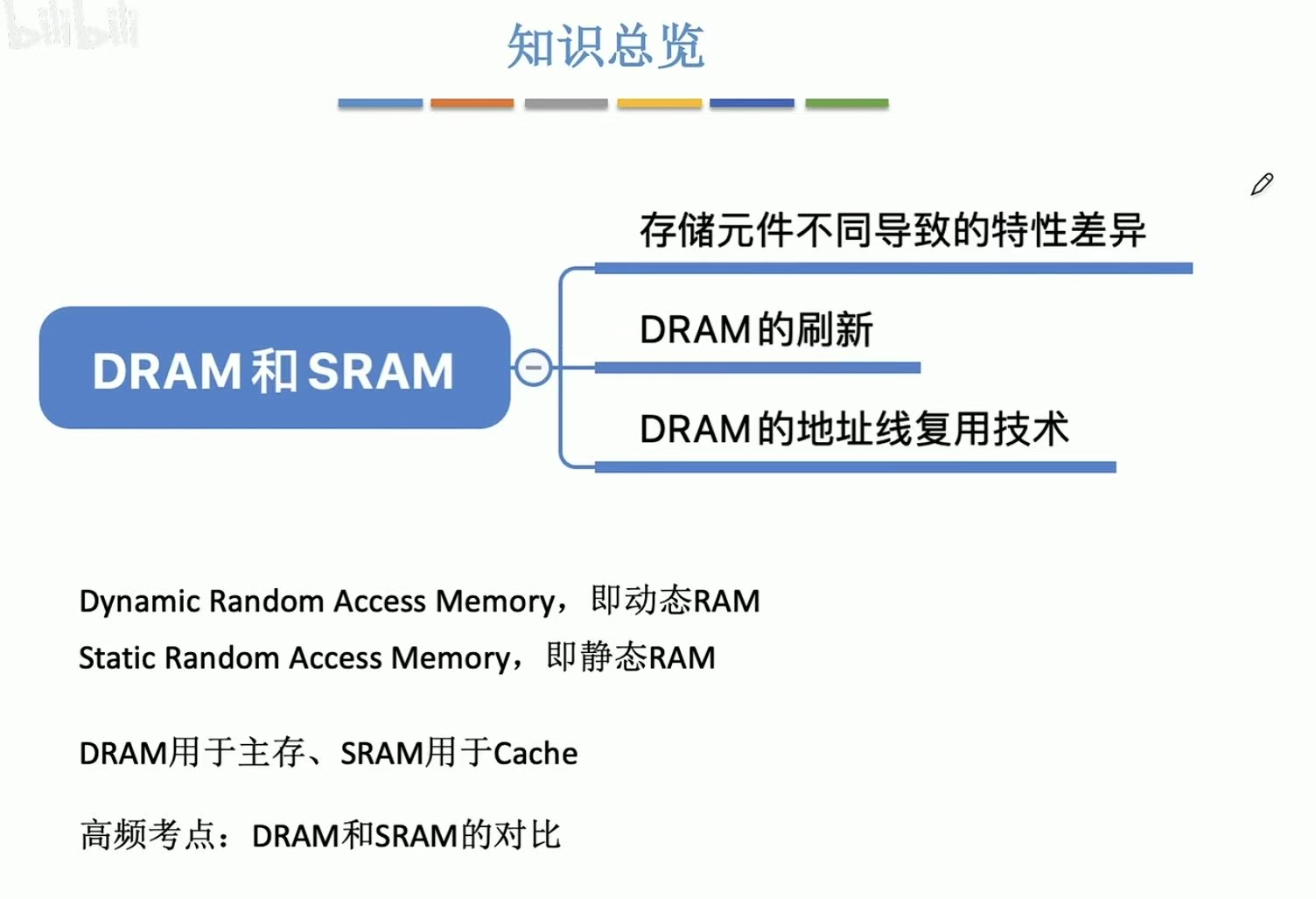

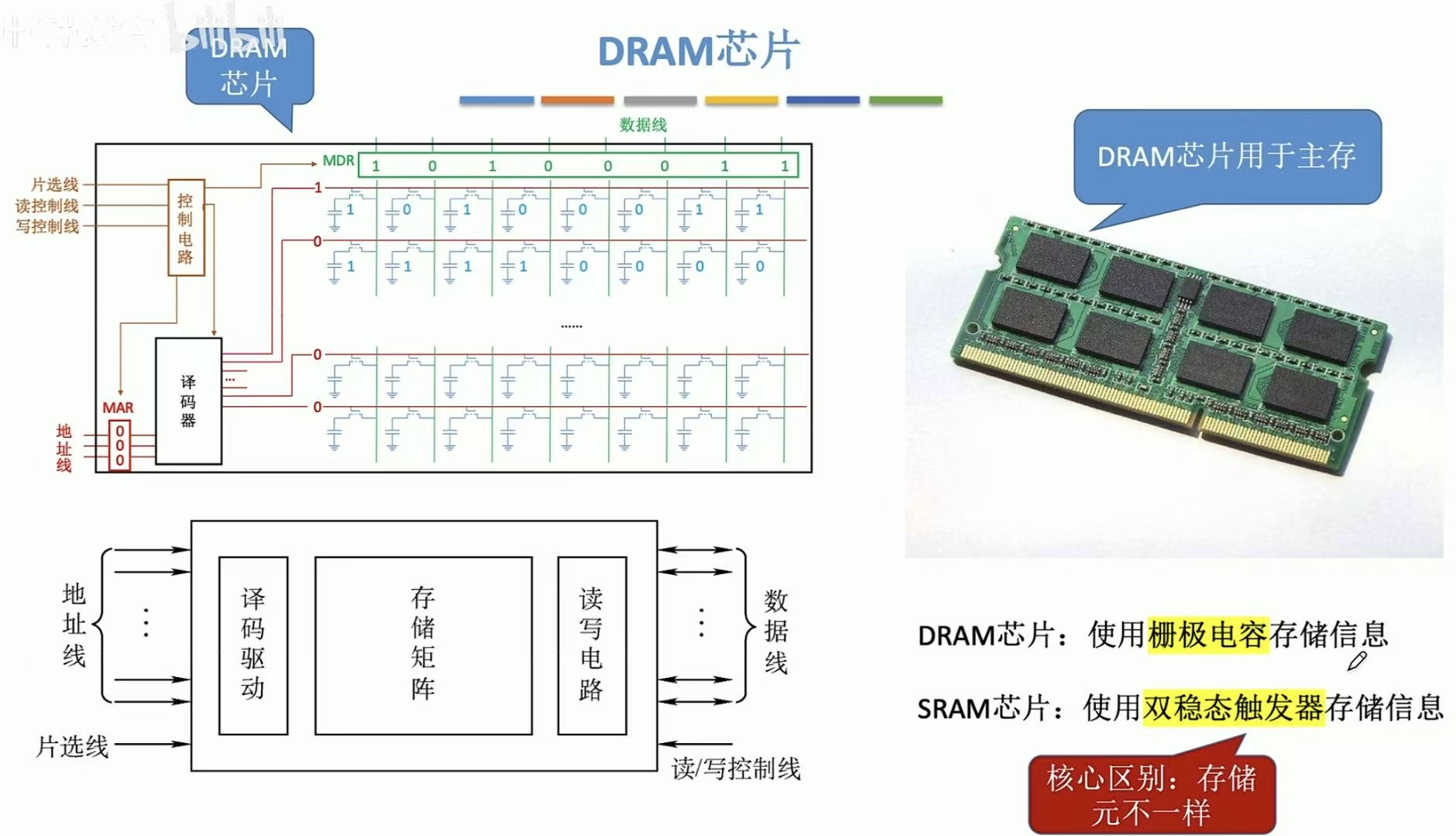

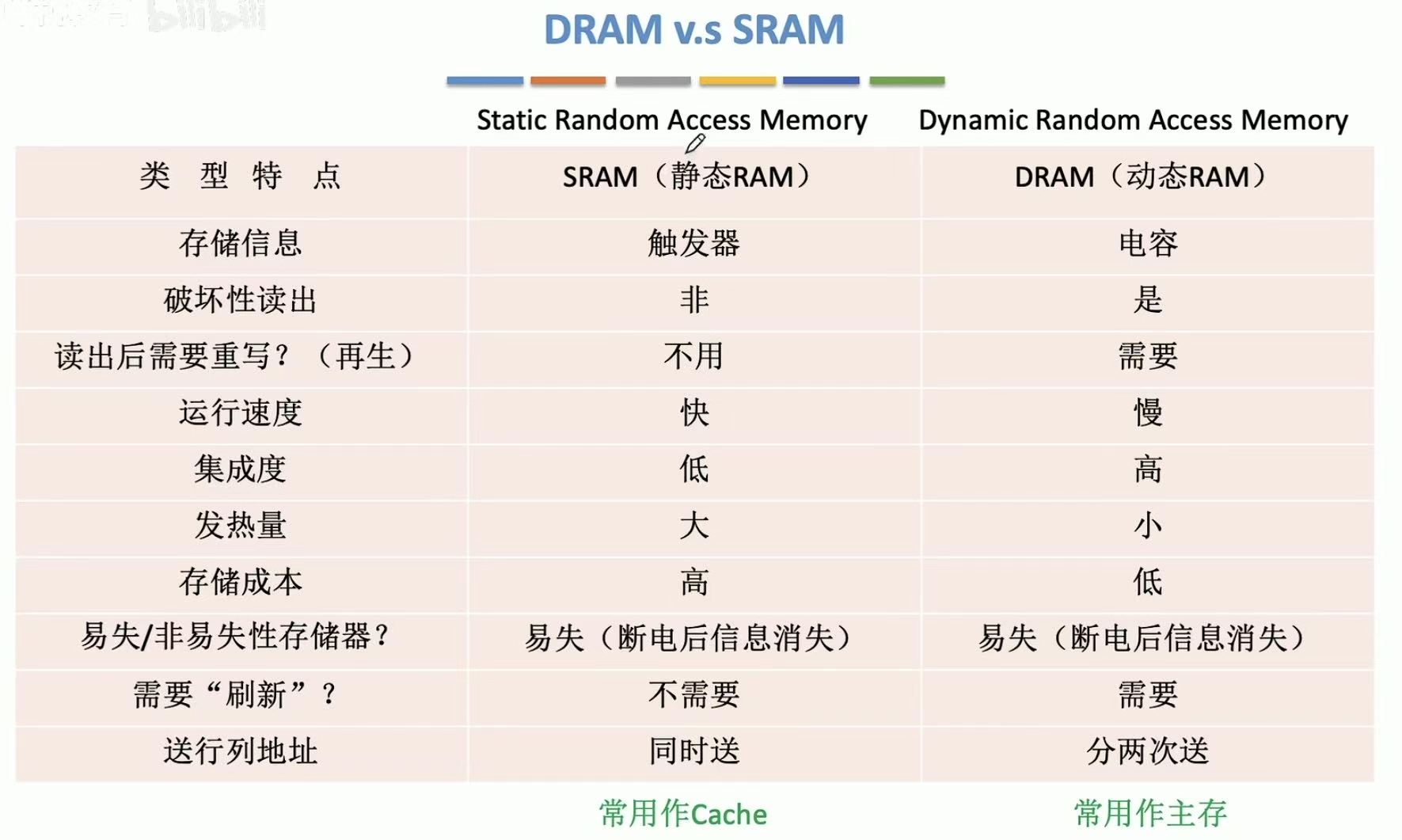

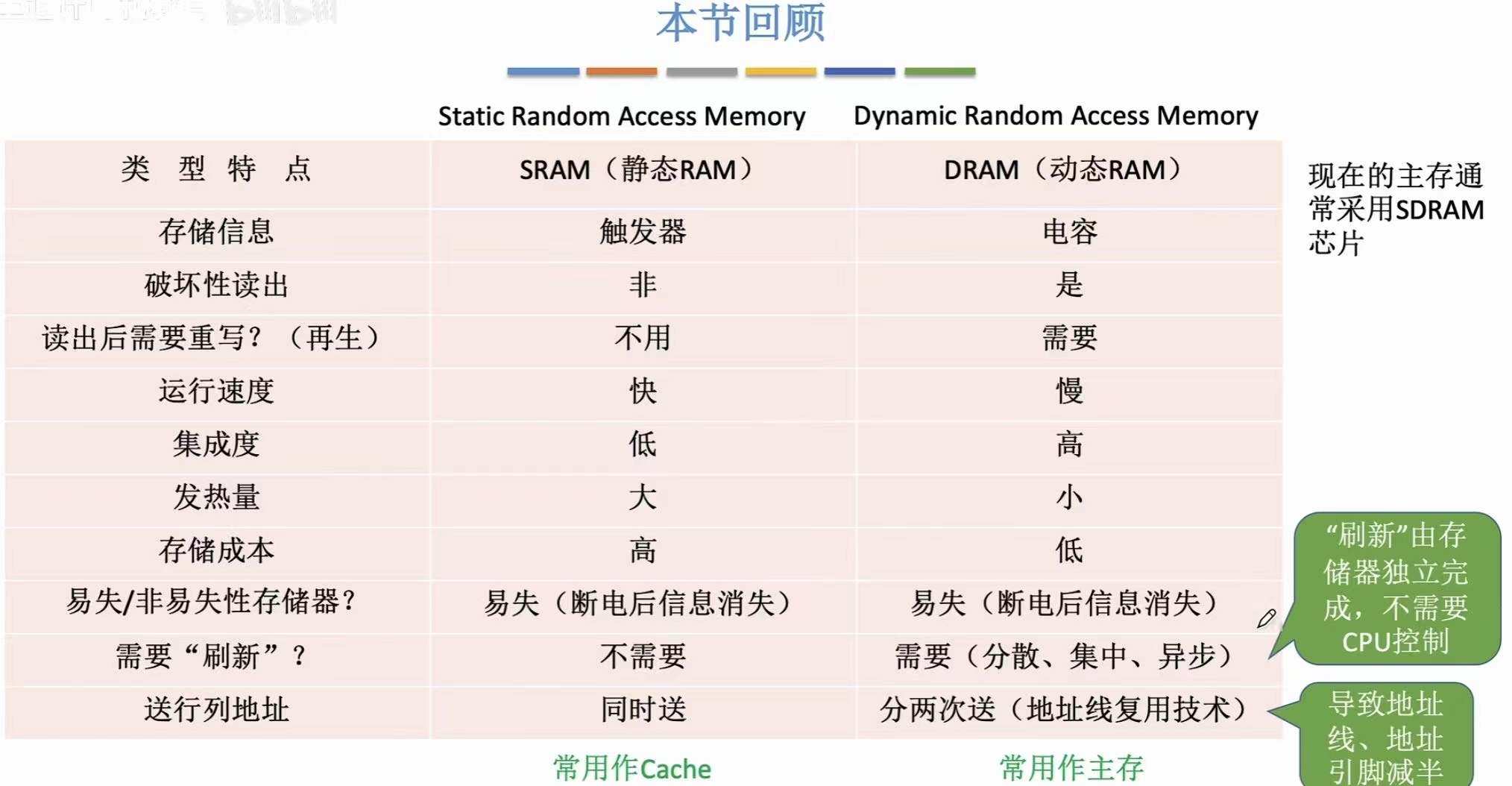

DRAM和SRAM

1. 特性差异

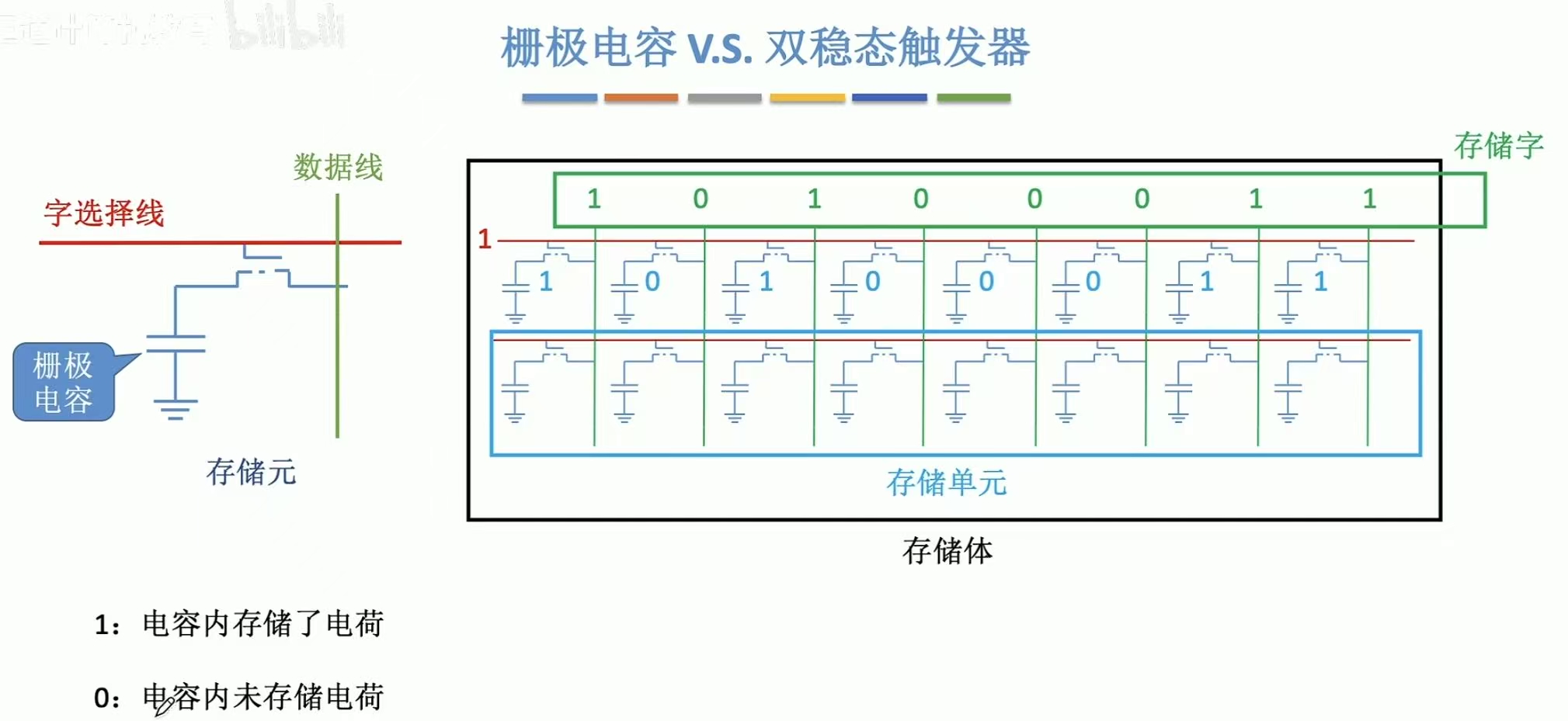

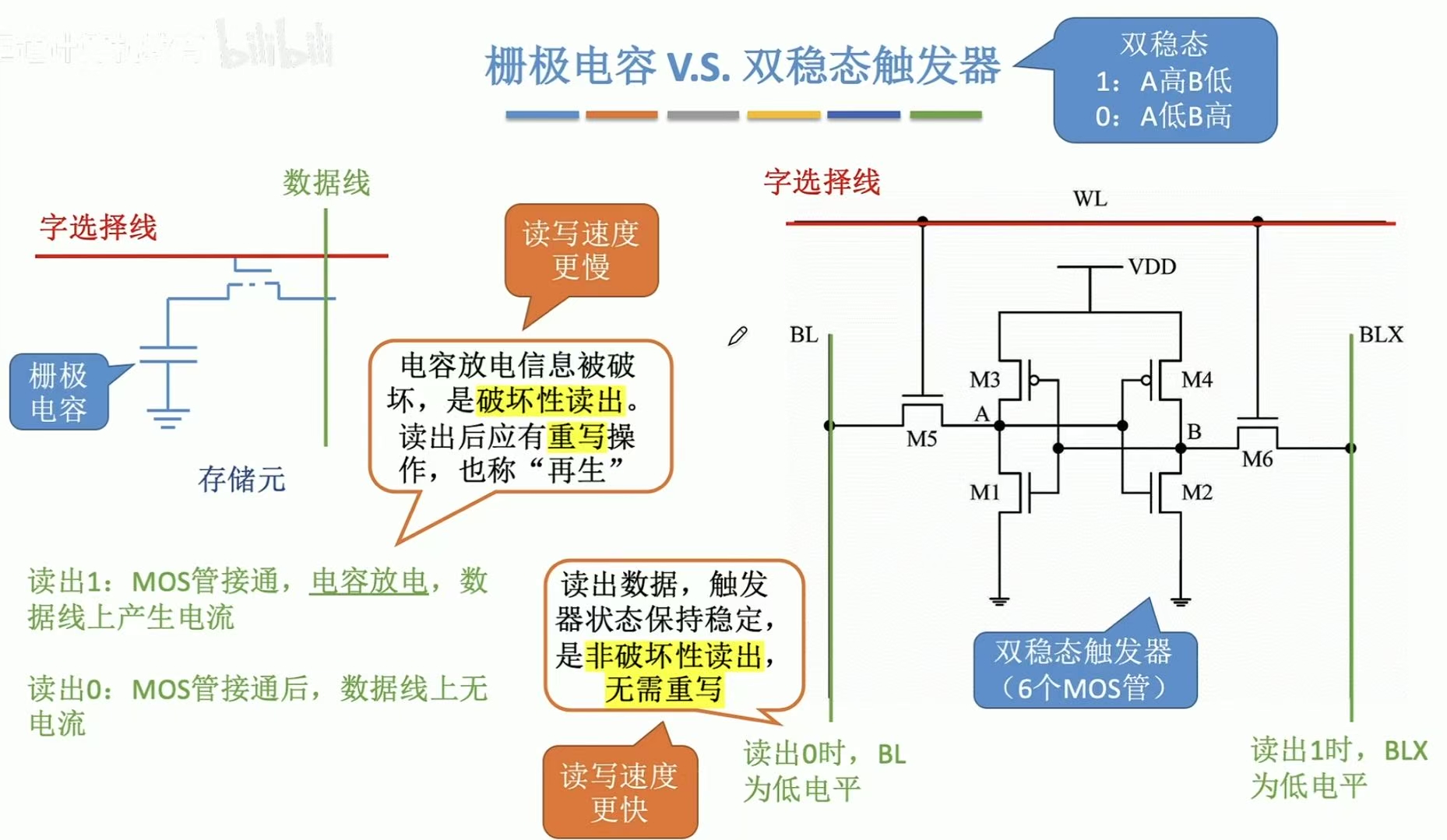

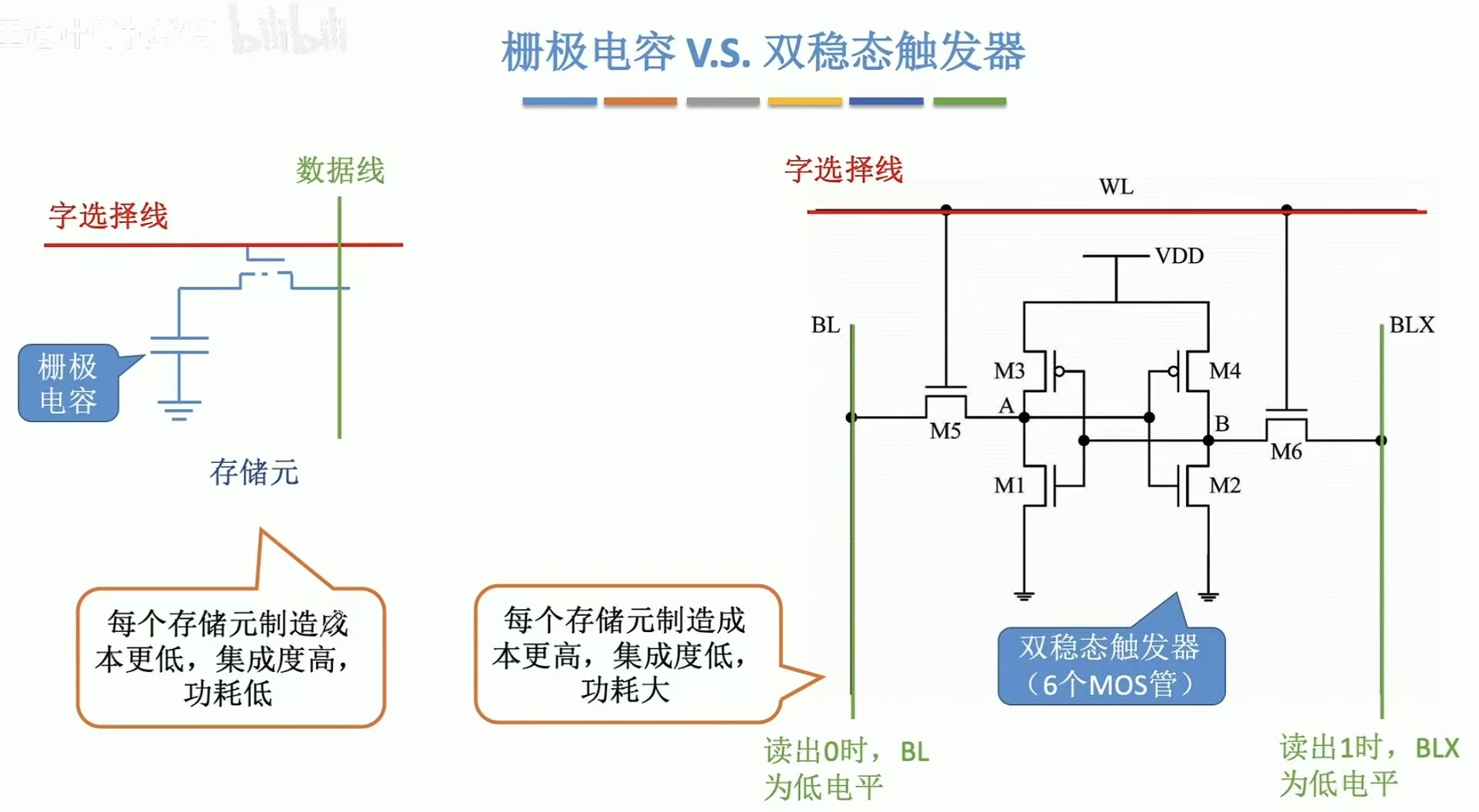

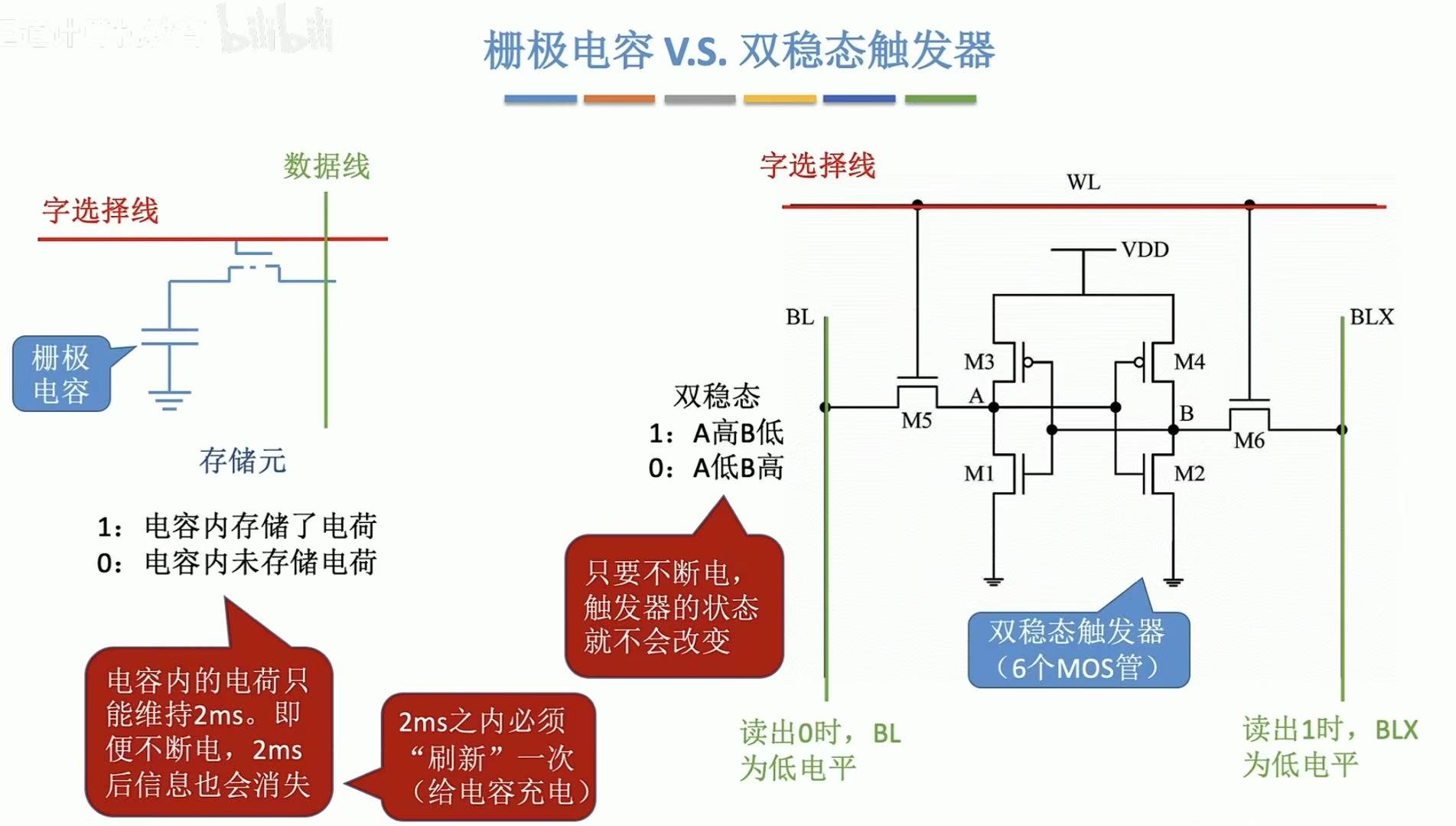

记住:栅极电容-->DRAM

栅极电容:小

双稳态触发器:大

记忆点:

双:1或者0都可以输入,会根据各自定义不同进行操作

稳态:非破坏性读出

刷新 :

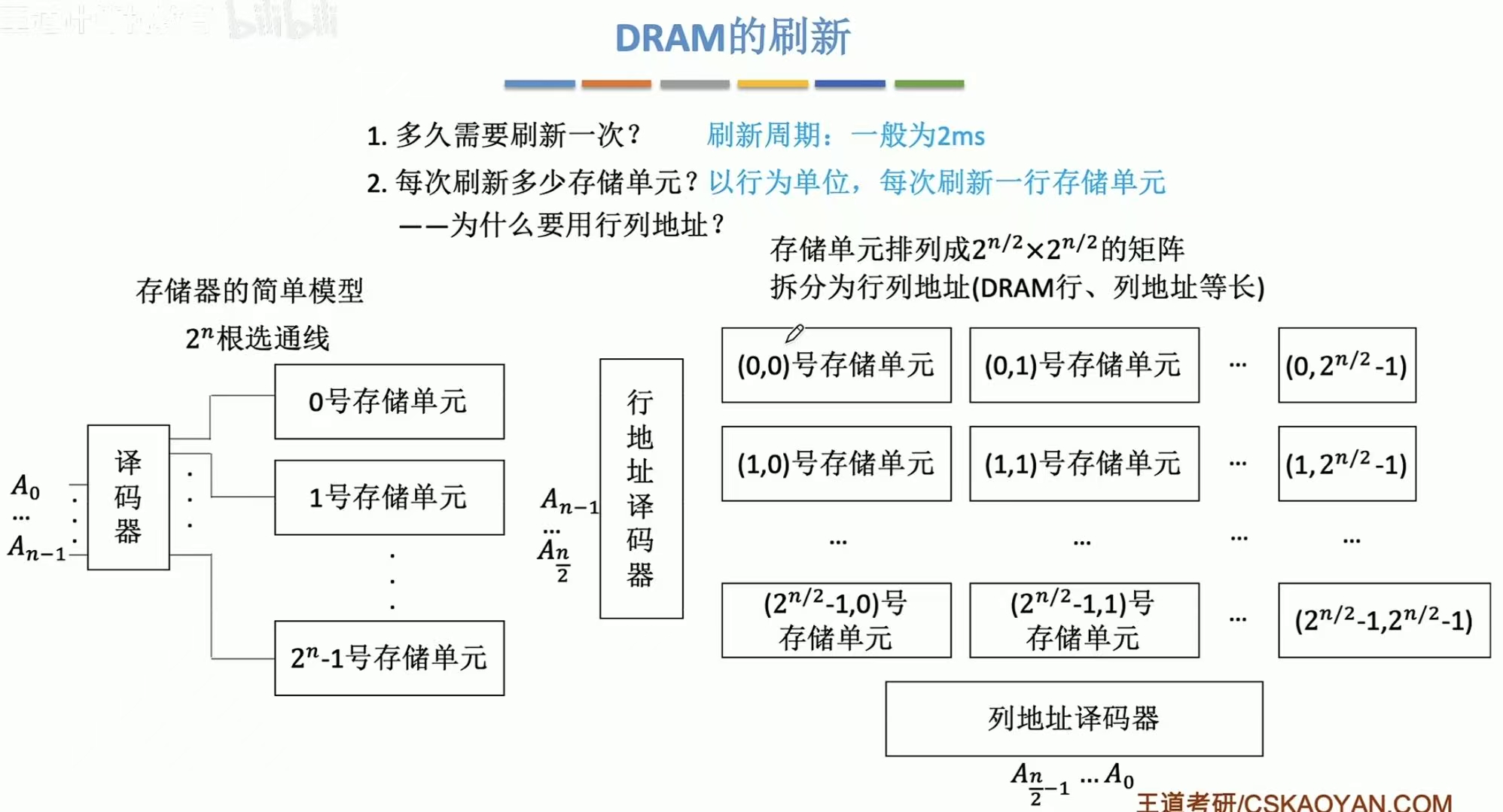

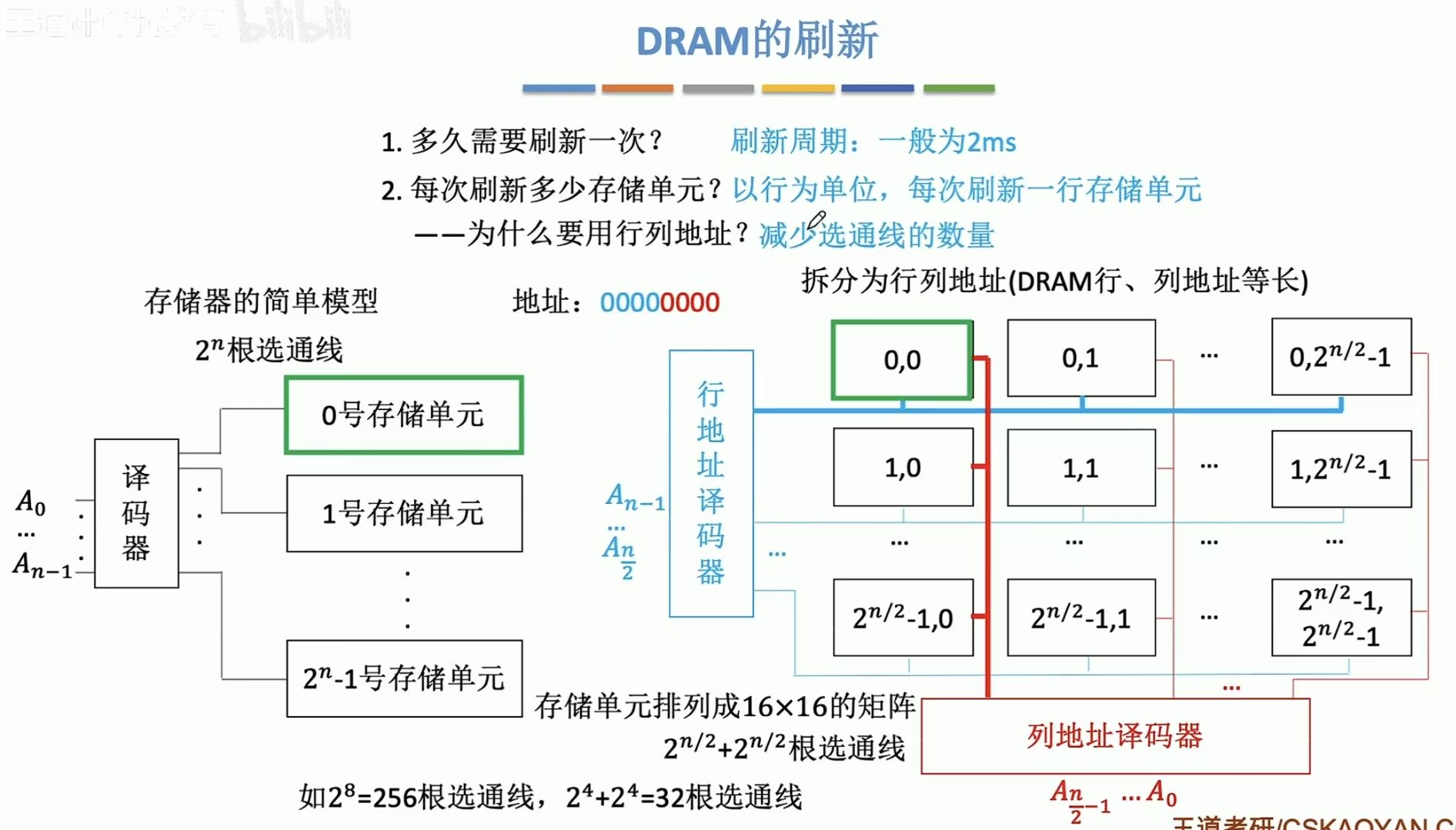

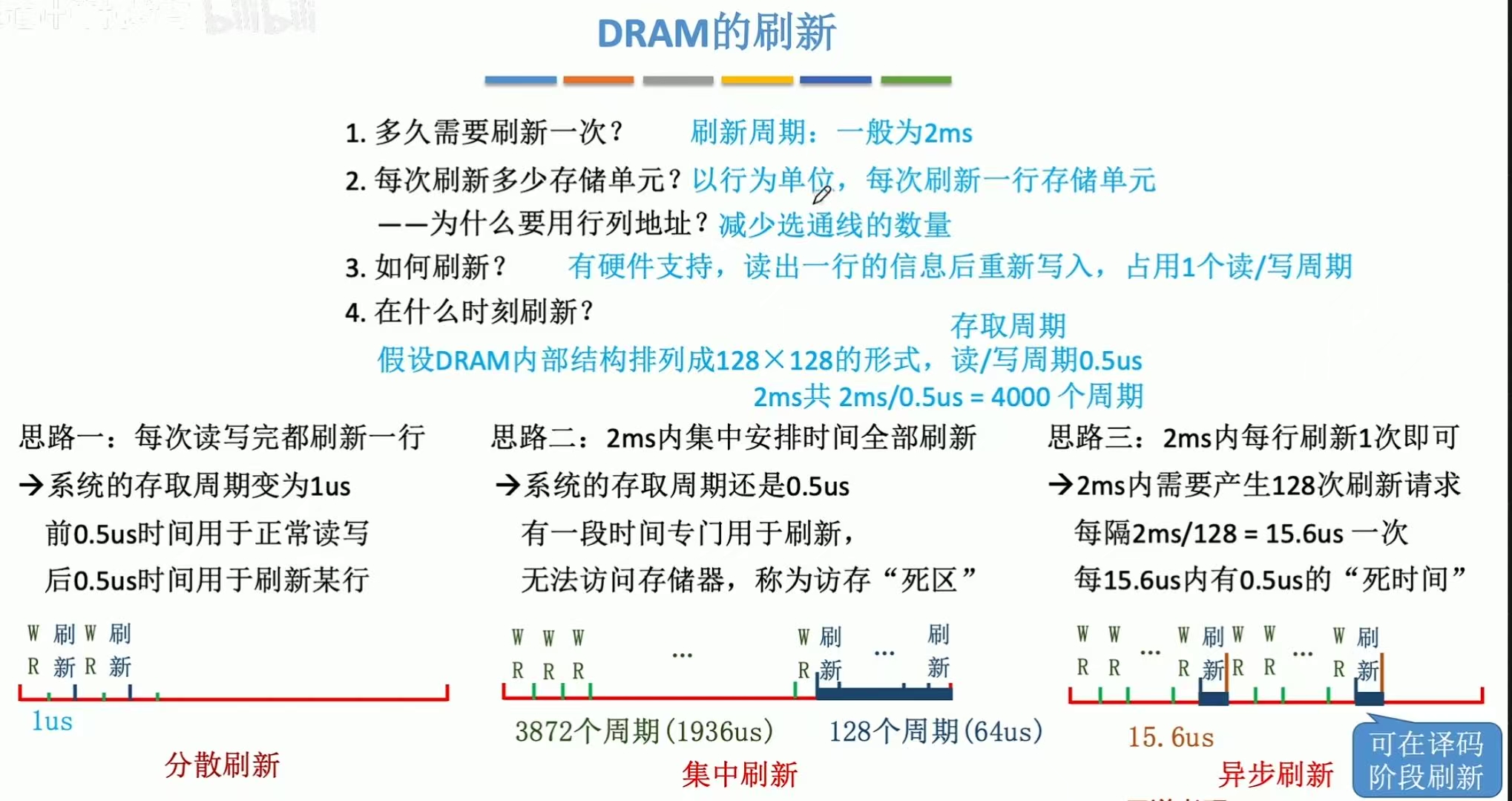

2. DRAM的刷新

同时被行和列选中的地址就是需要的地址。

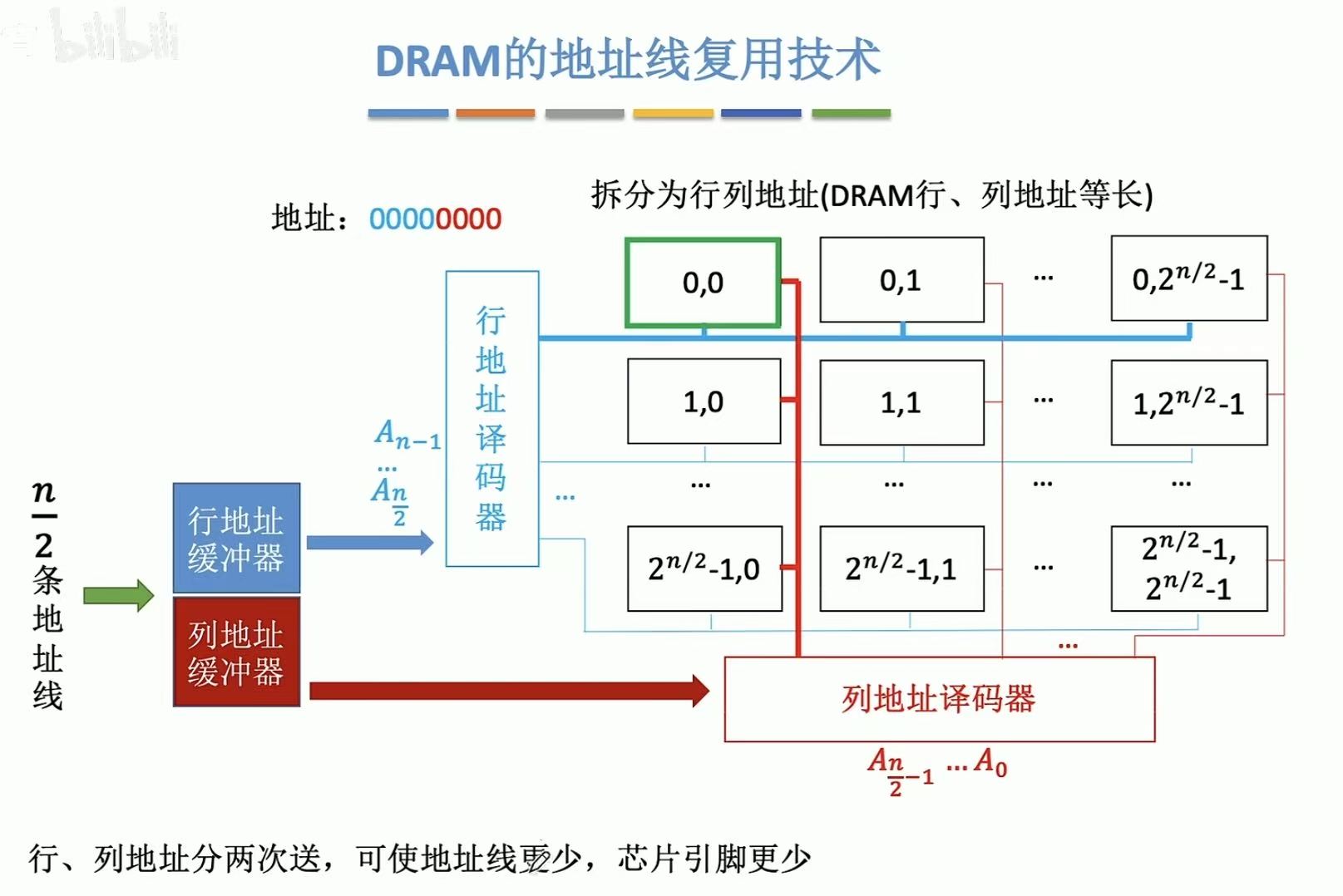

3. DRAM的地址线复用技术

地址线可以同时作为行或者列,先用作行筛选好自己的地址,再转换为列进行更细致的选择。

4. 小结

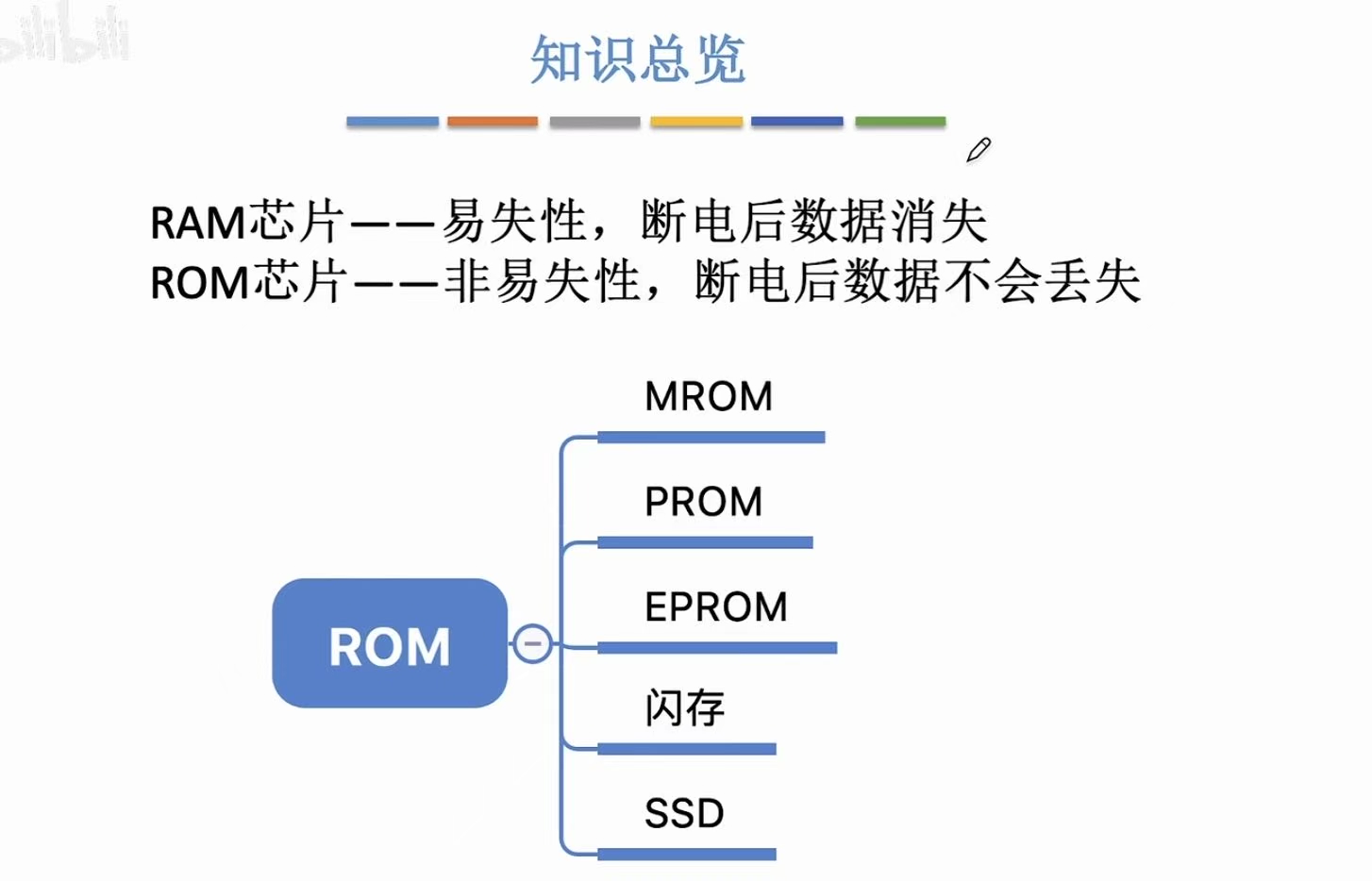

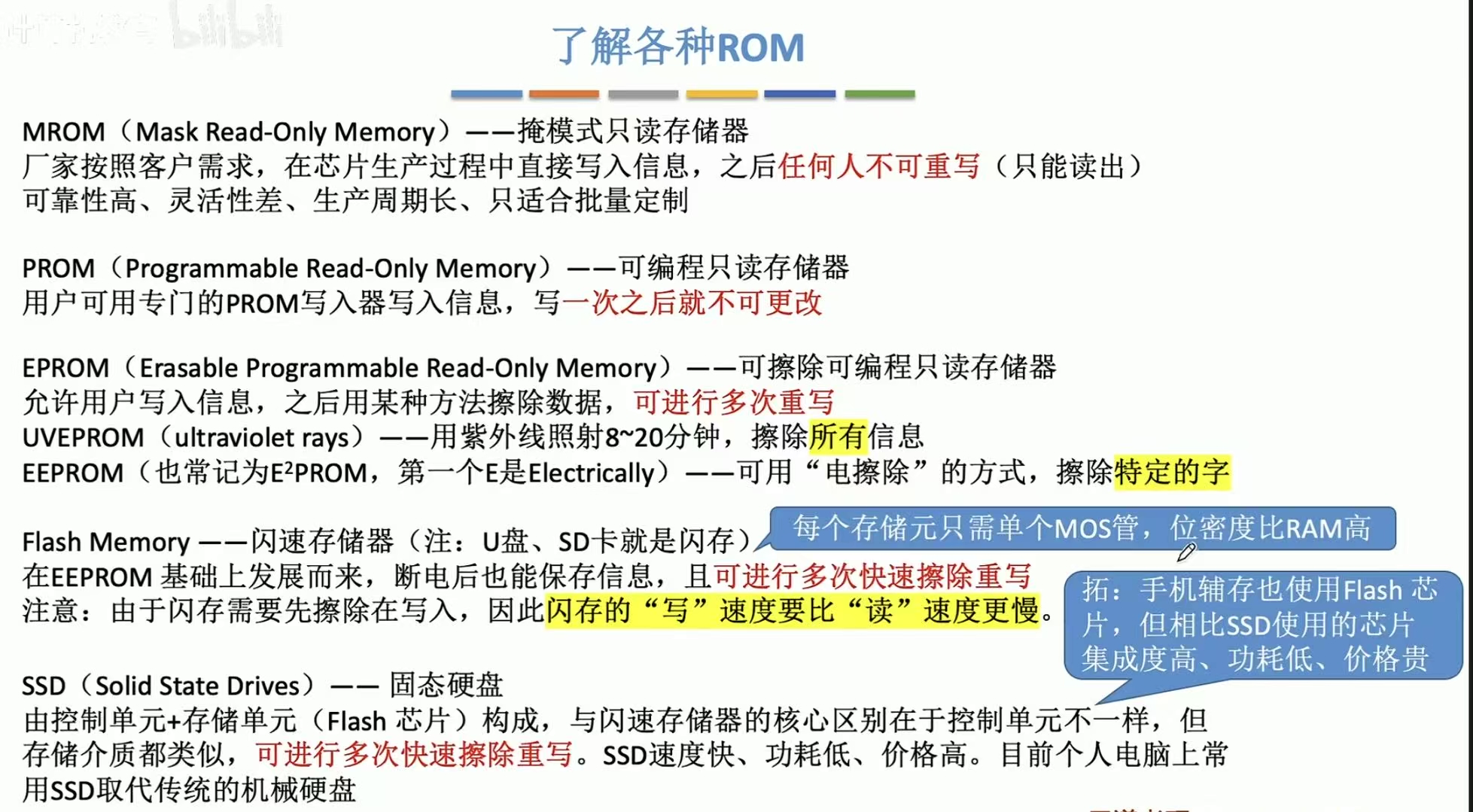

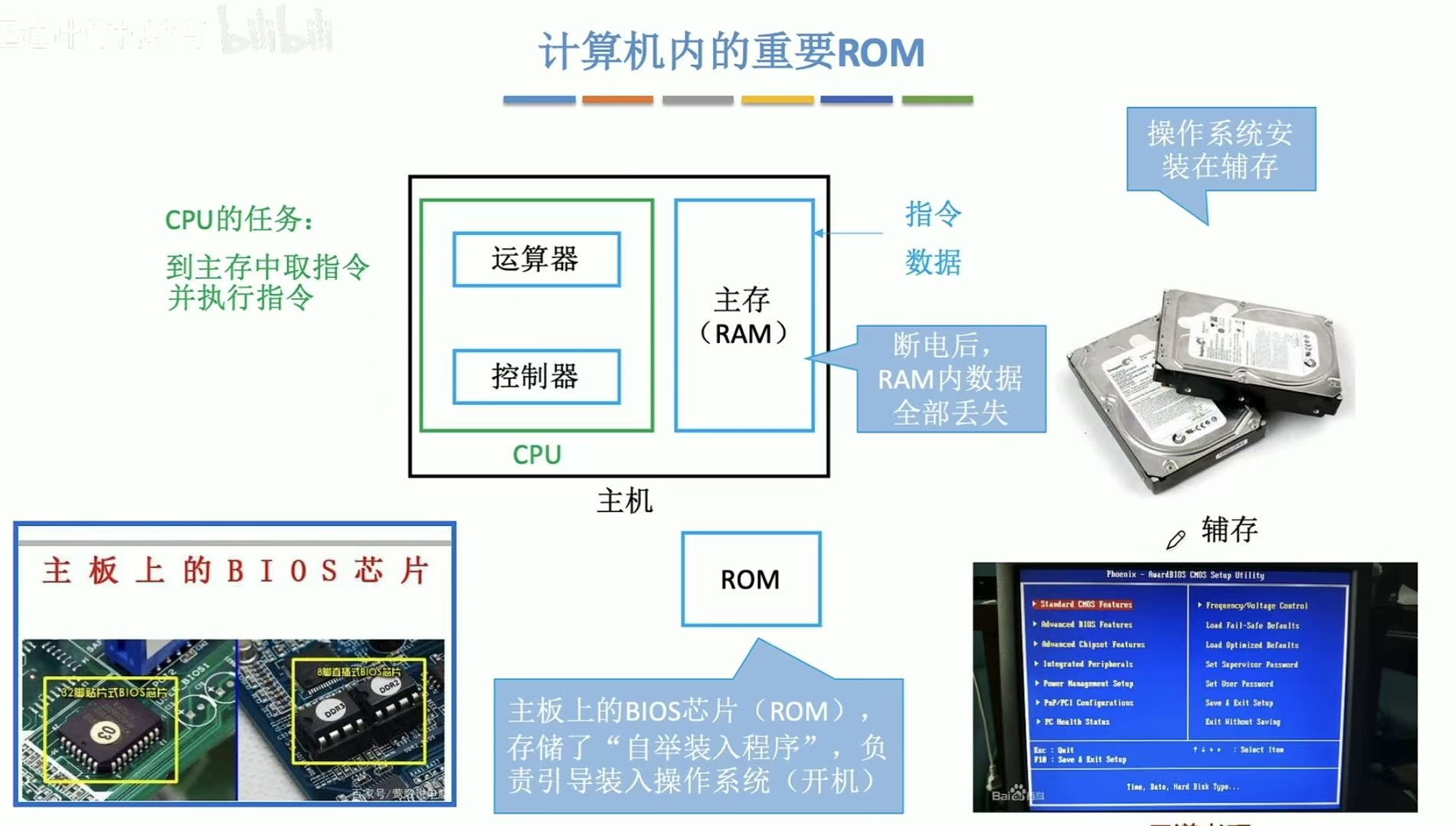

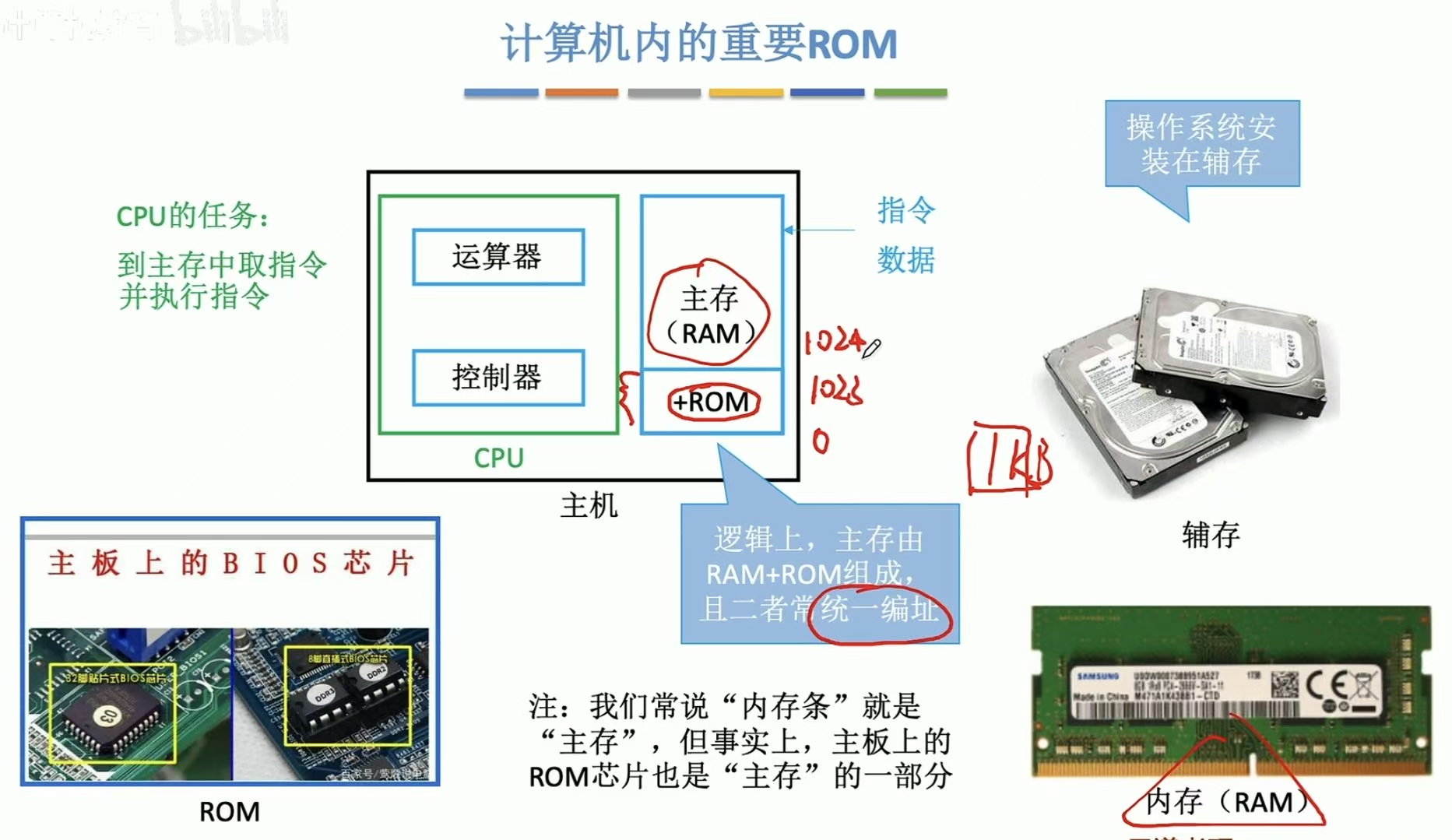

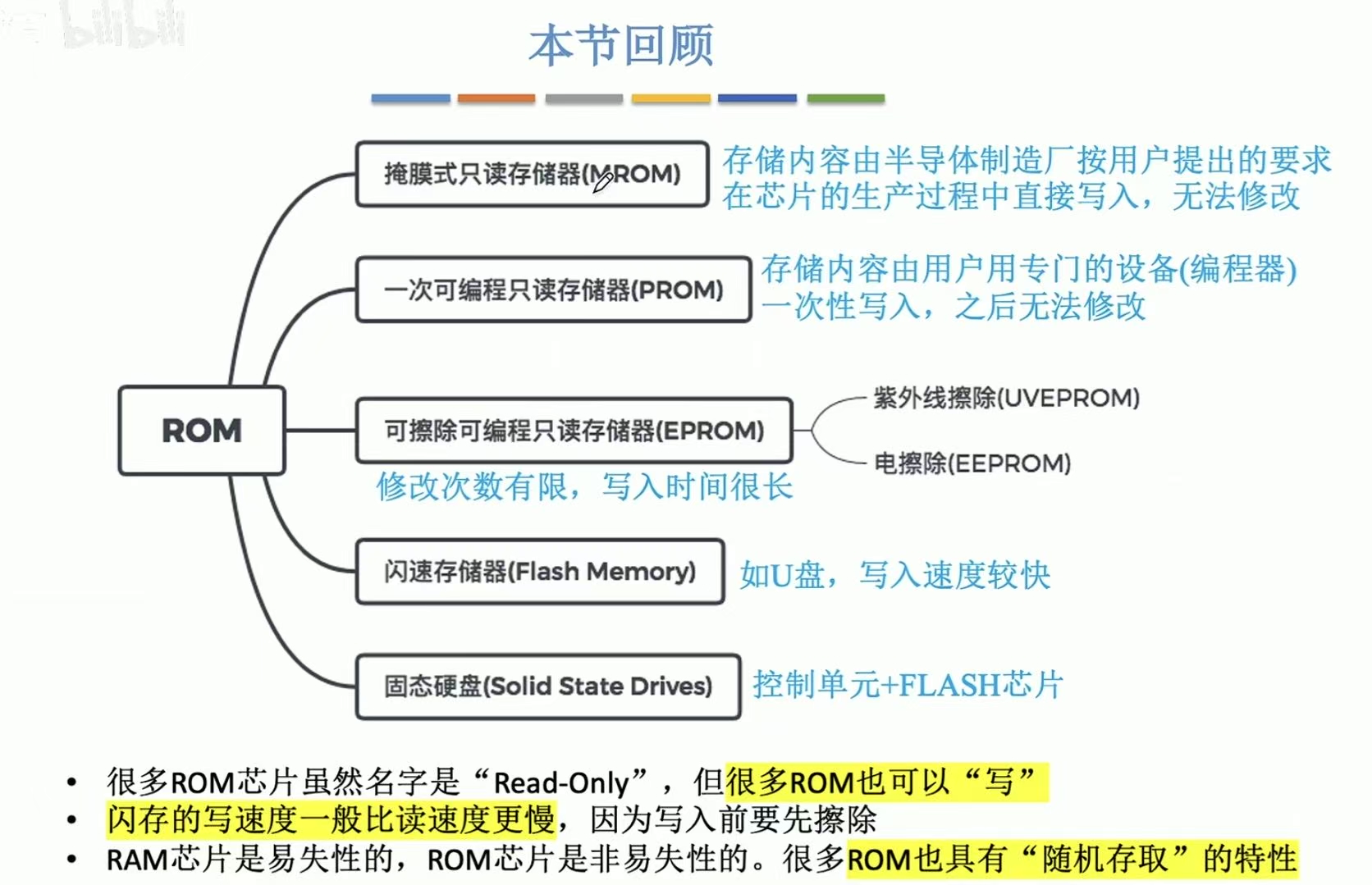

ROM

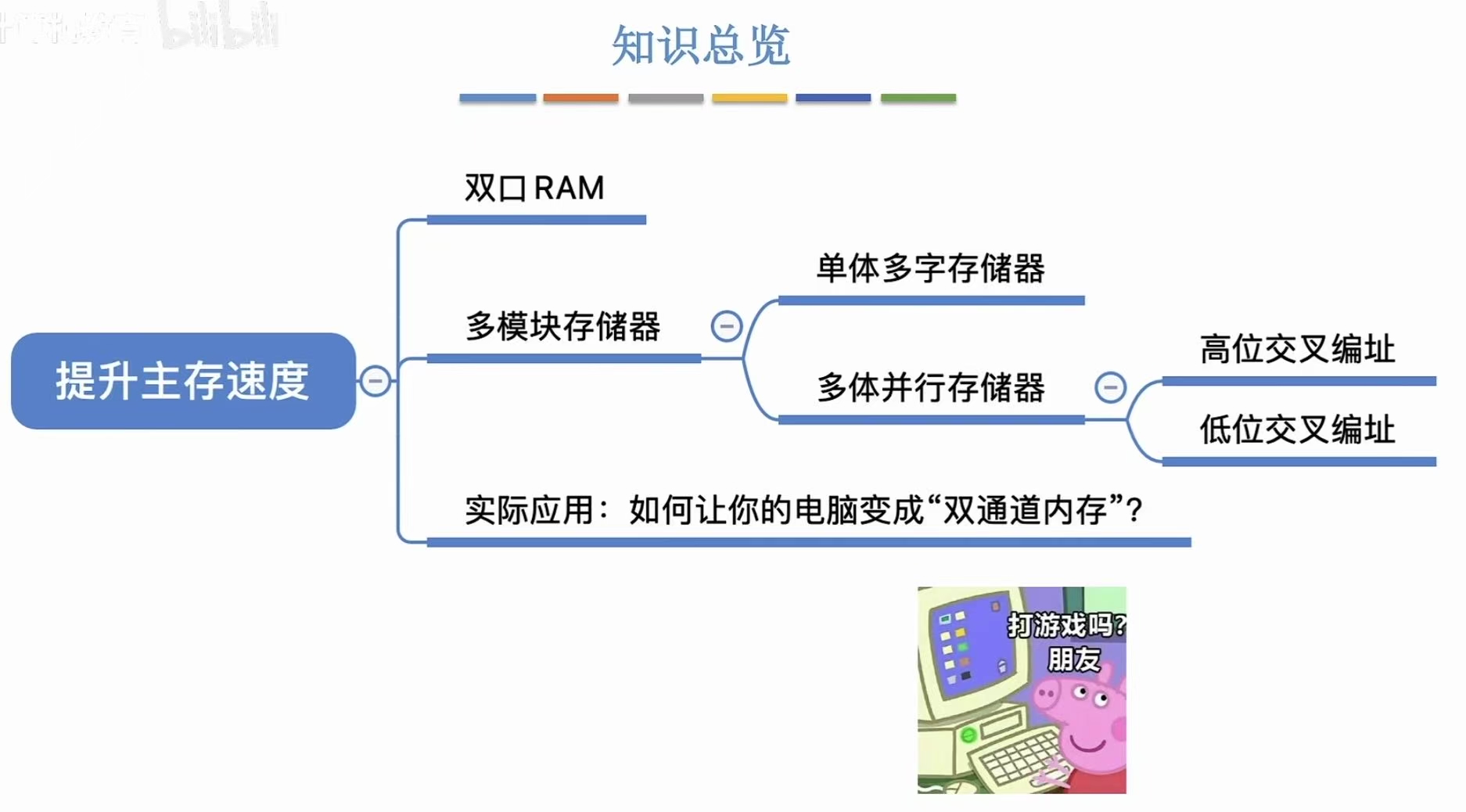

双端RAM和多模块存储器

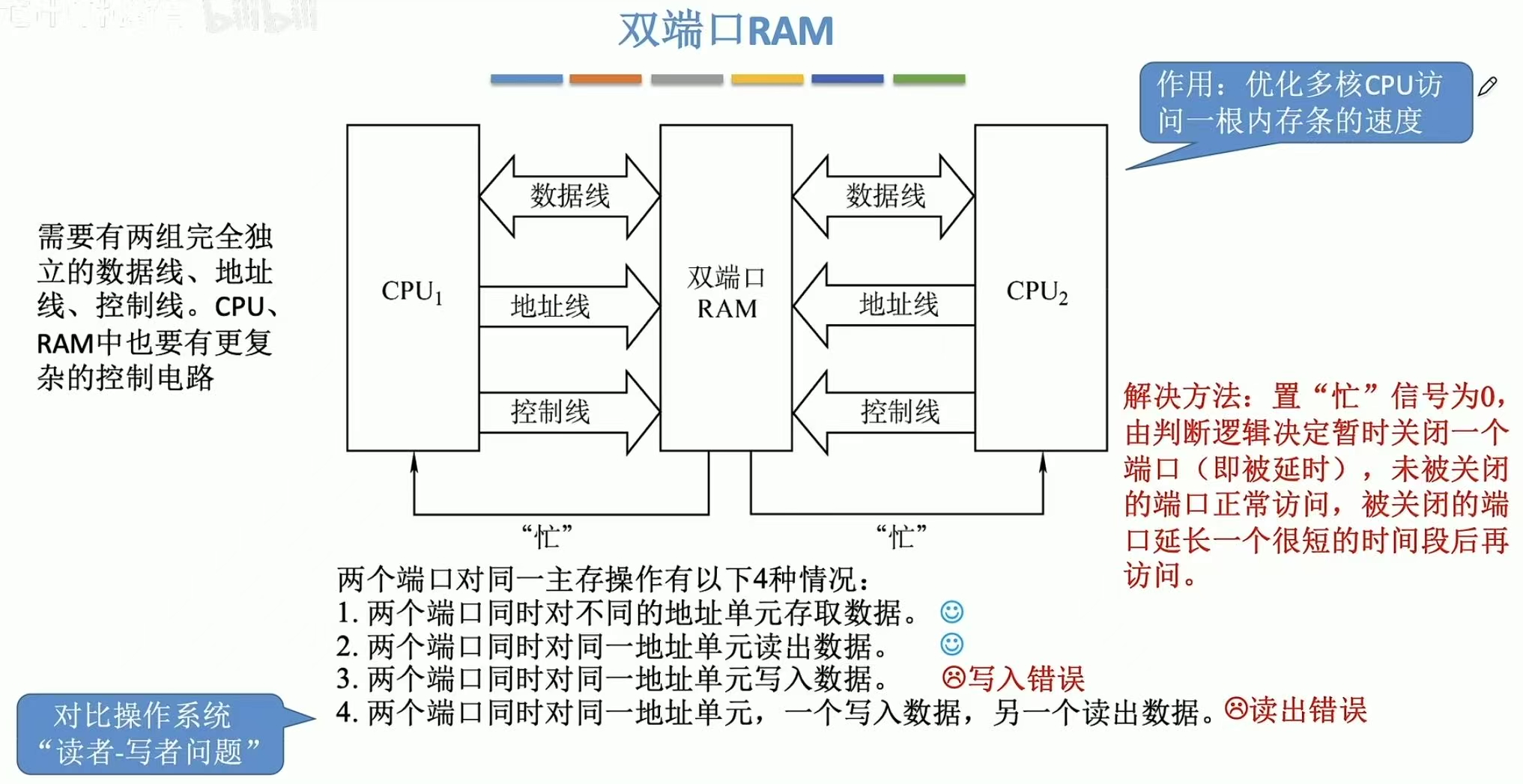

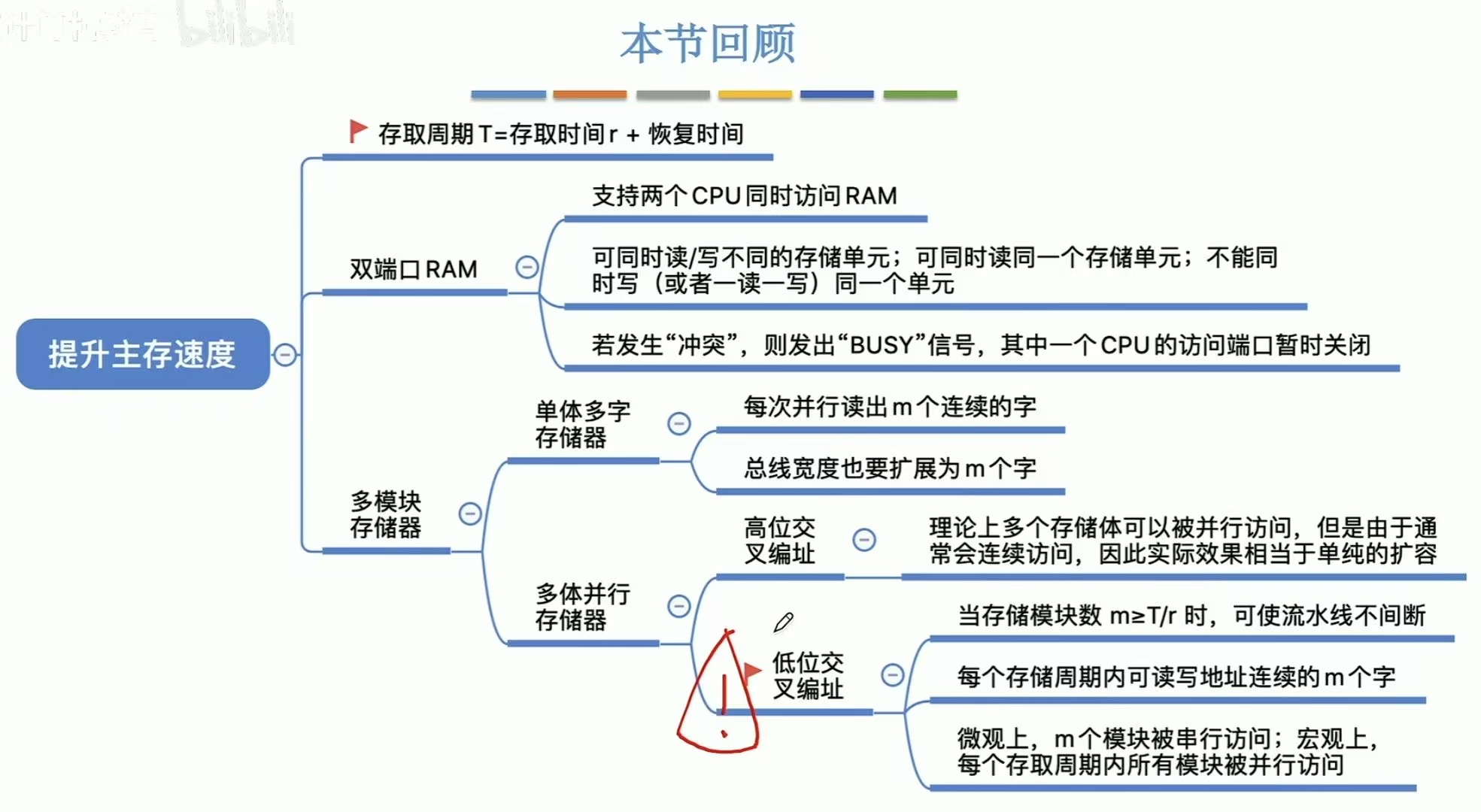

1. 双端口RAM(了解)

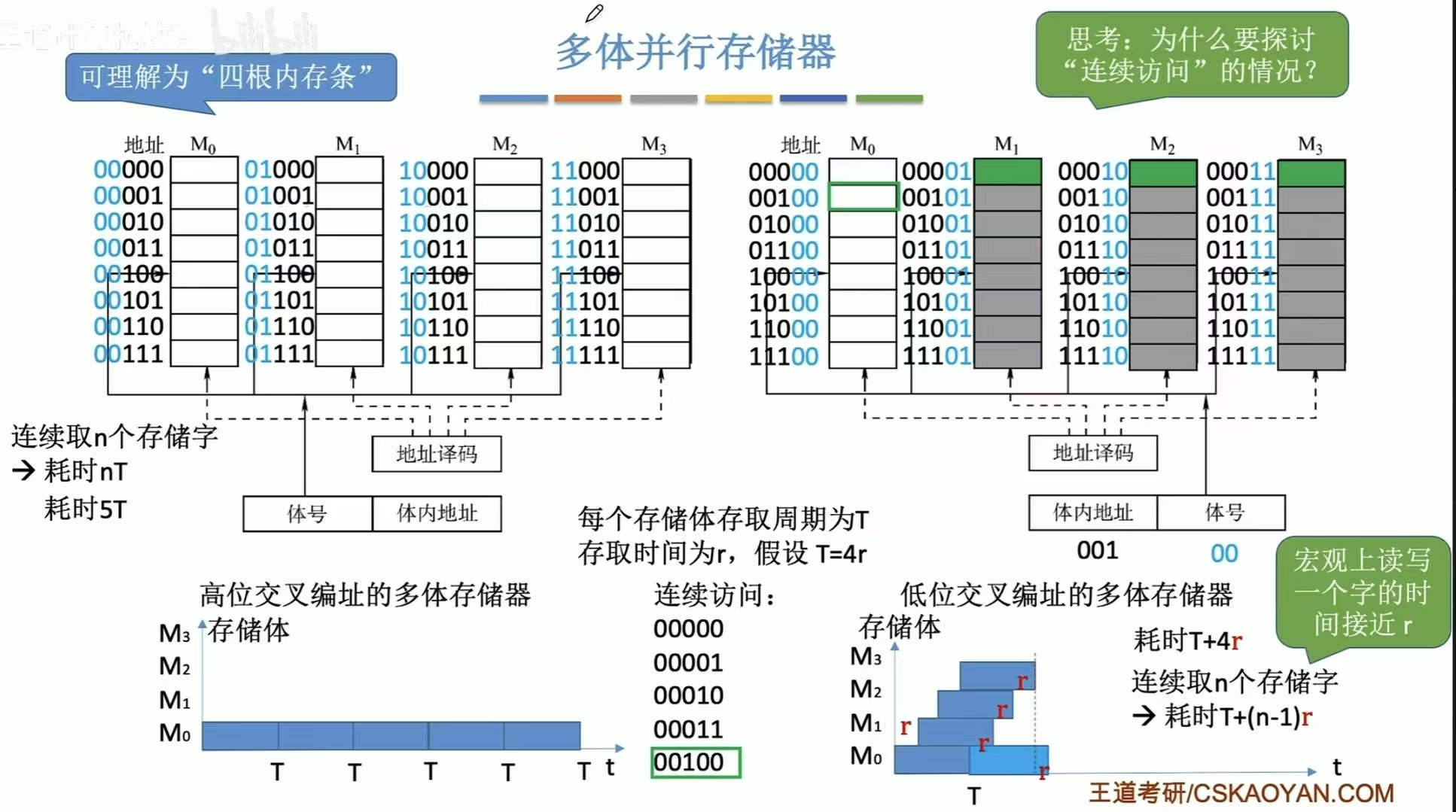

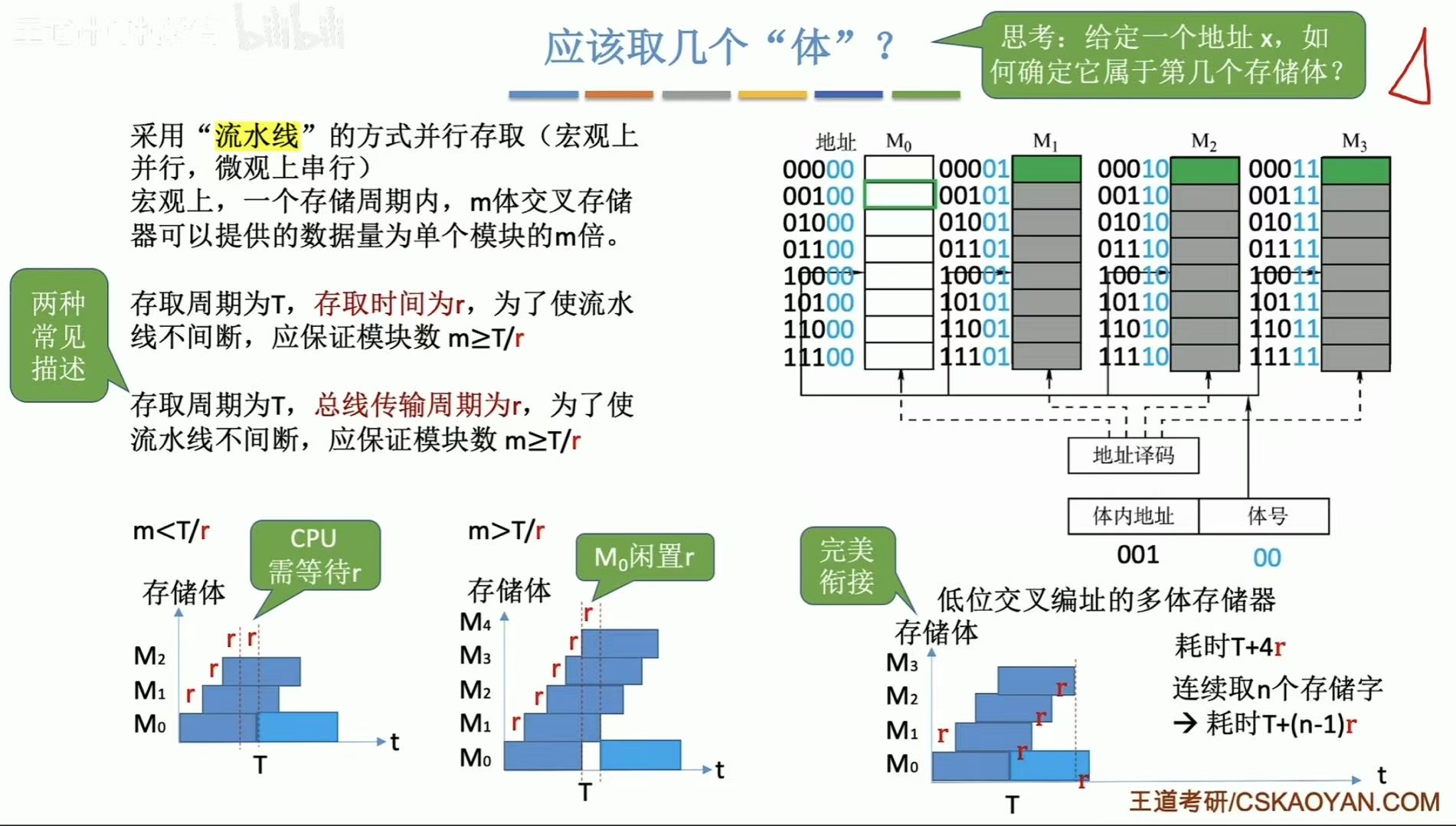

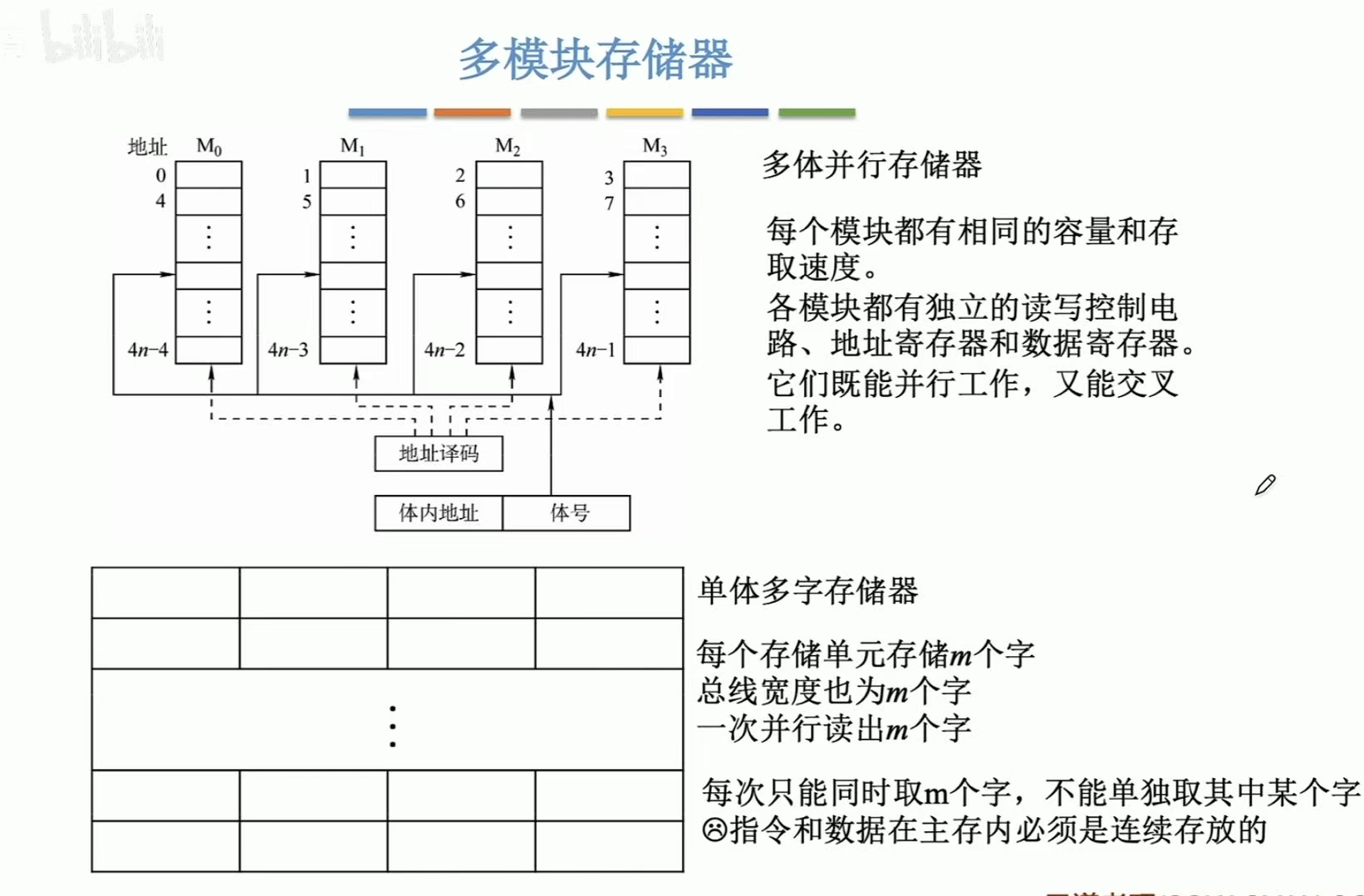

2. 多体并行存储器

高位交叉编址:按照前两位分类

低位交叉编址:按照最后两位分类

m=T/r

3. 小结

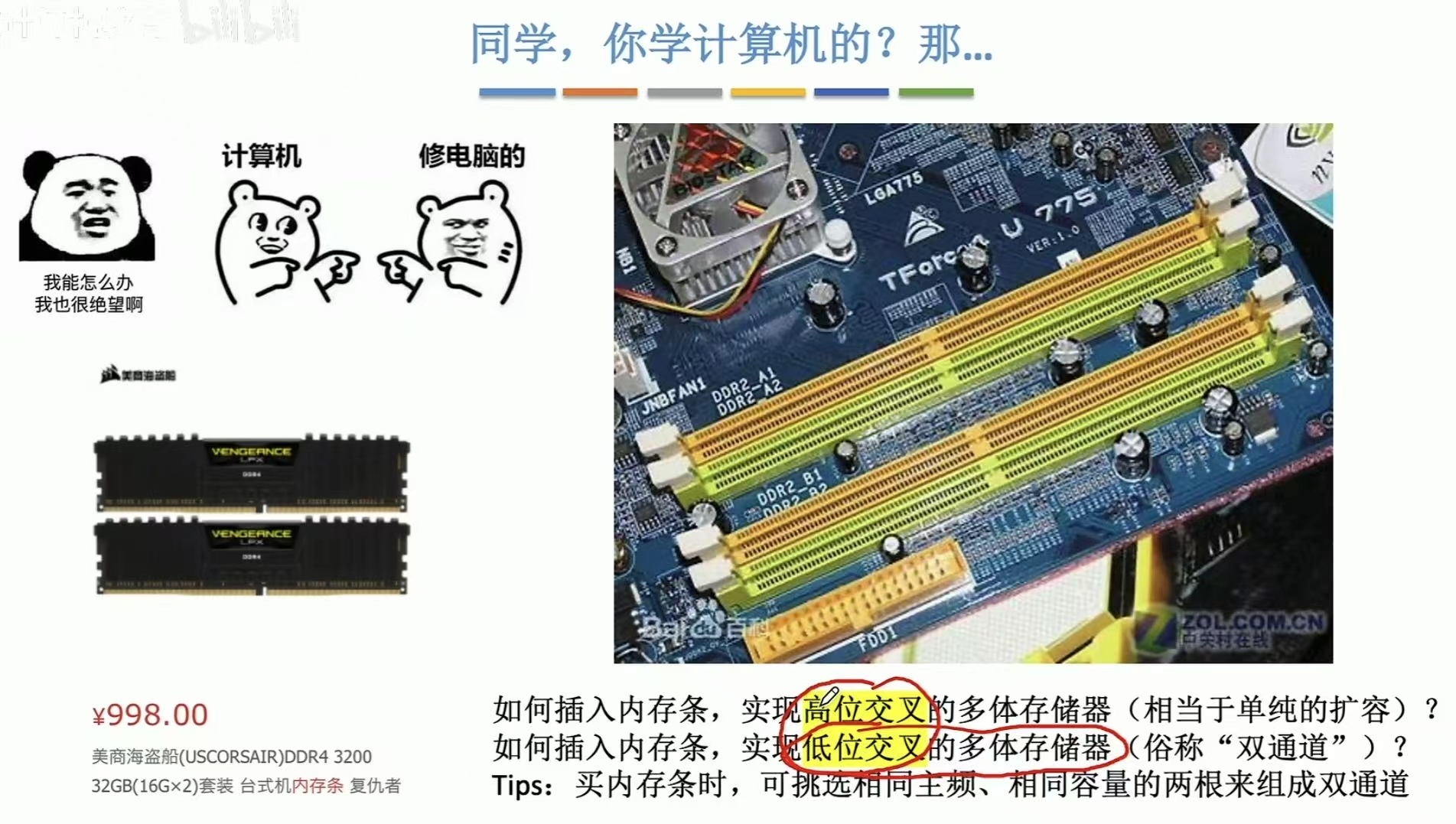

4. 拓展

简单来说:多模块存储器就是多插入了一个内存条,可以实现两个内存条同时访问CPU提高运行速度的结果。

加入同色的卡槽中就实现了低位交叉,加入异色的卡槽就实现了高位交叉。

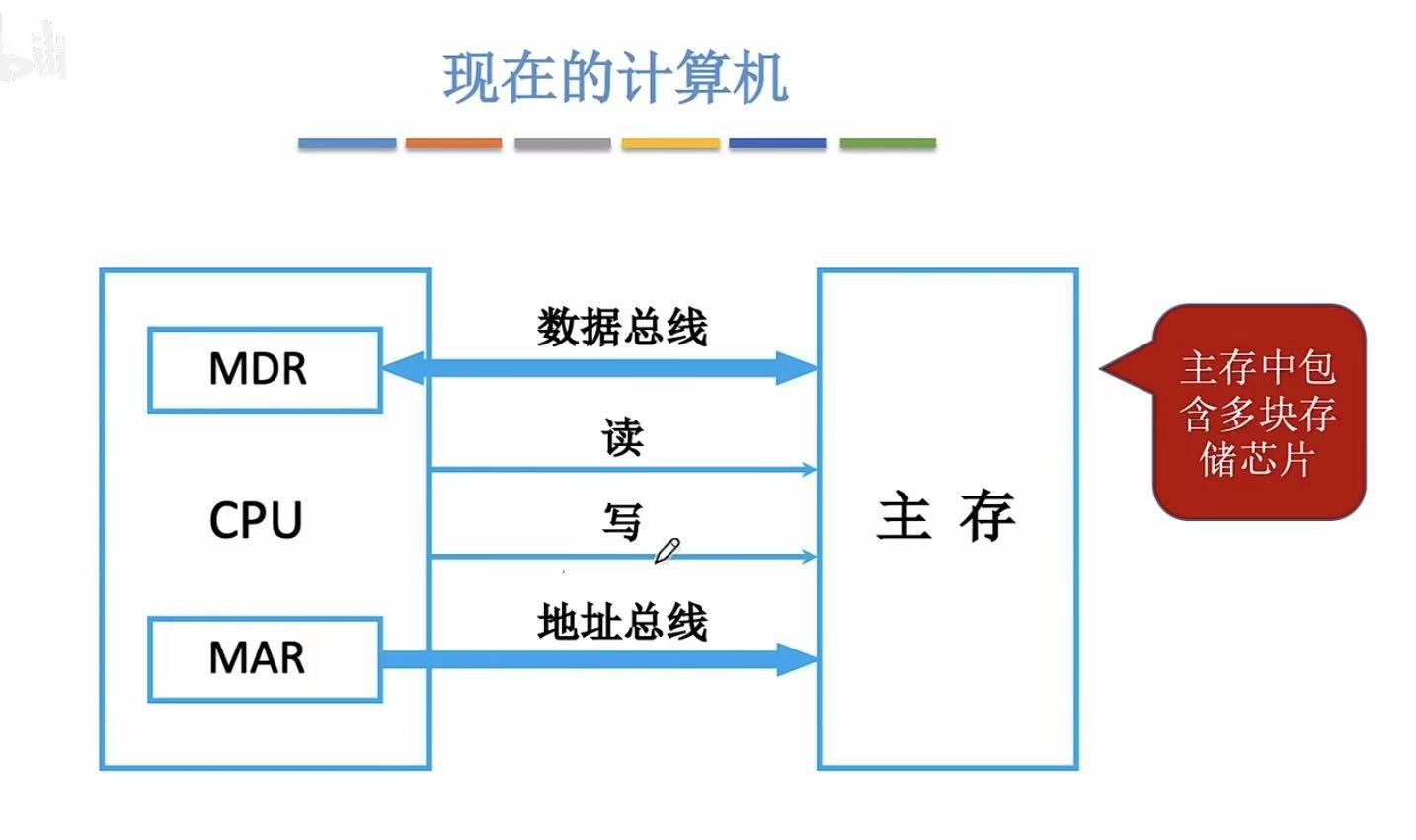

主存储器与CPU的连接

1. 前言

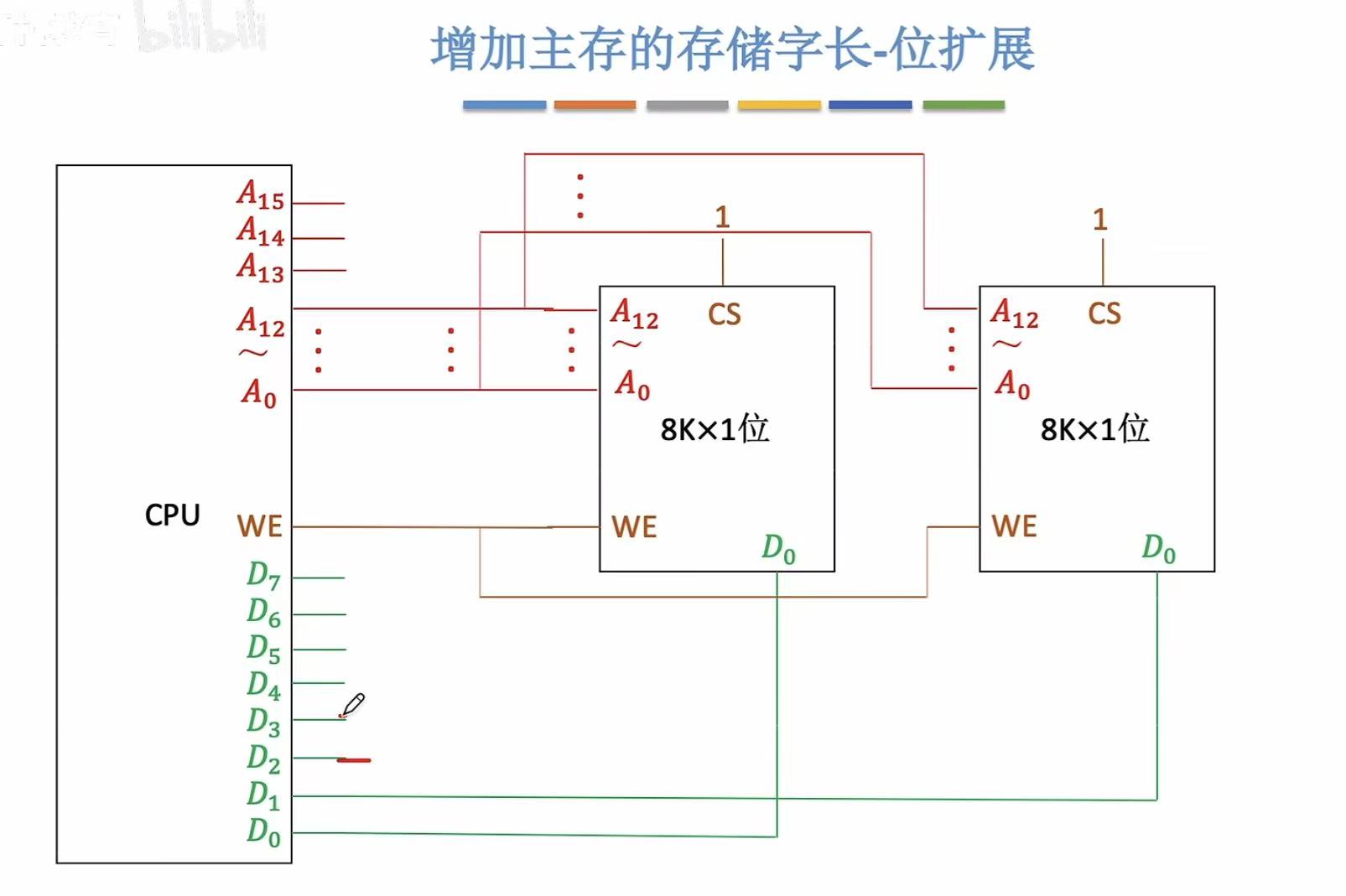

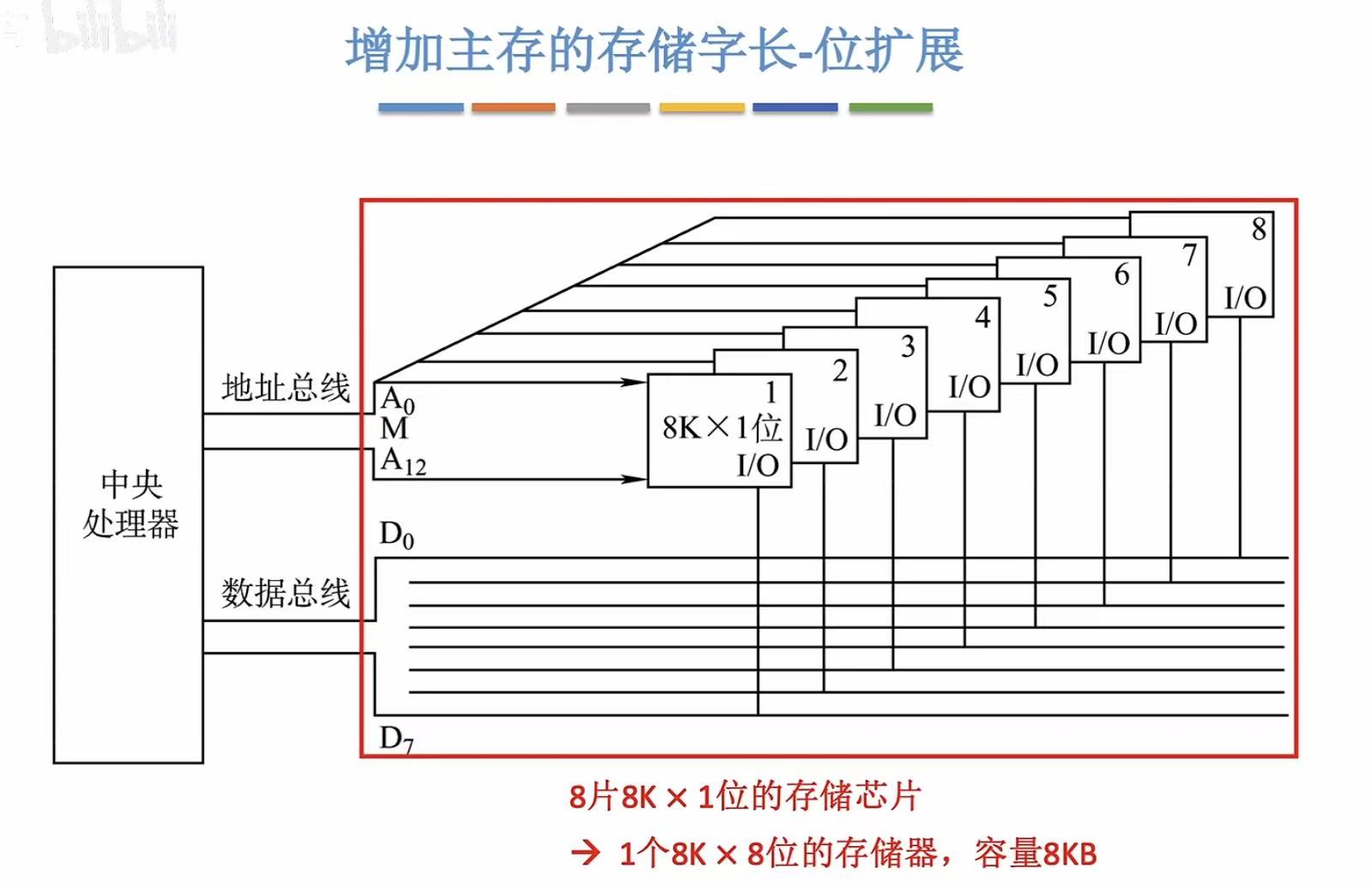

1. 位扩展

8=23-->K=210-->3+10-->13根地址线-->A0~A12-->用了13条地址线,还剩3条

就是通过不断增加 8K×1位 的这个单元,来实现位扩展。

新增加的单元,也要绕道前面去连接地址总线和写控制线和数据总线.(就是CPU中的线,新增的也要和前面的单元一样接上)

地址总线连接的没有变,主要是增加数据总线的连接,因为一个单元只能连接一个数据总线。

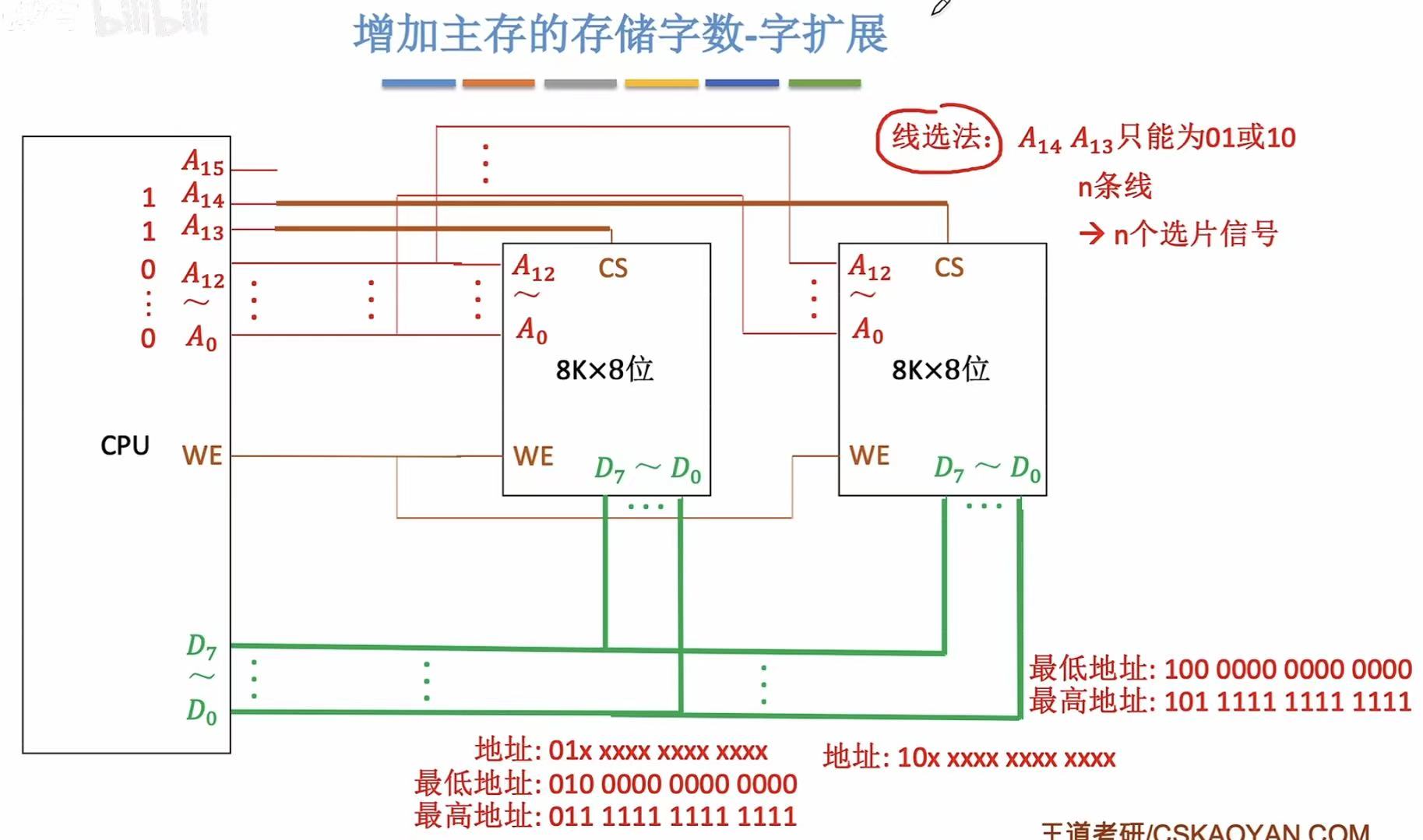

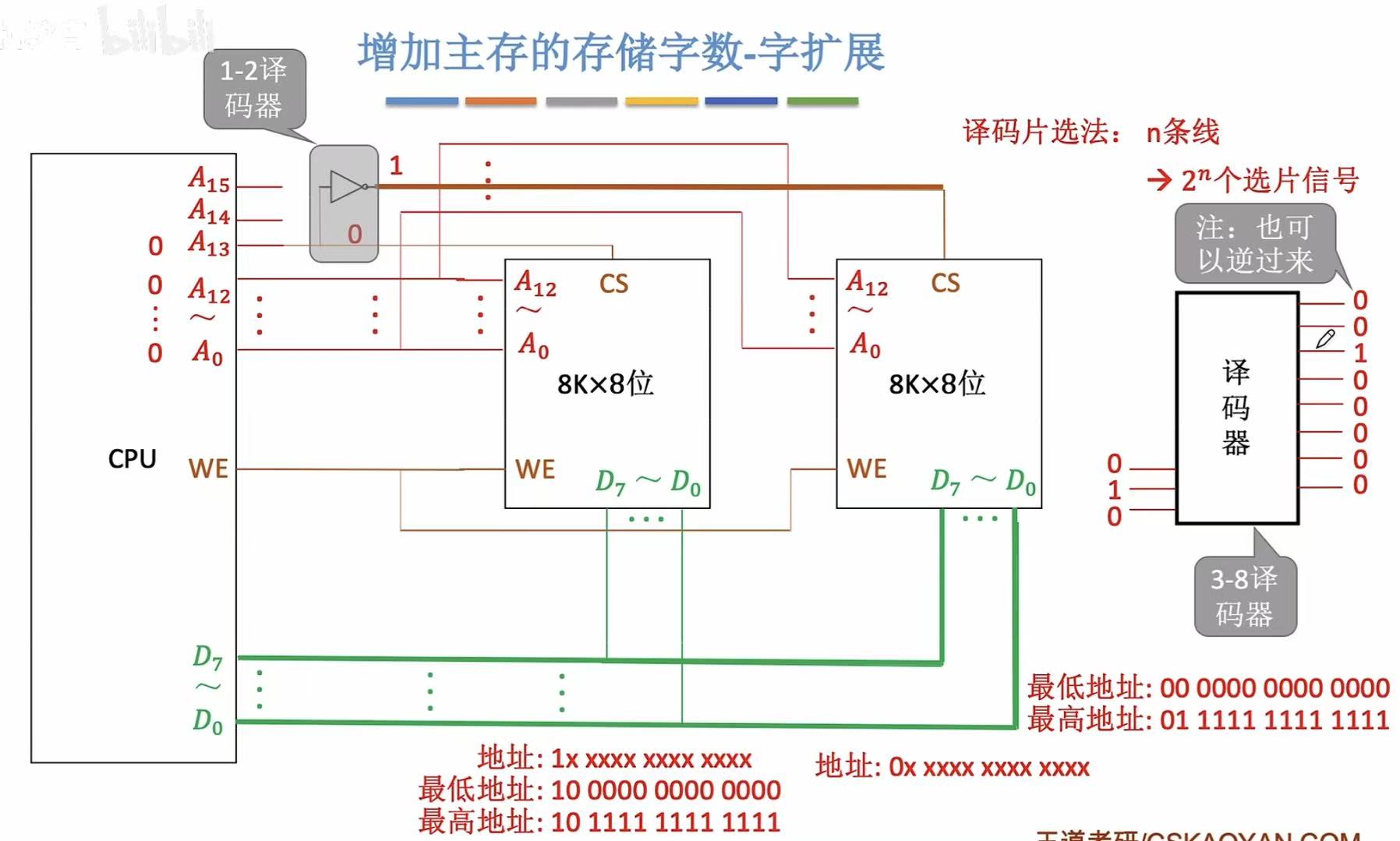

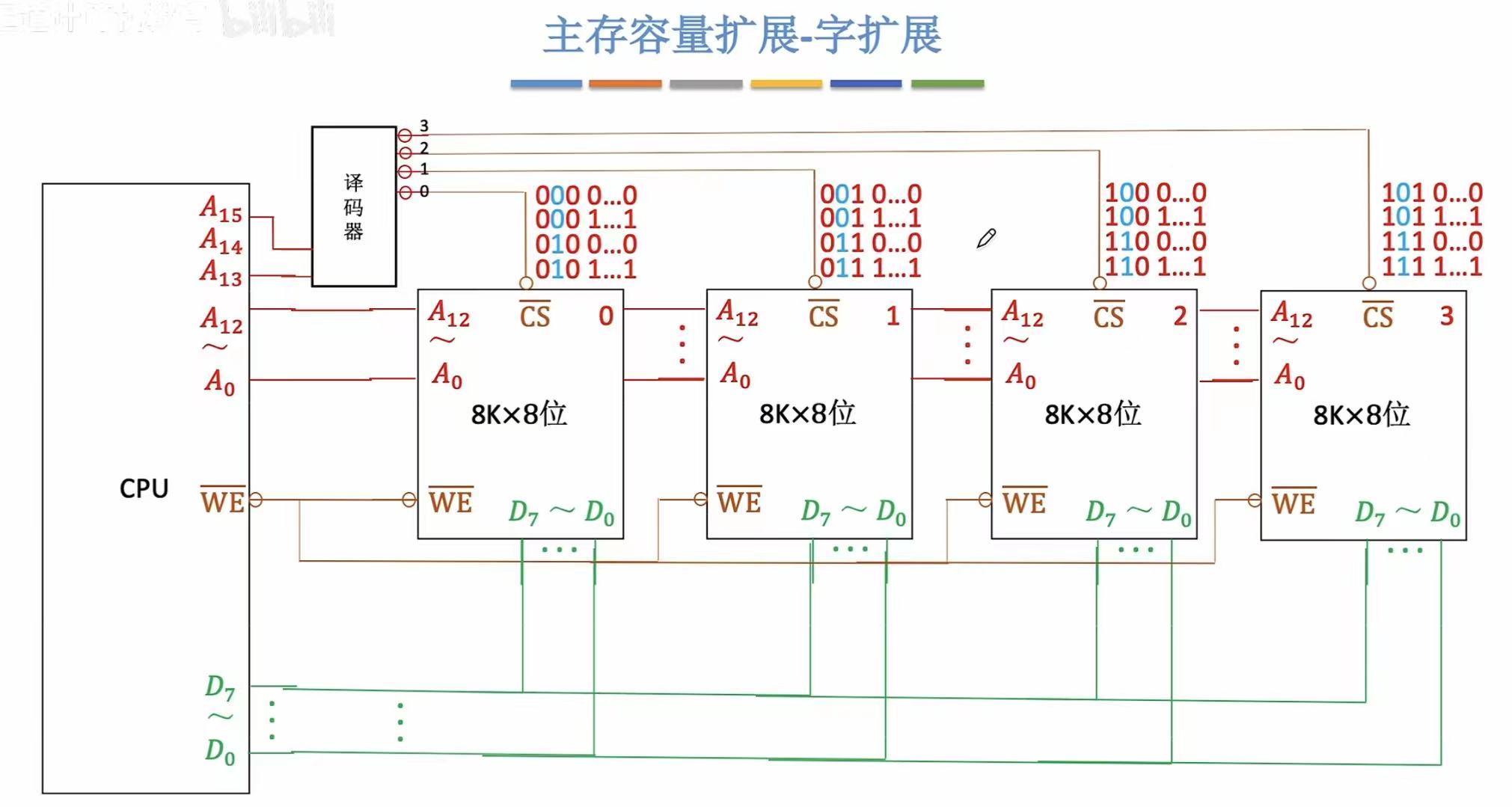

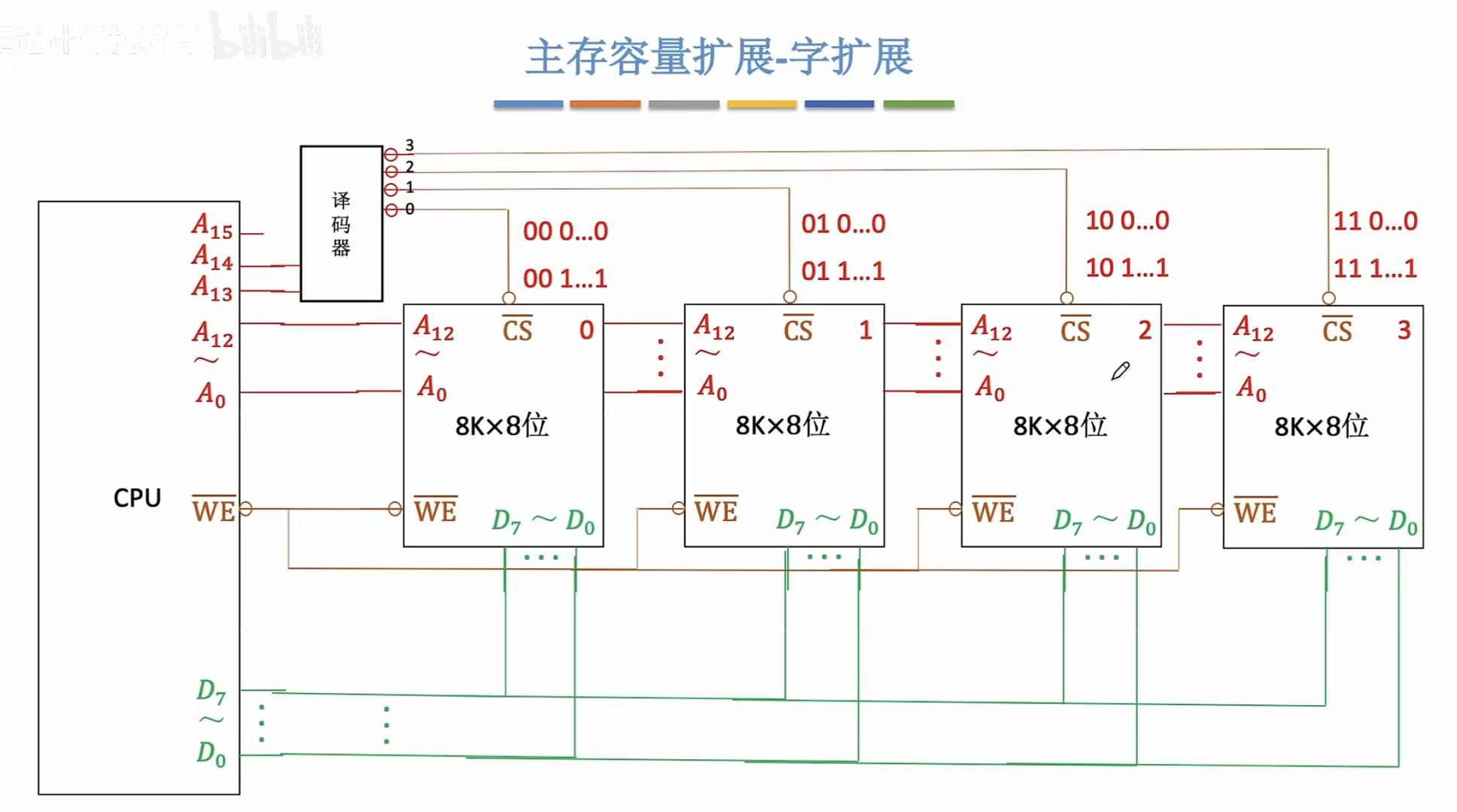

2. 字扩展

因为位扩展剩下了3根地址线没有连上,所以利用剩下的地址线来实现字扩展。

例如:A13=1,则用第一个单元的数据,但是同时A14必须为0,否则就造成访问的堵塞了。

这就是线选法,因为是直接将0或者1赋值给地址线。

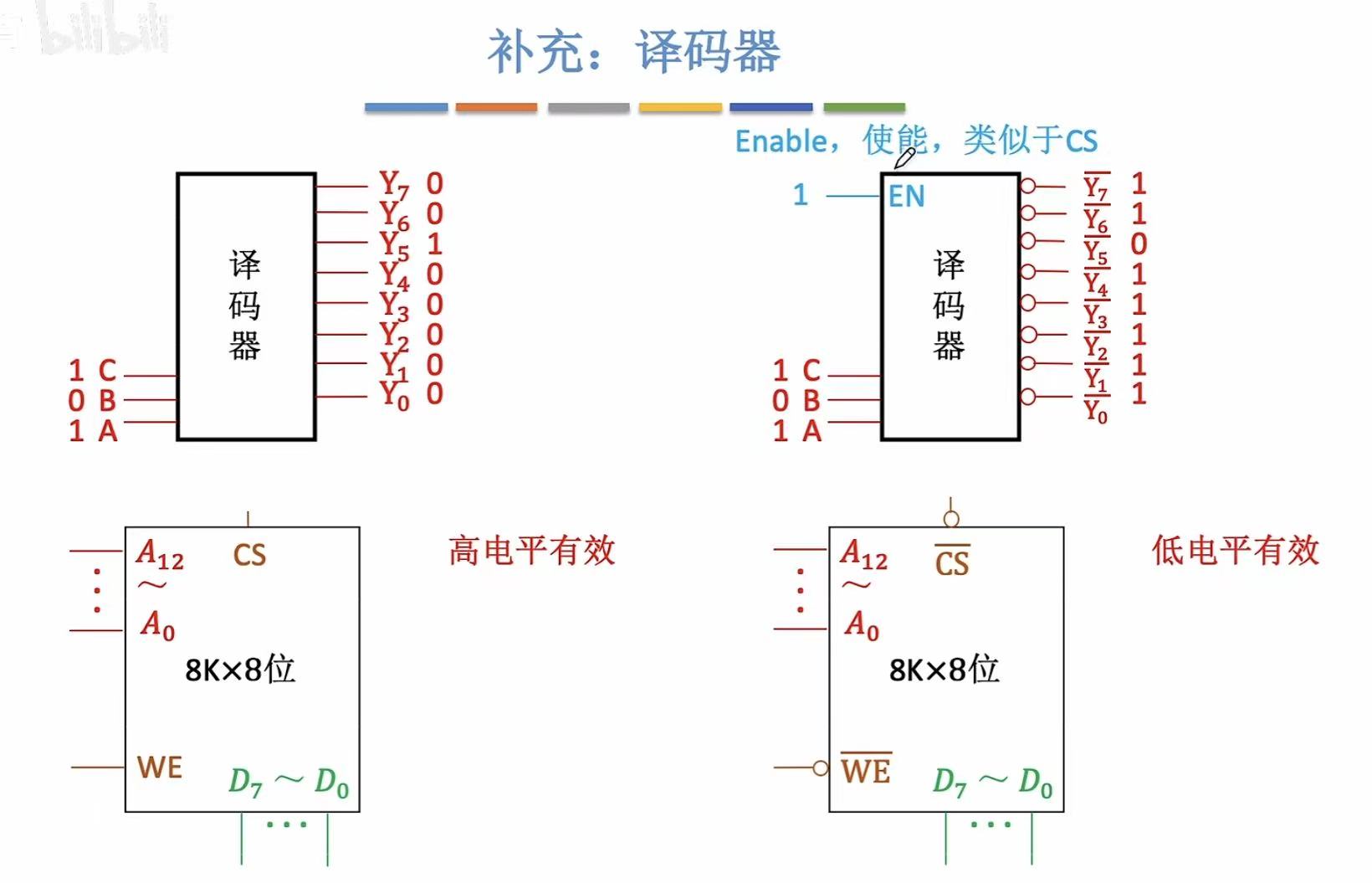

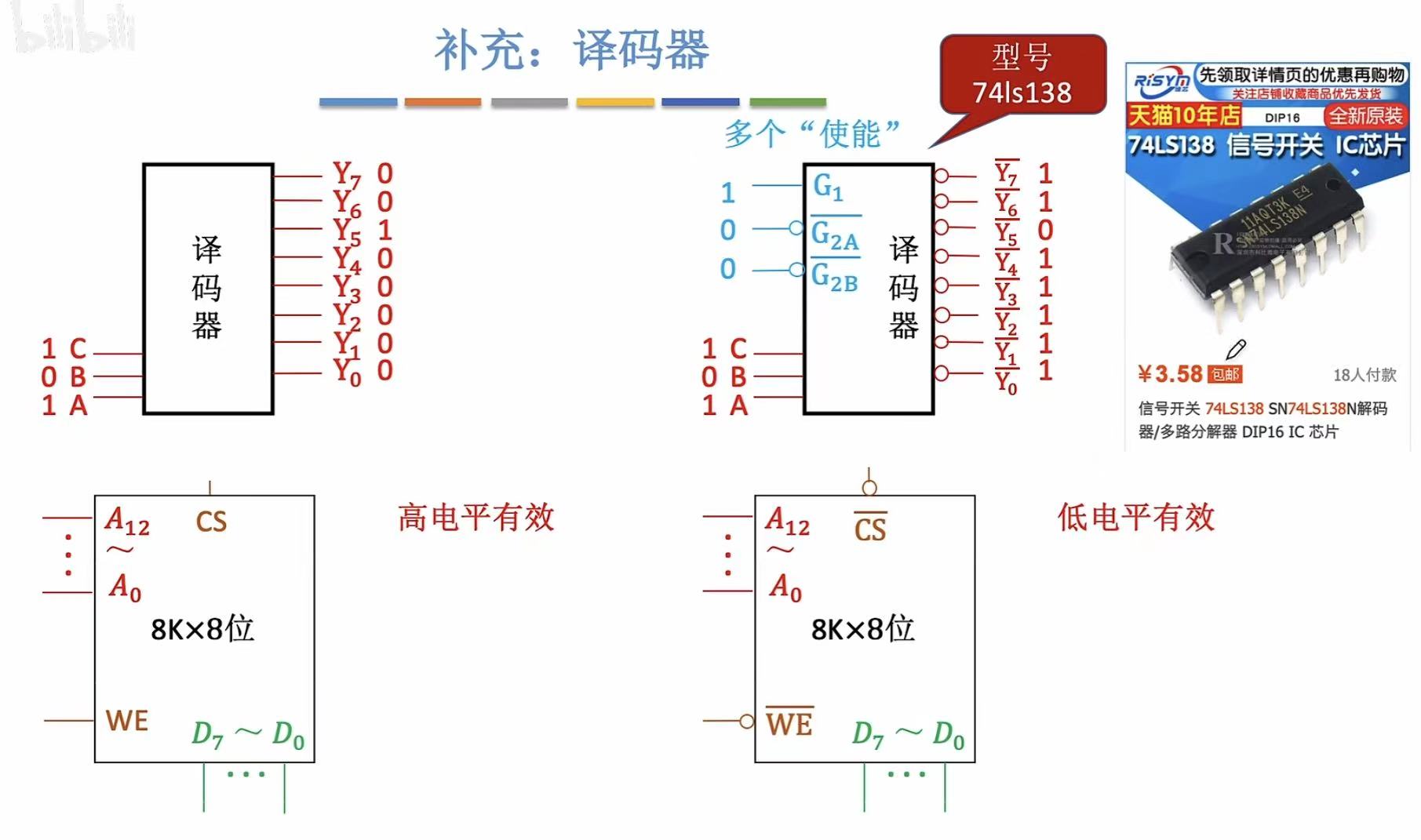

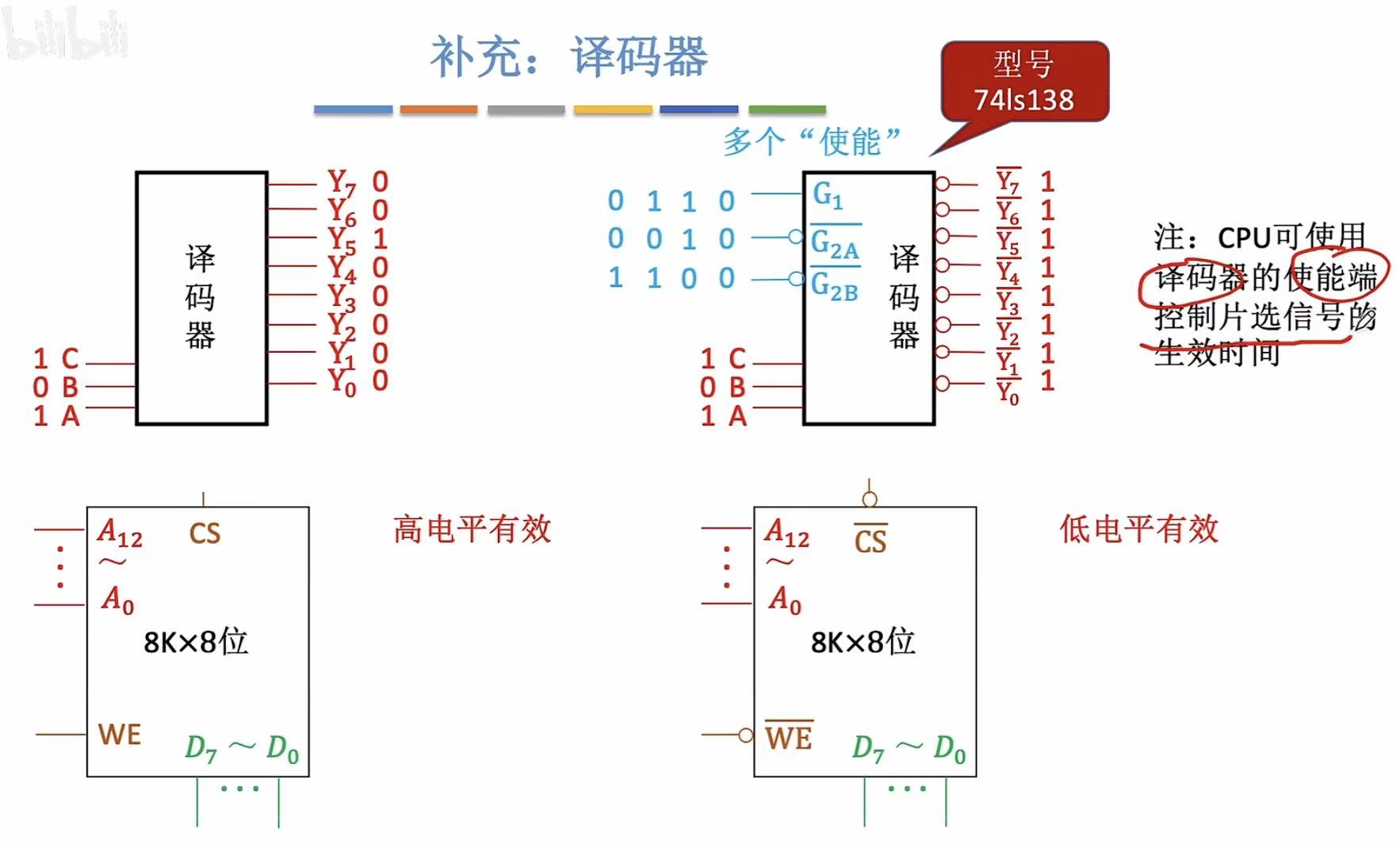

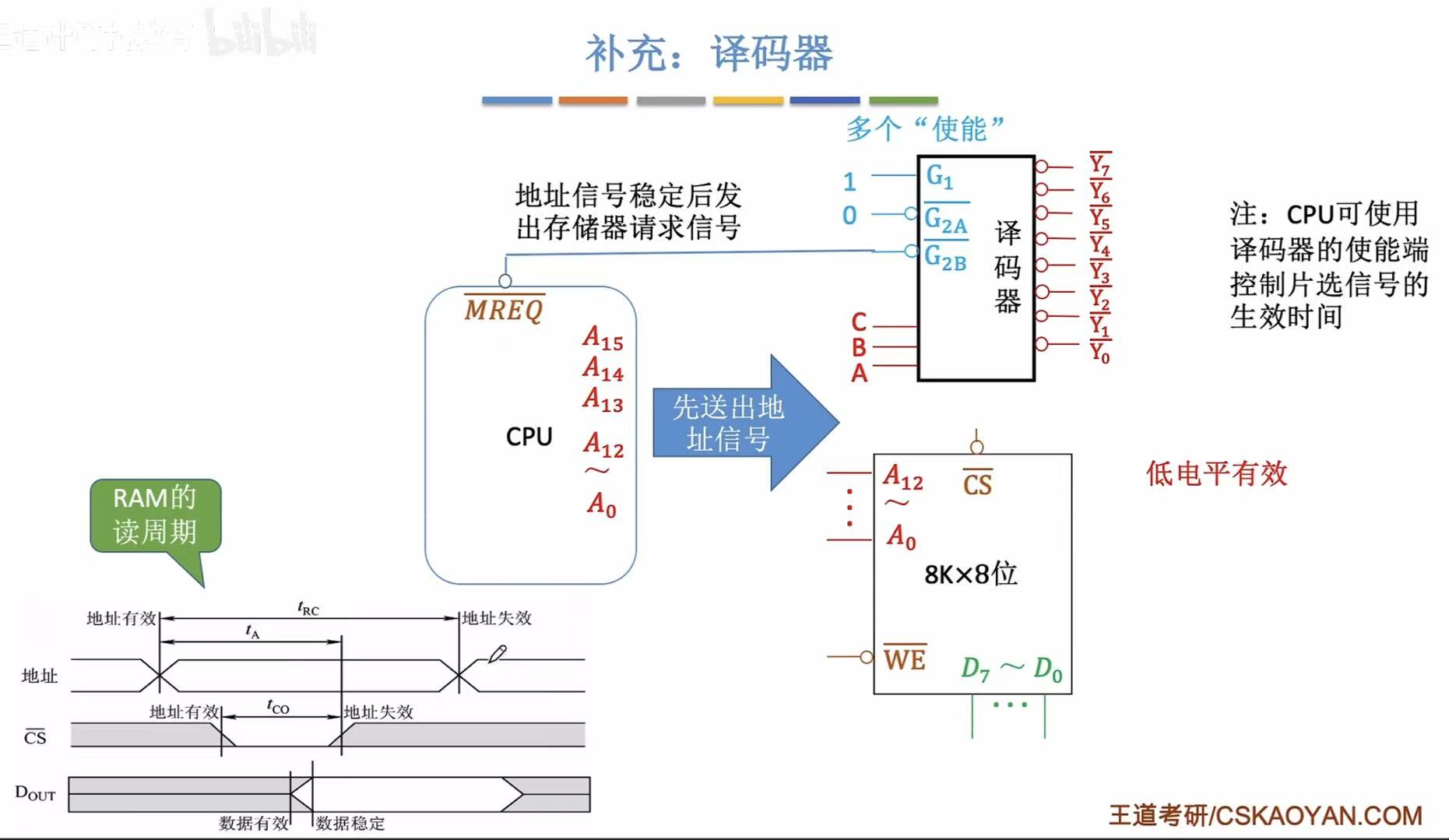

这个方法用到了一个译码器 和非门 ,就可以避免A13、A14同时等于1时产生的错误。

1-2译码器:输入一根线,输出21根线。

3-8译码器:输入三根线,输出23根线。

有的时候可能连接的是A13和A15这两条线,因为A14连不连接都不会影响查询结果。

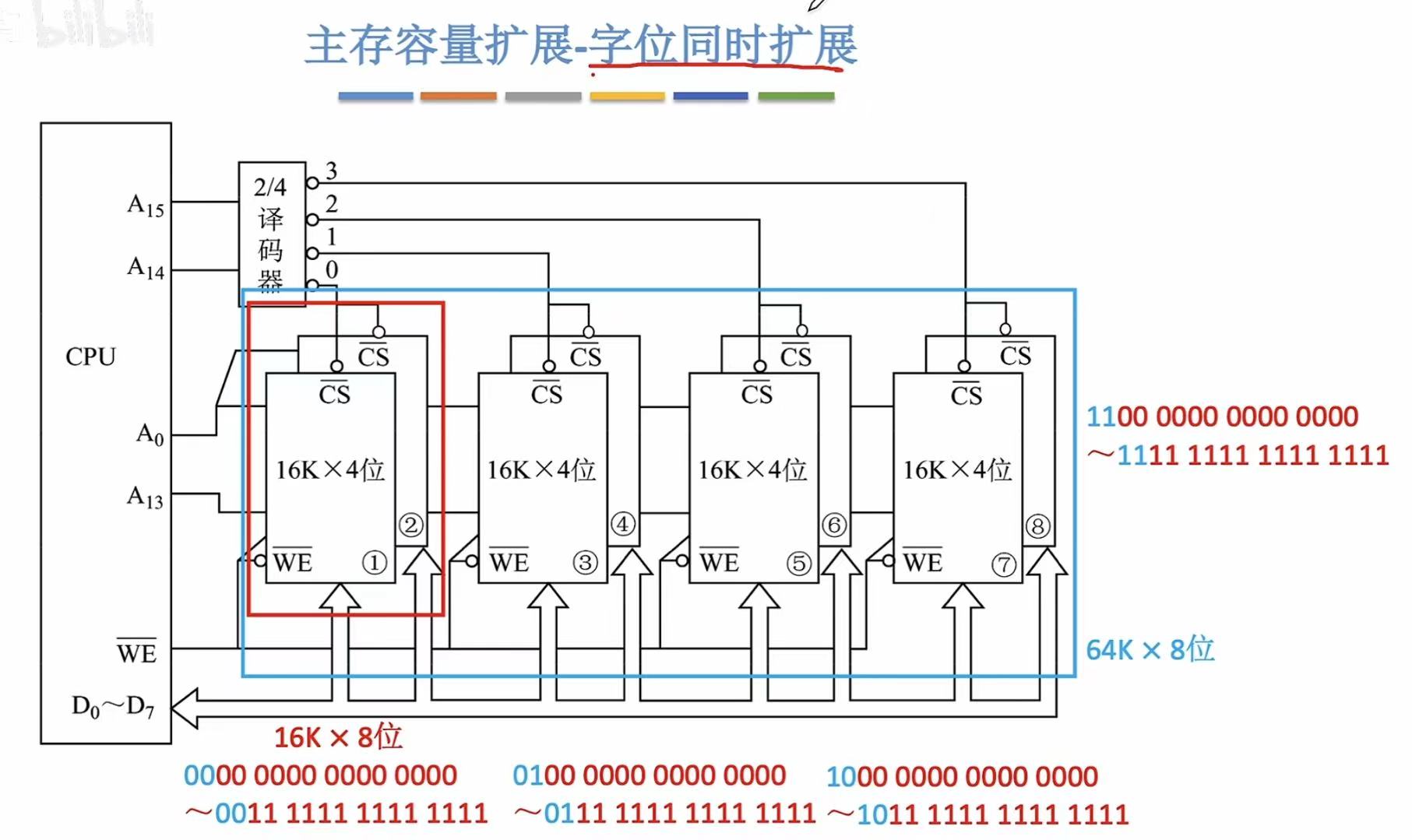

4. 字位扩展

5. 小结

6. 补充-译码器