FFT IP核支持复数形式的正变换(FFT)与逆变换(IFFT)。其关键特性如下:

-

变换点数 :支持

N = 2^m点变换,其中m的取值范围是3到16。 -

数据格式 :支持定点 和单精度浮点 两种数据格式。对于定点格式,输入/输出数据的位宽(

bx)和相位因子的位宽(bw)均在8到34位之间可调。 -

算法与缩放 :提供未缩放定点 、缩放定点 和块浮点三种算法,以适应不同的精度和动态范围需求。缩放因子可在运行时动态配置。

-

接口与输出 :采用AXI4-Stream接口 ,输出顺序可选择自然顺序 或位倒序。

-

存储类型 :计算过程中的数据和相位因子可选择用块RAM(BRAM) 或分布式RAM存储。

四种架构:

| 架构名称 | 核心特点 | 资源占用 | 转换速度 | 适用场景 |

|---|---|---|---|---|

| 流水线 (Streaming I/O) | 连续处理数据,吞吐量最高。 | 最高 | 最快 | 需要最高实时性的高速数据处理。 |

| 基-4突发 (Radix-4 Burst I/O) | 分批次处理数据,使用多个数据复用器。 | 中等 | 中等 | 兼顾速度和资源。 |

| 基-2突发 (Radix-2 Burst I/O) | 与基-4突发类似,但采用Radix-2蝶形单元。 | 较低 | 较慢 | 对速度要求不高的场景。 |

| 基-2精简 (Radix-2 Lite Burst I/O) | 使用单个蝶形处理器,时序复用程度最高。 | 最低 | 最慢 | 对资源极度敏感,对速度无要求。 |

关键配置参数说明

在Vivado中配置IP核时,以下几个参数需要特别注意:

-

转换点数:决定了单次FFT处理的数据长度,直接影响计算延迟和资源使用。有些架构支持运行时动态改变点数。

-

缩放方案 :与数据精度和溢出风险直接相关。块浮点(Block Floating Point) 方案能在保证精度的同时有效防止溢出。

-

输出顺序 :选择自然顺序时,输出频率点是从低到高排列的,更符合直观认知和后续处理需求。

-

通道数 :IP核支持多通道输入,可以对多个独立的数据流进行时分复用处理

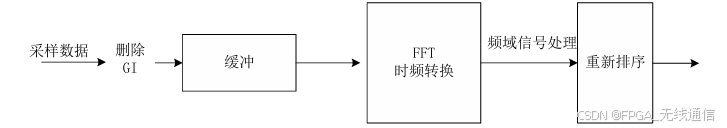

设计目的:

把LT1,LT2进行时频域转换,同时把signal域和data域的保护间隔循环前缀剔除,并进行时频域转换,最后把pilot导频取出来,供剩余的频偏矫正和采样相位纠正。

流程图:

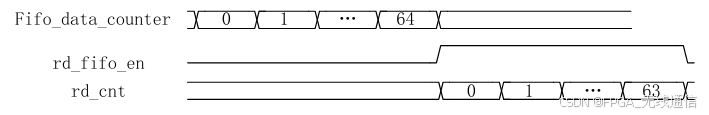

对于缓冲模块FIFO,一次存储够了64点,送入FFT进行运算;

200M时钟处理FFT,输入的信号是以20M为采样周期进来的;

长训练序列不需要取出循环前缀,因为在前面模块已经移除了;

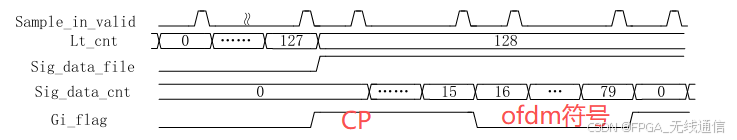

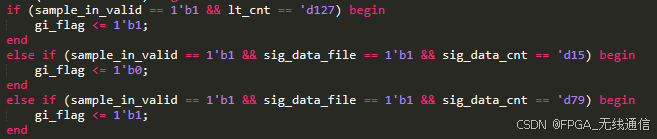

写入时序:

通过写入FIFO,就可以实现剔除CP;

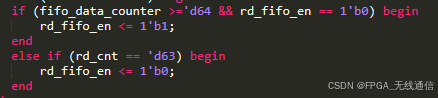

FIFO读出时序:

利用counter 的计数,64时证明FIFO内部够 64个数据,就给到FFT;

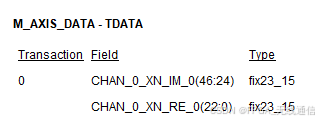

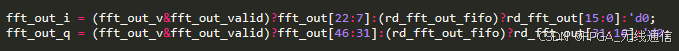

FFT 输出的数据不是16位,I Q都是23位,需要截取23位里面的高 16位进行重新排序输出;

其中,[22:7]是 i 取FFT IP输出的低23位中的高16位;后面[15:0] 是FIFO输出的,因为FIFO输入是已经拼接好的32位, 直接取即可;Q 是一样的;

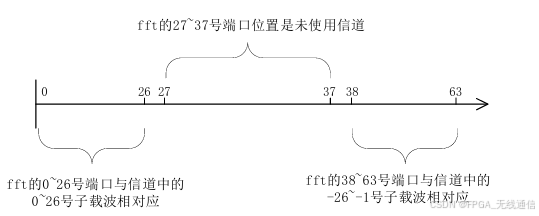

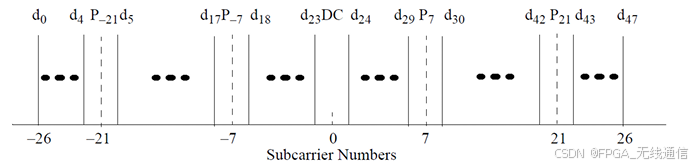

FFT 输出选择自然序列,那么输出频点是DC 1....31 -32....-1这样顺序.

需要转成-26...-1 +1...26 总数52个信道数据,不需要直流DC信道

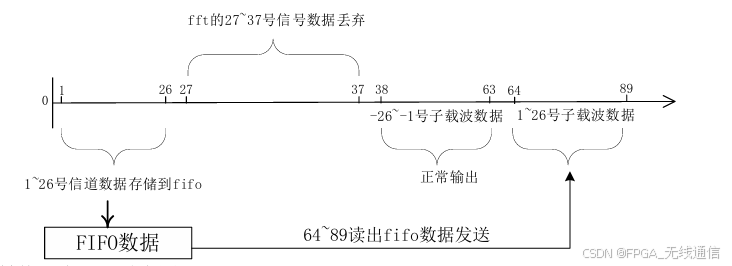

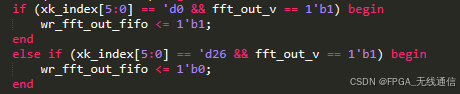

利用FIFO 对FFT输出数据进行排序,0为DC ,丢弃:

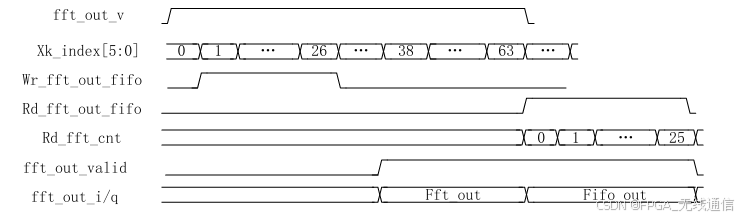

时序:

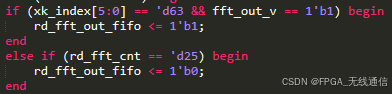

提取导频信号用于后续的采样频偏和剩余频偏的跟踪和剔除

其中从-21,-7,7,21中提取出来进行后续使用

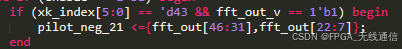

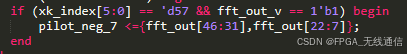

Xk_index 等于 43 时是-21信道数据,等于57时是-7信道数据;

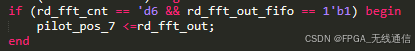

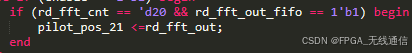

Rd_fft_cnt 等于 6 时是7信道的数据,等于20时就是21信道数据;

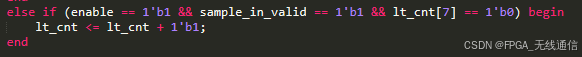

筛选长训练序列:

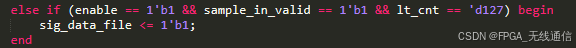

信号域起始位置:

信号域的80个采样点:64个采样点+16个循环前缀

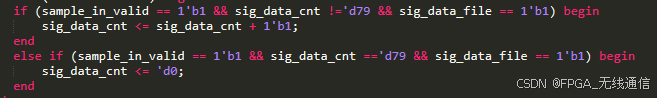

剔除CP,将OFDM符号存入FIFO标志:

根据 fifo_counter 输出64个数据:

输处的数据给到FFT IP核,从FFT 输出后进行重新排序,先将 1~26存入 fifo;待FFT 输出到第63个采样点后,将FIFO数据读出,完成重新排序;

其中,FFT的 m_axis_data_tuser 信号就是 xk_index;

最后取导频:{Q,I},FFT IP 的输出结果;