《FPGA基础知识》系列导航

本专栏专为FPGA新手打造的Xilinx平台入门指南。旨在手把手带你走通从代码、仿真、约束到生成比特流并烧录的全过程。

本篇是该系列的第二十一篇内容

上一篇:FPGA基础知识(二十):Xilinx Block Memory IP核(5)--ROM 详解_xilinx rom-CSDN博客

此篇为FPGA基础知识系列的最后一篇;

通过这一个系列我们对FPGA的使用从并行结构到时钟复位、计数器、状态机、引脚约束和时钟约束,时序、以及常用的IP核,常见原语都有了一定的了解,之后就是进行实际的设计了。

接下来会重新开一个系列,以K325T开发板为平台,做一些测试例程的讲解,敬请期待~~~

1 什么是FPGA原语?

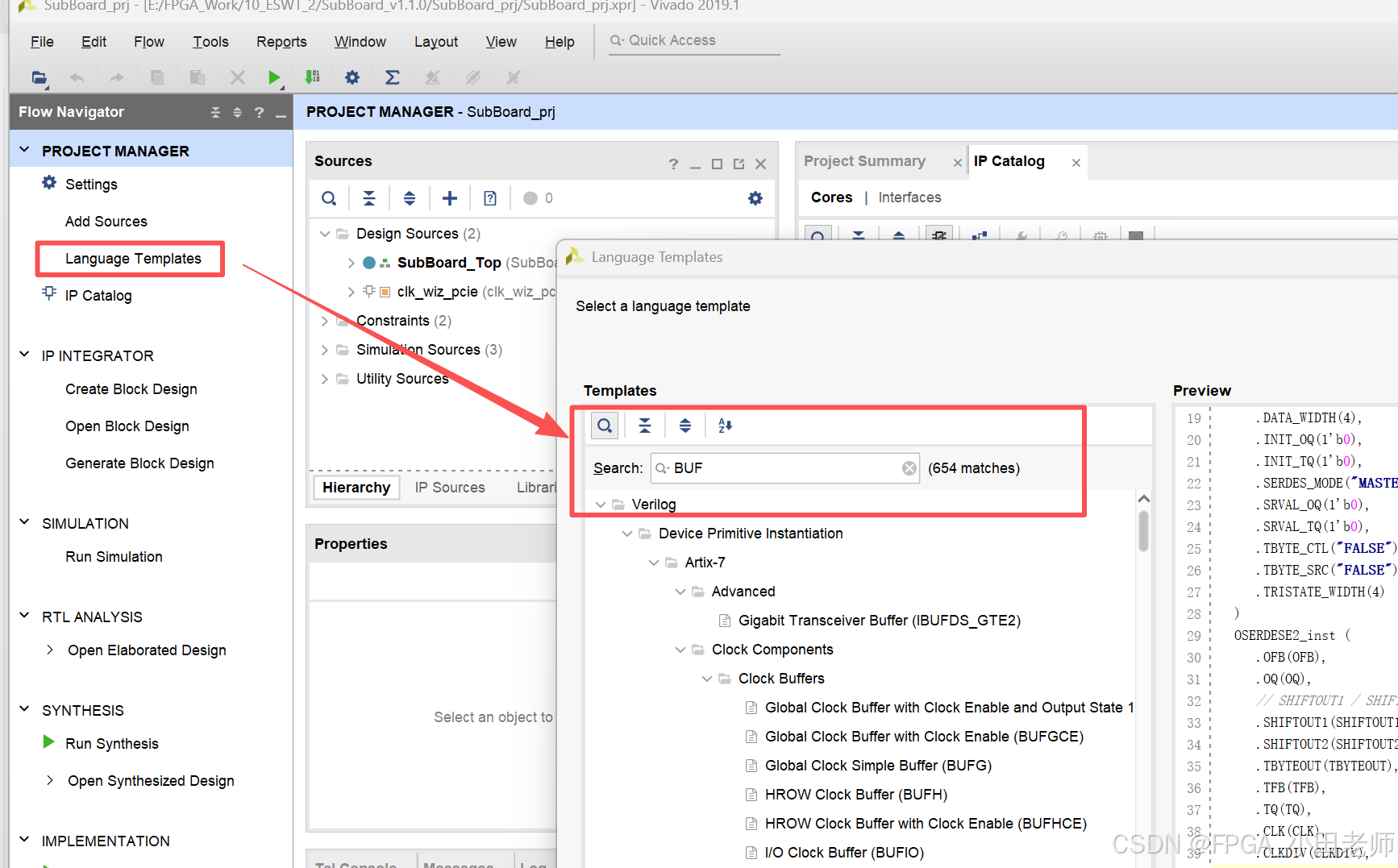

原语是FPGA中最基础、不可再分的硬件单元,它们直接映射到芯片的物理资源。如果说Verilog/VHDL是建筑设计图,那么原语就是砖块、钢筋和水泥。打开vivado软件,我们可以在如下的位置进行原语的检索

2 常用原语解析

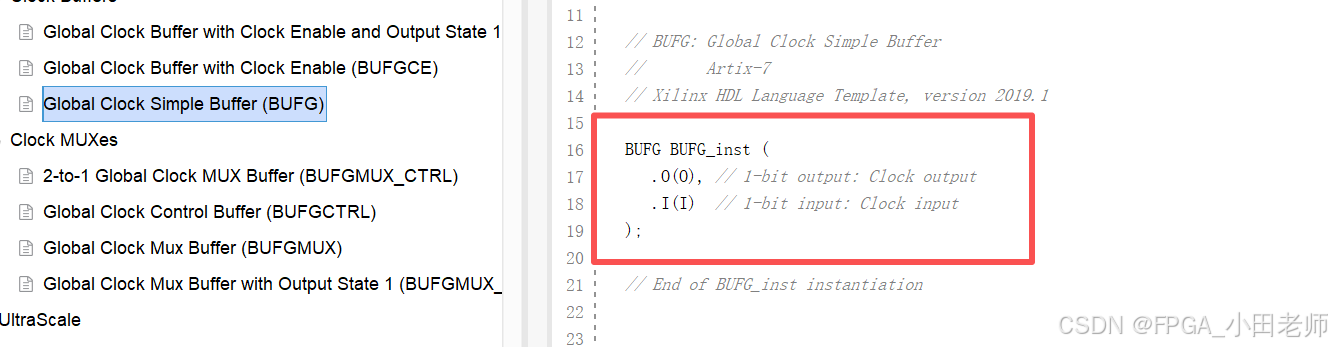

2.1 BUFG

全局时钟缓冲器 主要是当时钟驱动力不足的时候使用

那一般情况下咱们外部输入的时钟都会有输入约束,就不需要用这个,再就是clock wizard生成的时候,也会自带bufg 也是不需要用的;

当我们使用外部时钟,自己在内部通过计数器产生的时钟信号的时候,一般都是需要用BUFG做一次缓冲。

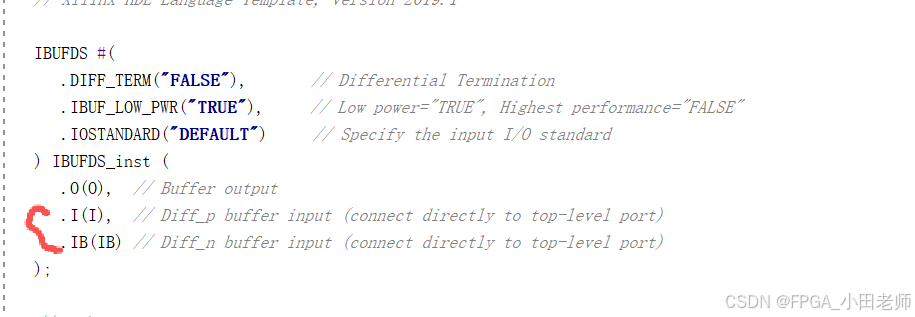

2.2 IBUFDS

差分输入缓冲器 他的目的是将咱们外部输入的差分信号转为内部单端信号

这个IBUFDS一般需要跟BUFG一起使用的哈 就是我们的差分时钟经过IBUFDS变为单端时钟,需要再经过BUFG之后才能作为我们程序中的时钟使用 这里要注意。

2.3 OBUFDS

差分输出缓冲 将咱们内部单端信号转为差分信号输出。

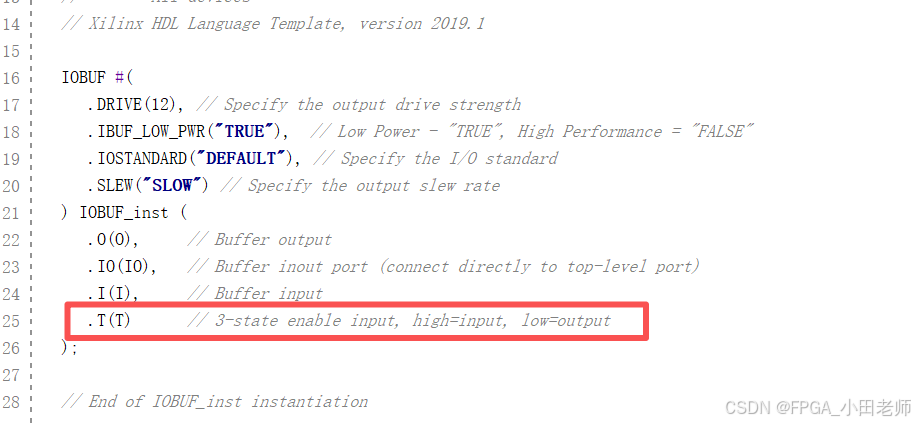

2.4 IOBUF

即双向缓冲,主要针对inout信号 通过双向信号选择引脚,选择到底是输入还是输出

3 总结

FPGA原语是连接RTL代码与物理硬件的桥梁。掌握原语,意味着你:

-

真正理解了FPGA的硬件结构

-

能够设计高性能、高可靠性的系统

-

可以解决最棘手的时序和信号完整性问题

-

站在了硬件设计的最前沿

记住:伟大的建筑师从不嫌弃砖块,伟大的FPGA工程师从不忽视原语