副标题:通过 QSPI 引导 SD / eMMC 系统镜像的工程化启动与升级方法

1. 方案概述(做什么,解决什么问题)

本方案用于 ZYNQ / ZYNQ MPSoC 平台,在 QSPI Flash 固定存放 BOOT.bin 的前提下,通过 U-Boot 引导 SD 卡或 eMMC 中的 Linux 系统镜像 ,并支持在工程现场通过 U 盘完成系统升级。

核心解决的问题:

- QSPI 不反复擦写大镜像,仅承担启动与调度职责

- Linux 系统(Kernel / DTB / RootFS / FPGA bitstream)可独立升级

- SD / eMMC 启动方式统一,升级路径一致

- 出现升级失败时,可快速回退到已知可启动状态

该方案面向工程交付与长期维护,不追求最小配置,而强调可控性与可复制性。

2. 启动架构与介质分工

2.1 启动介质职责划分

| 介质 | 职责 | 是否频繁写入 |

|---|---|---|

| QSPI Flash | 固定启动入口 | 否 |

| SD / TF | 调试、应急启动 | 是 |

| eMMC | 量产运行系统 | 是 |

QSPI 中仅存放 BOOT.bin 与 U-Boot 环境变量,不存放 Kernel 或 RootFS。

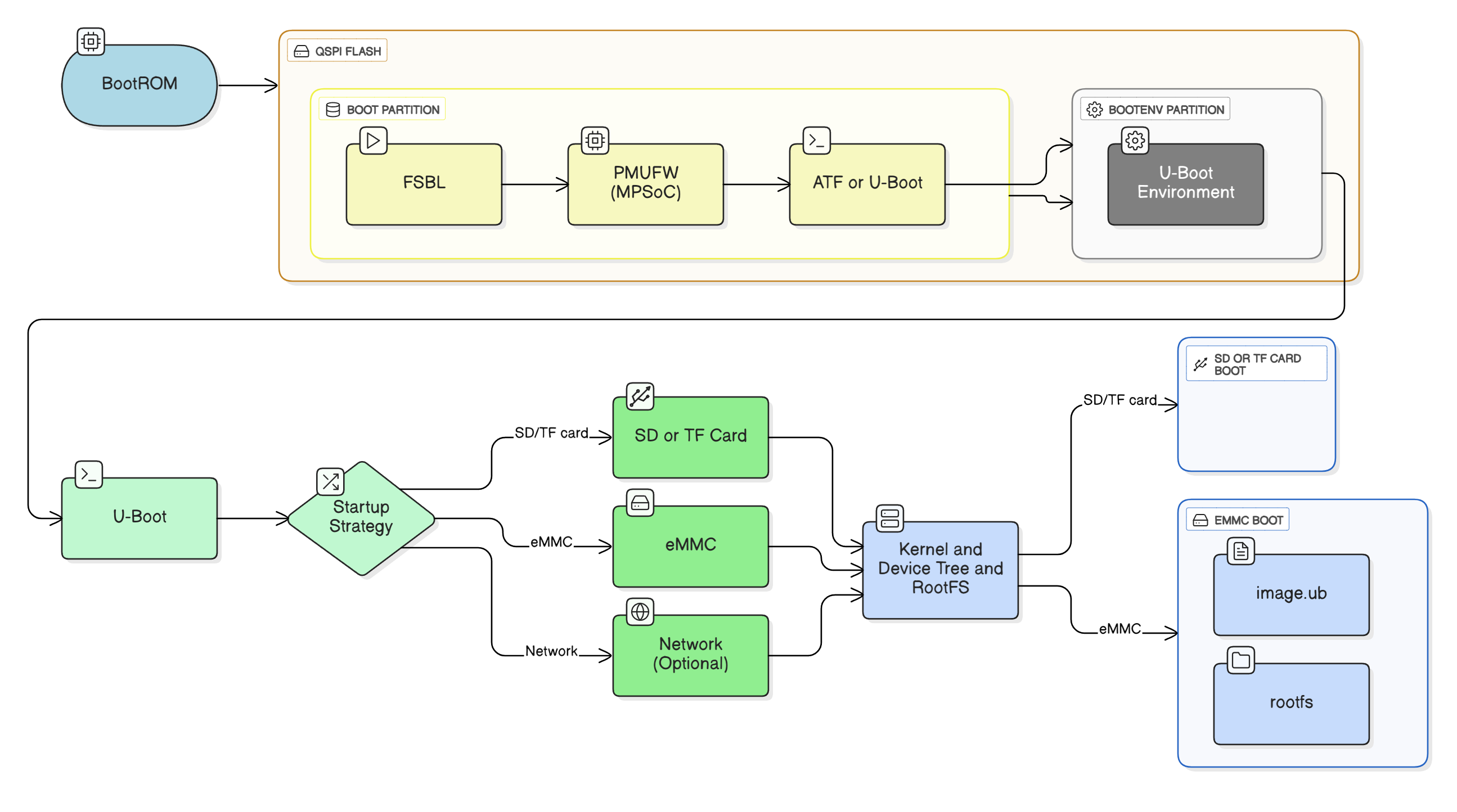

2.2 启动链说明(文字版)

- BootROM 上电后固定从 QSPI 读取 BOOT.bin

- FSBL 初始化 DDR、时钟、必要外设

- U-Boot 启动后读取 QSPI 中的环境变量

- U-Boot 按策略尝试 SD / eMMC

- 从目标介质加载 image.ub、DTB、RootFS

3. QSPI Flash 规划

3.1 MTD 分区定义

| 分区名 | 设备节点 | 大小 | 内容 |

|---|---|---|---|

| boot | /dev/mtd0 | 固定 | BOOT.bin |

| bootenv | /dev/mtd1 | 固定 | U-Boot Env |

3.2 设计说明

- QSPI 中不存放 Kernel 或 RootFS

- 避免大容量镜像反复擦写

- 降低 Flash 老化与升级风险

4. Linux 镜像组织方式

4.1 SD / TF 卡结构示例

/boot

├── image.ub # Kernel + DTB

├── system.dtb # 设备树(可选独立)

├── system.bit.bin # FPGA Bitstream

└── boot.scr # U-Boot 升级脚本

/rootfs4.2 eMMC 分区示例

| 分区 | 用途 |

|---|---|

| mmcblk0p1 | boot / image.ub |

| mmcblk0p2 | rootfs |

5. U 盘升级机制(工程重点)

5.1 升级介质说明

工程升级通过 USB U 盘 完成,U-Boot 或 Linux 系统中挂载为 /mnt/update,目录结构固定如下:

update/

├── ubuntu22.04_u9.tar.gz # RootFS 镜像

├── image.ub # Kernel + DTB

├── system.dtb # 设备树(可选独立)

├── system.bit.bin # FPGA Bitstream

└── boot.scr # U-Boot 升级脚本5.2 升级流程说明

- 插入 U 盘并上电

- U-Boot 或 Linux 自动挂载 U 盘

- 执行

boot.scr或升级脚本 - 按脚本顺序更新 bitstream / image.ub / RootFS

- 升级完成后重启系统

QSPI 中内容在升级过程中保持不变。

6. 升级与维护机制

6.1 QSPI 固件升级

- 通过 Linux MTD 工具烧写 BOOT.bin

- 升级过程中不影响 RootFS

6.2 Linux 系统升级

- SD 卡离线升级

- eMMC 在线升级(文件系统级)

6.3 回退策略

- 保留 SD 启动作为应急手段

- 启动介质切换不依赖重新烧写 QSPI

7. 可靠性与工程约束

- QSPI 分区地址不可变

- 不依赖 Petalinux 自动分区

- 启动失败可快速定位阶段

8. 典型应用场景

- 研发阶段:SD 启动 + QSPI 固定

- 量产阶段:eMMC 启动

- 现场维护:SD 应急恢复

9. 版本信息

- 方案名称:ZBoot-MP

- 当前版本:V1.0

- 维护状态:工程稳定版

- 维护邮箱:1174316744@qcom

说明 :

本规格说明书用于工程实现与方案交付,不作为入门教学文档。