《FPGA经典例程及解读--基于xilinx K325T平台》系列导航

本专栏主要针对与想学习FPGA的同学,从基础的点灯到之后的复杂功能实战例程,从入门到进阶,通过这些例程的学习和了解,希望可以帮助你从一个FPGA小白进阶到FPGA中级阶段,能够处理工作中大多数的FPGA使用场景。

本篇是该系列的第二篇内容

上一篇:FPGA例程(1):LED流水灯实验--vivado工程创建、编译及下载bit-CSDN博客

**下一篇:**关注我,第一时间获取更新!!

1 引言

上一篇介绍了LED流水灯的程序,但是我们将bit文件下载入板子中,一旦掉电bit文件就丢失了,我们就需要重新下载,那本篇就来说一说,如何将上一篇流水灯的程序固化到我们板子的Flash里面,包括MCS文件的生成,Flash配置和如何固化。

2 MCS文件制作

**第一步:**打开上一篇流水灯的程序,确认bit文件已经生成

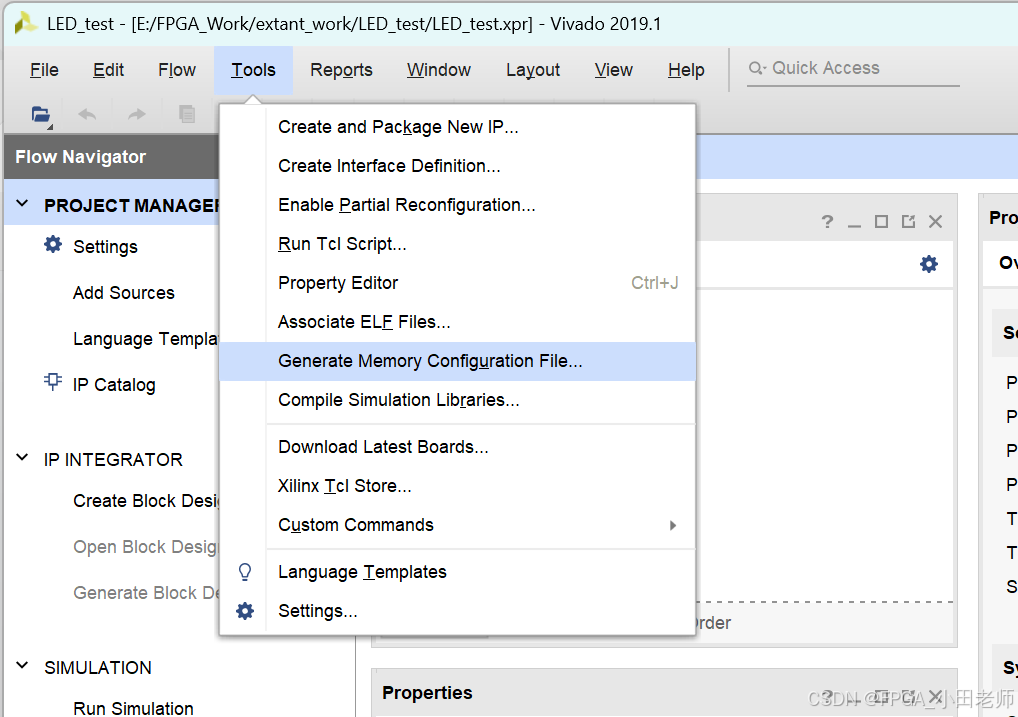

**第二步:**点击Tools--->Generate Memory Configuration File... 就会打开下面的界面

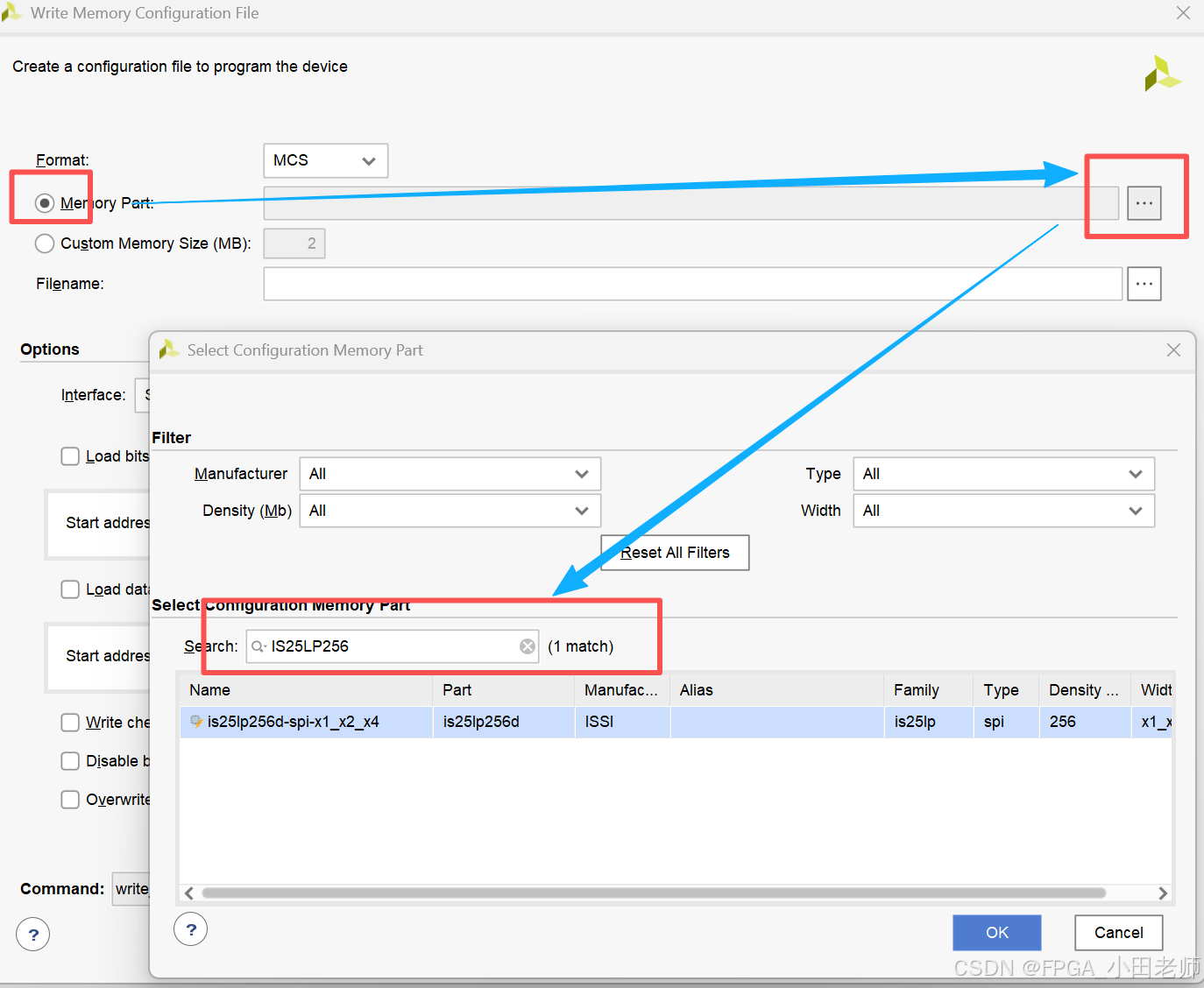

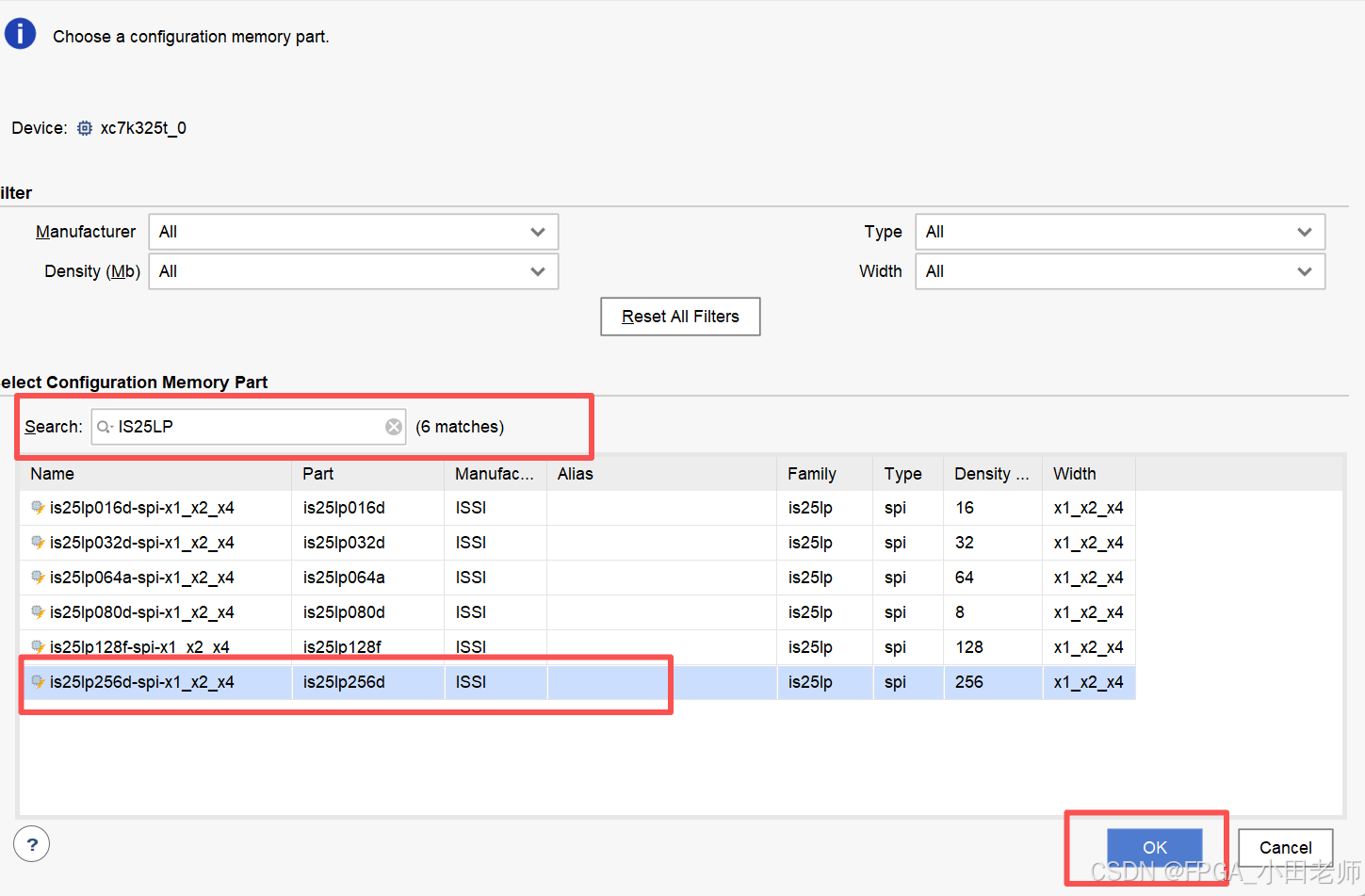

**第三步:**选择Flash型号,查看硬件原理图可知,我们本次使用的Flash型号是IS25LP256

选择Memory Part---点击后面的三个点,输入Flash型号进行选择,点击OK

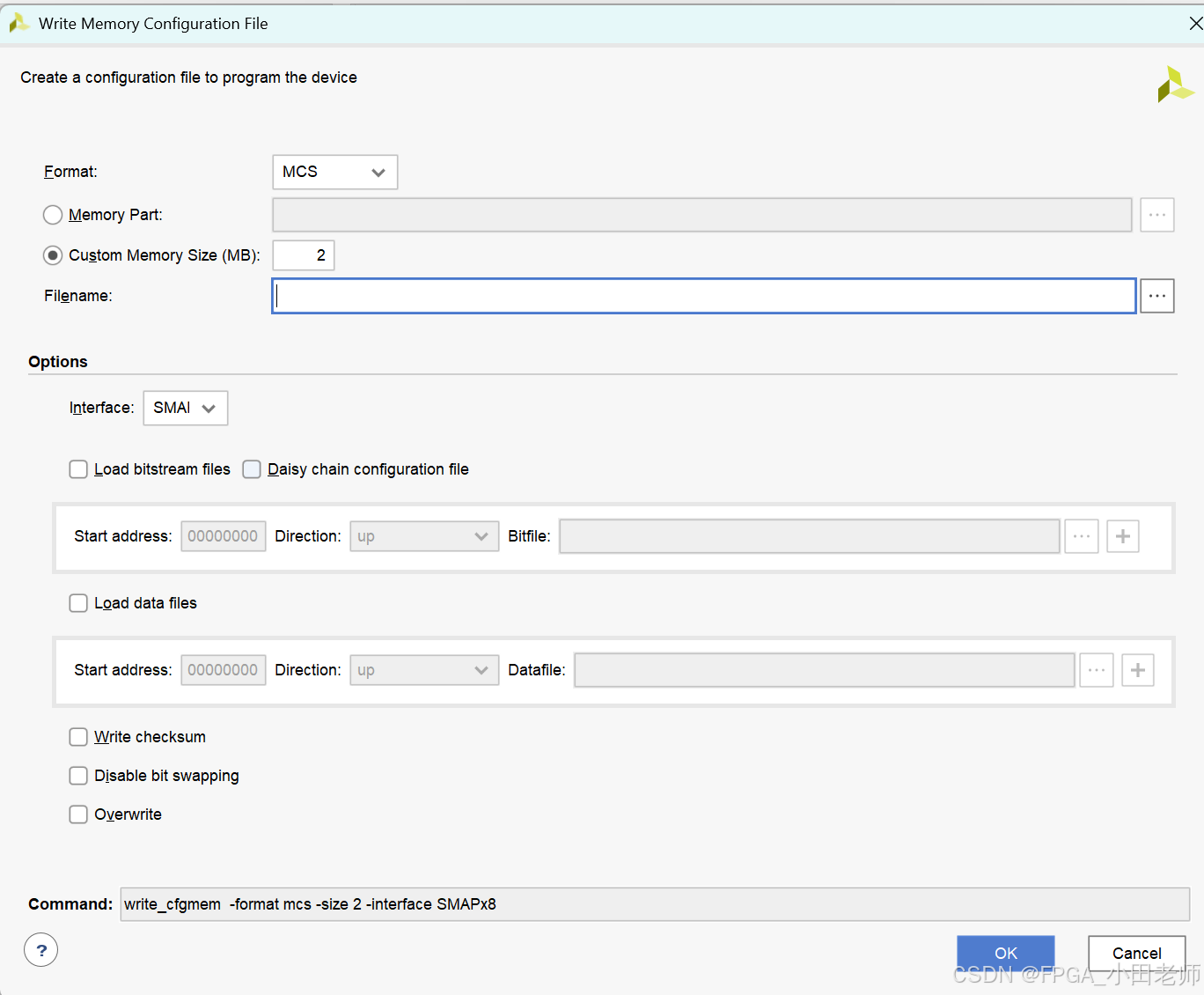

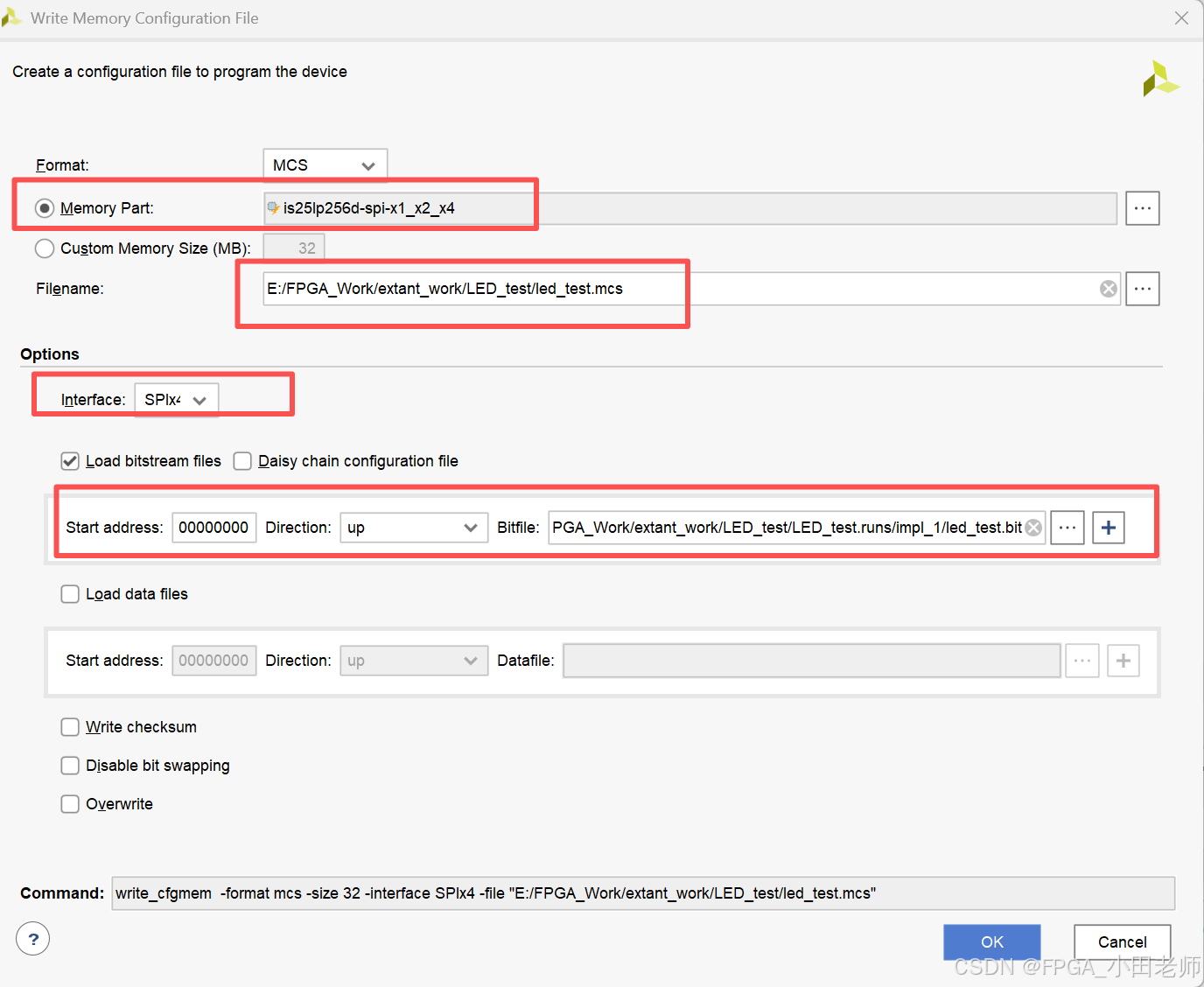

**第四步:**新建MCS文件

点击Filename后面的三个点---->选择你想要放置MCS文件的路径--->命名一个led_test.mcs的文件--->点击save

**第五步:**导入bit文件

选择接口为SPIX4(在上一篇生成bit的时候我们进行了SPI X4的约束,如果没有这个约束,默认就是SPI X1)

勾选load bitstream files

点击Bitfile后面的三个点--->找到我们上一篇生成的bit文件--->选择OK

这样我们的MCS文件生成的界面就配置好了,点击OK即可生成一个led_test.mcs的文件,这个就是我们将来固化到Flash中的文件。

3 程序烧写Flash

**第一步:**连接仿真器,给板子上电

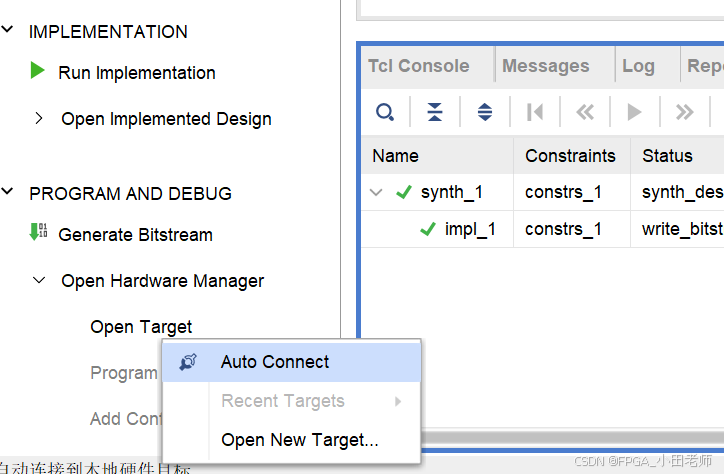

**第二步:**Open Hardware Manager---->Open Target---->Auto Connect

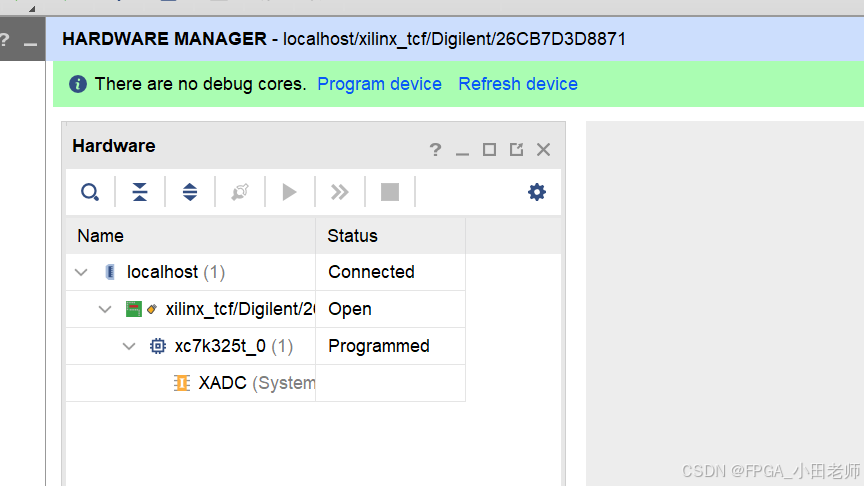

连接成功的界面如下

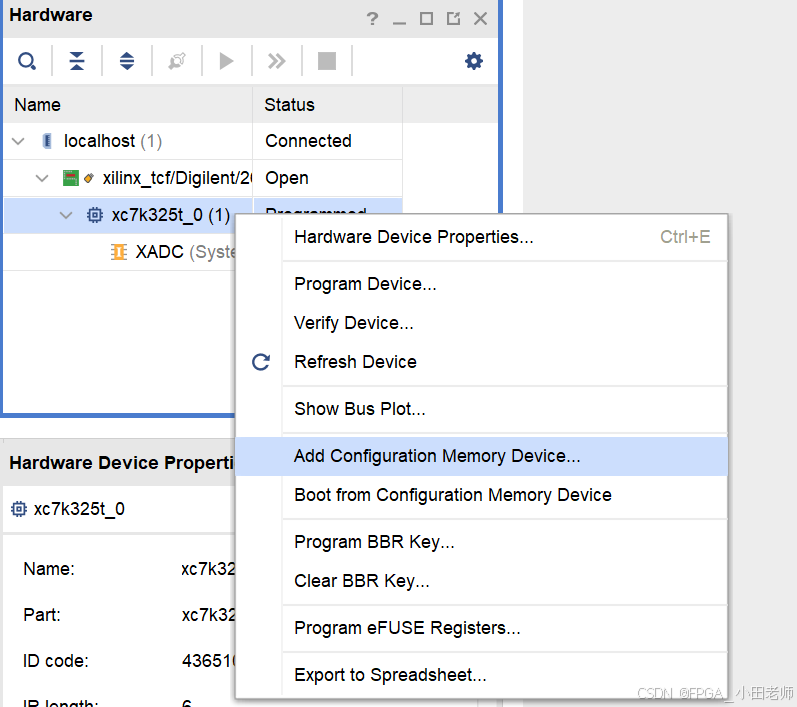

**第三步:**选择器件(xc7k325t)----> Add Configuration Memory Device

**第四步:**选择Flash型号(IS25LP256),点击OK

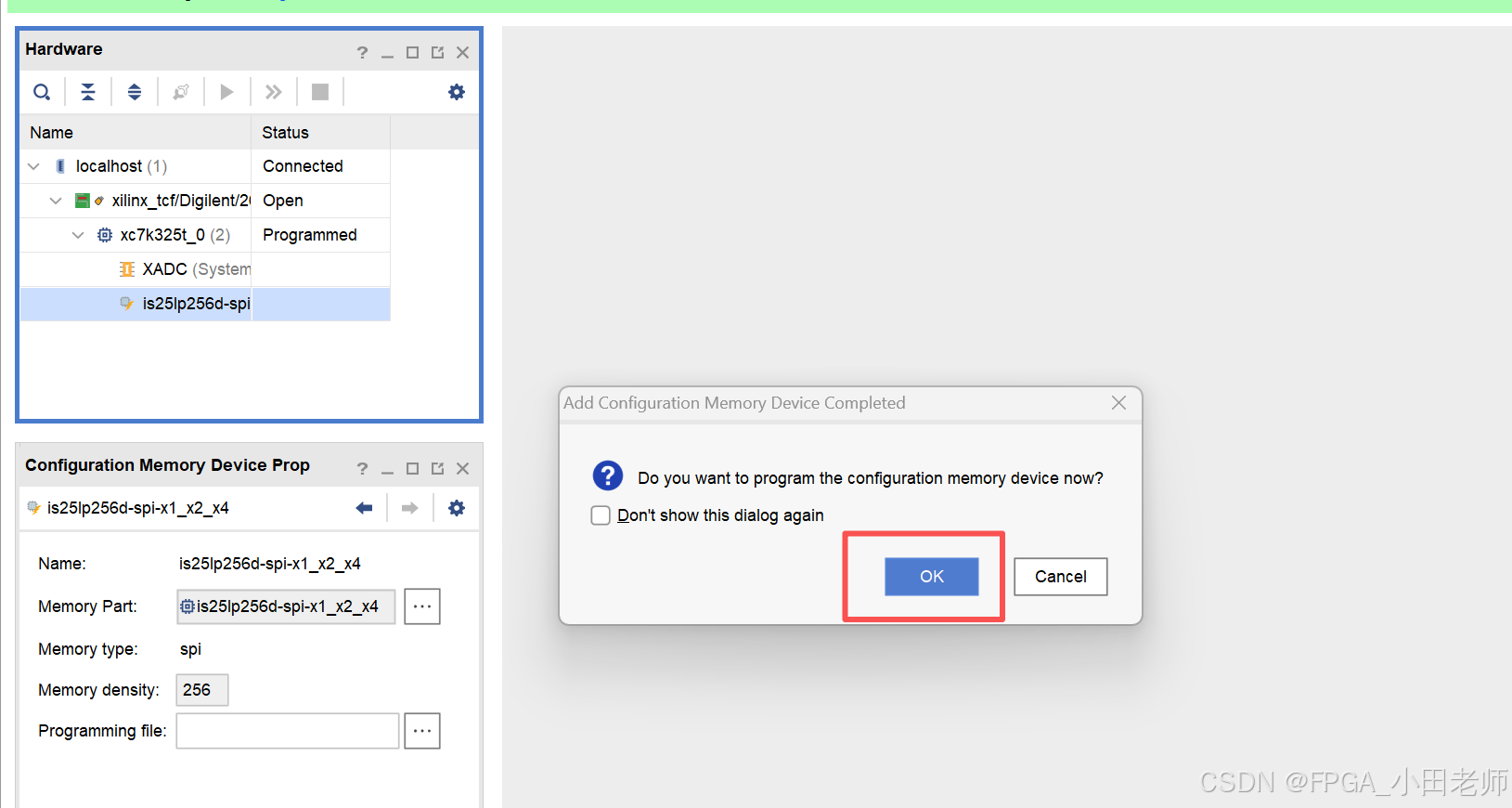

跳出如下界面,询问是否需要现在下载程序,我们点击OK即可。

**第五步:**烧写文件MCS选择

点击Configuration file后面的三个点--->选择刚才生成的MCS文件---OK

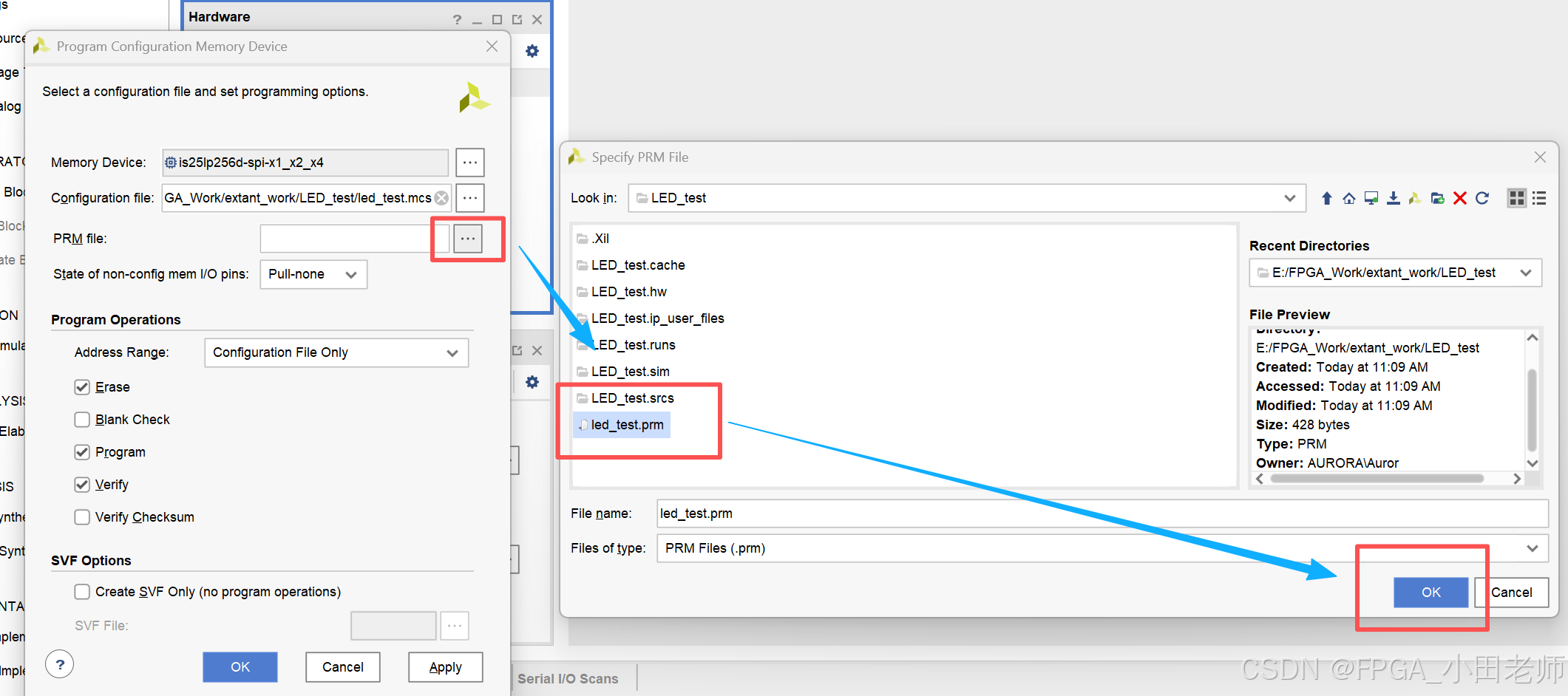

**第六步:**PRM文件选择

点击PRM file后面的三个点---->选择PRM文件(一般都是在MCS文件的同级目录下,随MCS文件一起生成的)---->OK

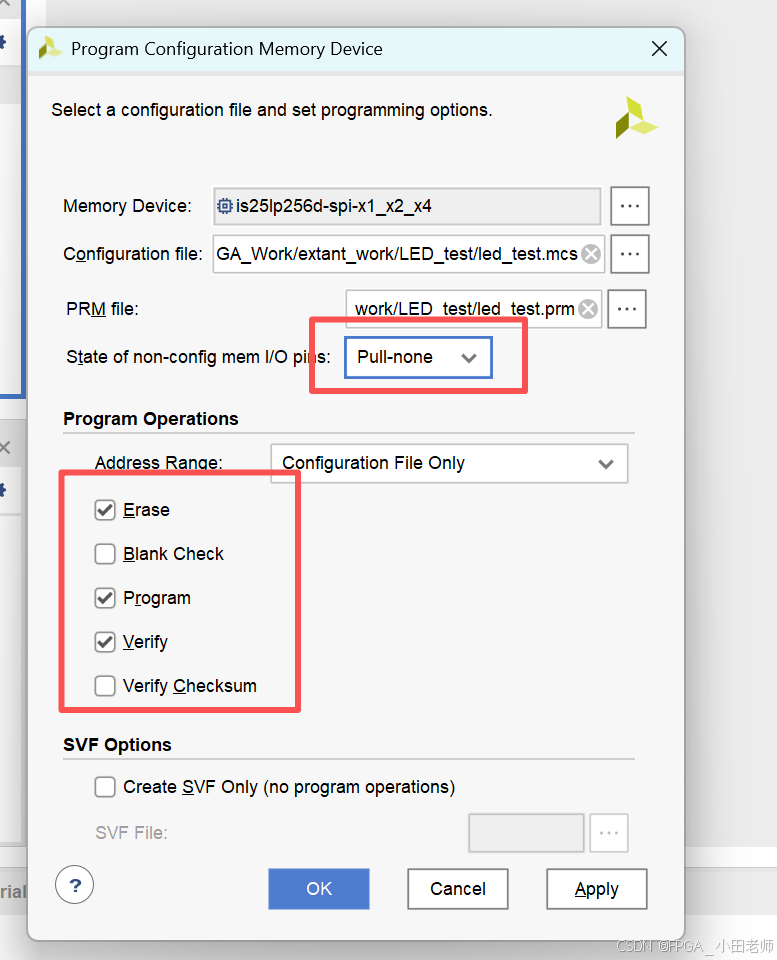

**第七步:**之后的选择还有以下两个

第一个是选择没有使用的端口的状态,默认是pull-none,即悬空态,你可以选择上拉或者下拉均可

第二就是下载的一些选项:擦除、烧写等,一般我们都是保持默认,当然有的时候不需要烧写Program,可能只需要擦除原来的程序,那我们这这里就只选择Erase就可以了。

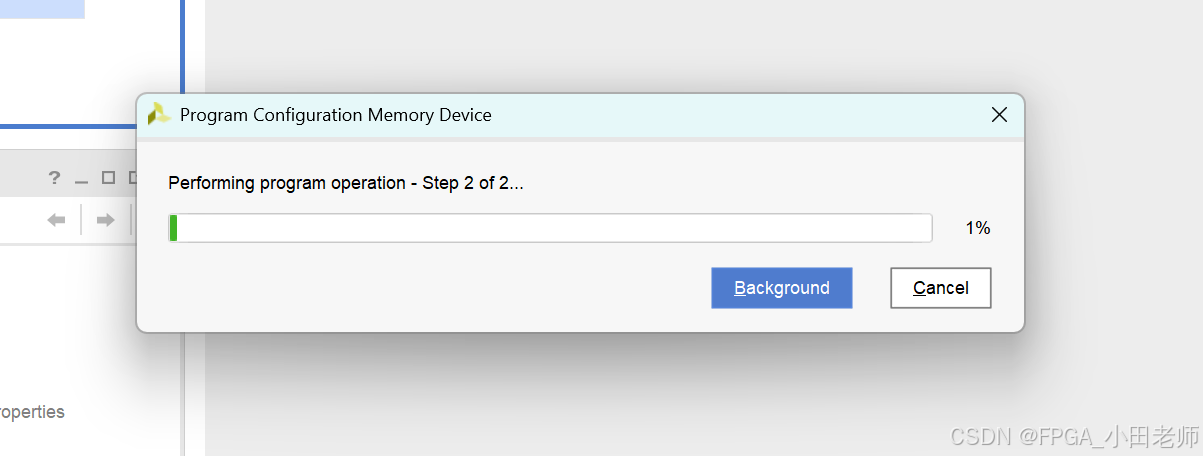

**第八步:**配置好之后,点击OK,程序就开始下载了,一般需要稍微等待一下

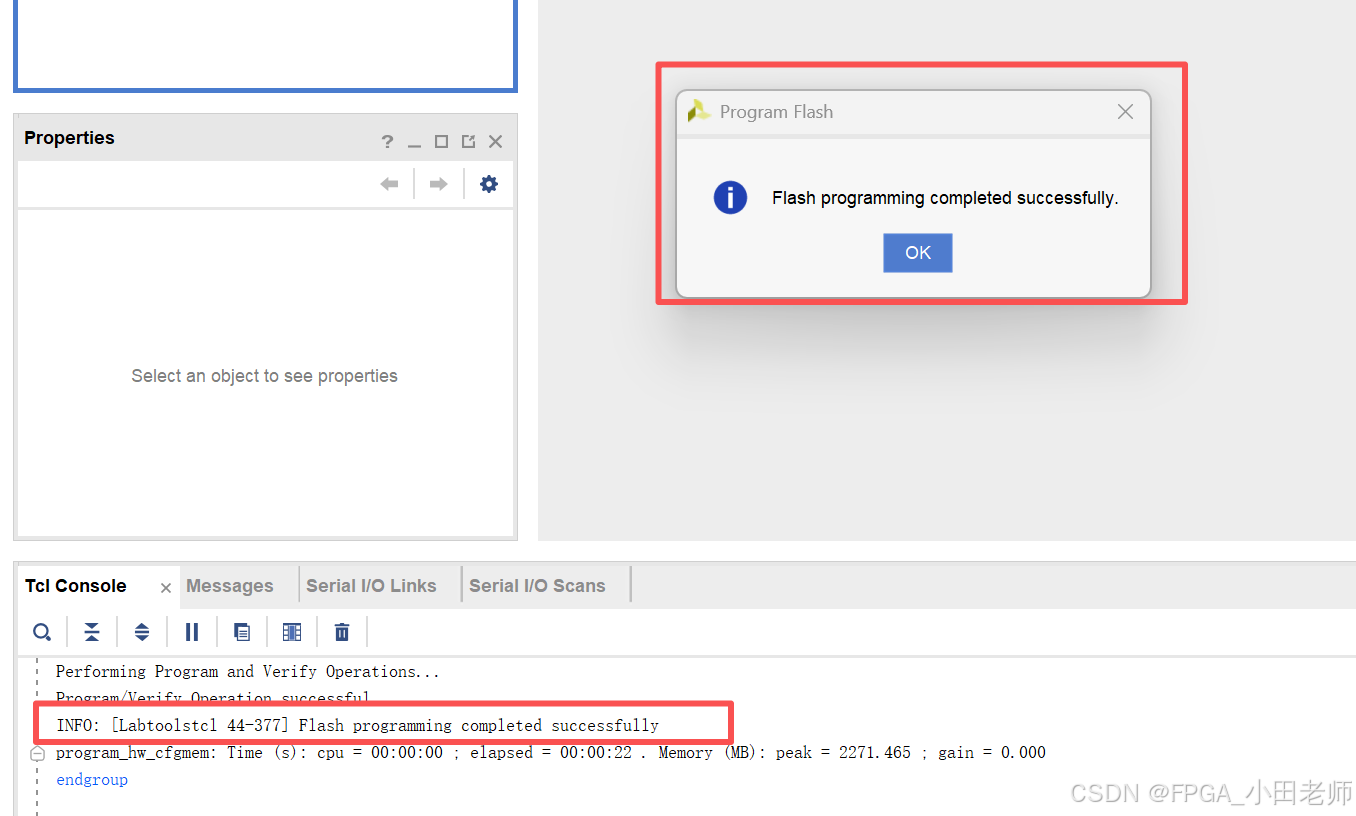

烧写完成之后会显示如下界面

4 烧写结果测试

我们将板子断电

再重新上电

可以看到LED流水灯已经开始闪烁,说明我们的程序已经固化进去了,而且掉电也不会丢失了。

led流水灯视频展示