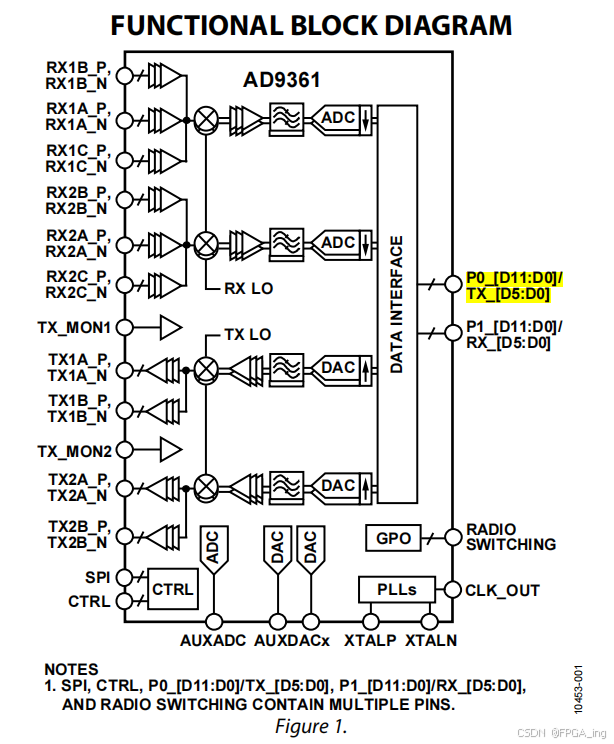

AD9361是一款高度集成的射频(RF)收发器,能够针对各种应用进行配置。这些设备集成了在单个设备中提供所有收发器功能所需的所有RF,混合信号和数字模块。可编程性使该宽带收发器适用于多种通信标准,包括频分双工(FDD)和时分双工(TDD)系统。这种可编程性还允许使用单个12位并行数据端口,两个12位并行数据端口或12位低压差分信号(LVDS)接口将设备连接到各种基带处理器(BBP)。

AD9361接收器LO(本振)工作频率范围为70 MHz至6.0 GHz,发射器LO 工作频率范围为47 MHz至6.0 GHz。每个通道搭载两个高动态范围模数转换器(ADC),先将收到的 I 信号和 Q 信号进行数字化处理,然后将其传过可配置抽取滤波器和128抽头有限脉冲响应(FIR)滤波器,结果以相应的采样率生成12位输出信号。

使用AD9361,首先将其外部一些控制的引脚置位到相应的电平信号,然后对其进行初始化,既寄存器的配置,配置完成后就可以启动收发信号了。

AD9361提供了spi接口用于读写内部配置寄存器,初始化就是通过spi总线进行。

AD9361的输入以及输出的数据以及时钟都是差分信号,对于输入数据需要差分转单端,输出数据需要单端转差分。

AD9361架构:

RX1/2通道分为A,B,C三种输入,A是最优选择,B,C在3G以下频段使用;

TX1/2只能选择A输出;

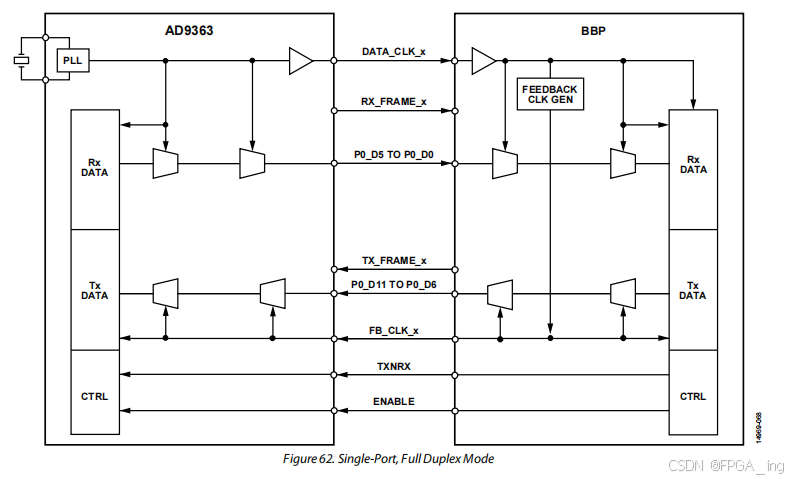

1R1T、FDD模式下需要两个时钟才能完成的接收完一个12位的数据,在RX_FRAME_x为高时,接收到的是 I 路与 Q 路的高6位,为低时接收到的低6位,且DATA_CLK_x的下降沿接收的是 I 路,上升沿接收Q路;

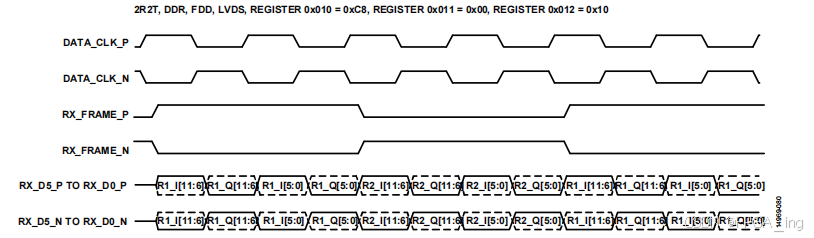

2R2T、FDD模式下需要四个时钟才能完成的接收完一个12位的数据,在RX_FRAME_x为高时,接收

到一个通道的数据,但是先接到的前两个是高6位,后两个是低六位,DATA_CLK_x的下降沿接收的是I路,上升沿接收Q路;

TX的波形与此类似,在发送时,需要将数据按照波形图进行拼接,不然会导致发送错误。

时序图:

1T1R:两个时钟周期输出一路的 I Q 数据;

假如时钟频率为20M(data_clk),其系统采样频率为10M。

因为DDR 双沿采样,即两个时钟出一个采样点,所以最终时钟频率为10M;

采样率是系统时钟的 1/2;

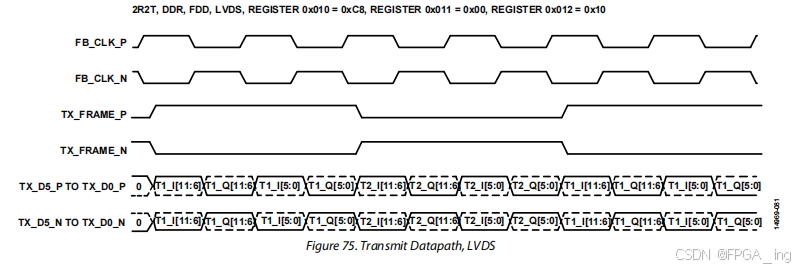

2T2R:4个时钟周期输出 2 路的 I Q 数据;

假如时钟频率为20M(data_clk),其系统采样频率为5M。

对于2T2R,最终时钟频率为20M/4=5M;

采样率是系统时钟的 1/4;

BBP:基带处理单元(FPGA);

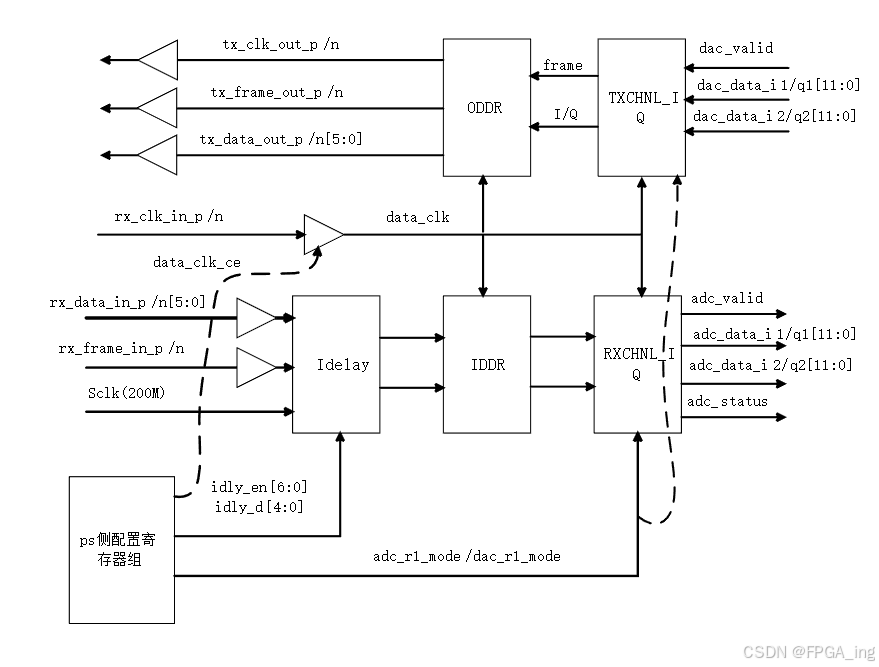

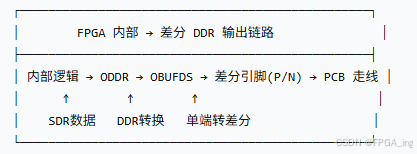

FPGA 接收AD9361数据和给AD9361发送数据接口模块设计思想:

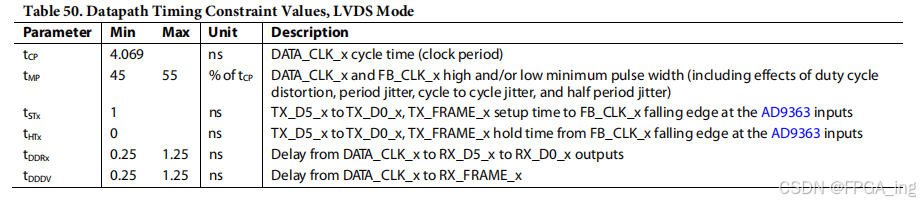

AD9361使用的是LVDS DDR通信模式,FPGA侧首先使用 IDDR 和 ODDR 的原语进行转换成单沿采样数据(RX),单沿输出数据转换成双沿数据(TX)。RX端使用 Idelay 原语进行动态调整接收数据与时钟延迟。TX端使用 ODDR 简单进行180度的相位翻转,因为在AD9361官方配置程序中 tx_fb_clock_delay 设置=7 也就是近似160度相位,这里两个180+160度相位累加就是变成了340度相移。

AD9361接口模块设计框图

AD9361 的数据接口与时钟接口均采用差分设计,数据通道分为正交的 I 路(同相通道)与 Q 路(正交通道),二者构成核心数据传输路径。该芯片的接收(Rx)与发送(Tx)链路各配备 6 对数据接口,单次传输的数据位宽固定为 6 位。

在1R1T(1 收 1 发)、频分双工(FDD)模式下,接收链路的工作机制如下:

接收数据需占用两个完整的时钟周期(DATA_CLK),通过 RX_FRAME_x 信号实现数据位分段控制 ------ 当该信号为高电平时,接收高 6 位数据;为低电平时,接收低 6 位数据,完成 12 位数据的完整采集。时钟同步方面,DATA_CLK_x 时钟的下降沿专门用于采集 I 路数据,上升沿则采集 Q 路数据;为确保采集到数据最稳定的中间时刻,系统还需要针对数据信号设计专门的延时处理机制。

发送链路的工作逻辑与接收链路类似,在 1R1T、FDD 模式下,需生成对应的 TX_FRAME_x 控制信号:发送高 6 位数据时,TX_FRAME_x 信号为高电平;发送低 6 位数据时,TX_FRAME_x 信号为低电平,以此实现发送数据的分段传输。

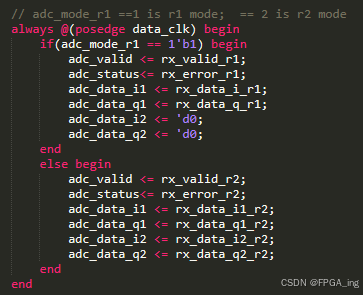

需要注意的是,上述 1R1T 模式与 2R2T(2 收 2 发)模式的切换,由接口对接模块的 adc_r1_mode 与 dac_r1_mode 信号联合控制:当两个信号均为 0 时,模块工作在 2R2T 模式;当两个信号均为 1 时,模块切换至 1R1T 模式。该控制仅针对 AD9361 的接口对接模块,若需直接控制 AD9361 芯片本身的工作模式,还需通过 SPI 接口对芯片内部的配置寄存器进行相应配置。

ADC 侧

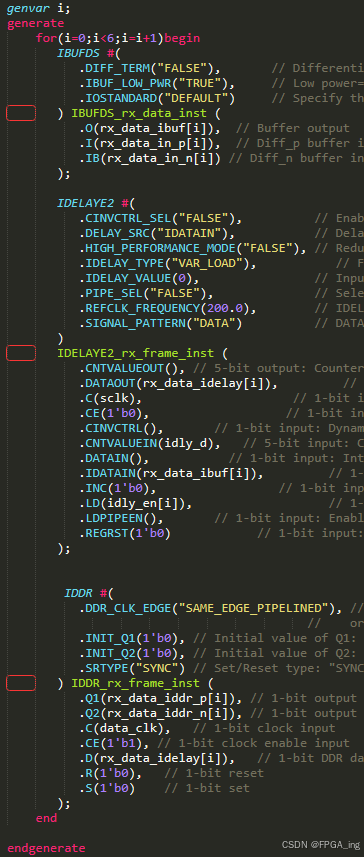

对于 rx_clk_in_p/n:

因为输入的数据信号为差分,所以需要进行差分转单端,再经过全局时钟网络缓冲输出;

需要使用到的原语:IBUFDS、BUFGCE(1=enable); FPGA芯片型号不同原语会不同;

BUFGCE 是 Xilinx FPGA 中一种带有时钟使能(Clock Enable)信号的全局时钟缓冲器。它的核心作用是在不使用时安全地关闭时钟信号,以达到动态降低功耗和避免时钟域混乱的目的。

对于 rx_frame_in_p/n:

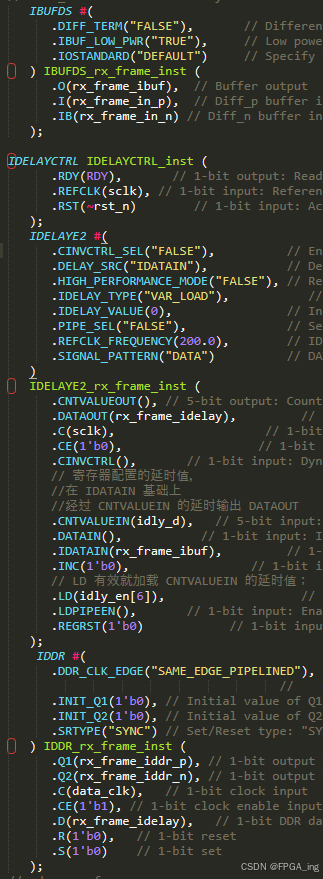

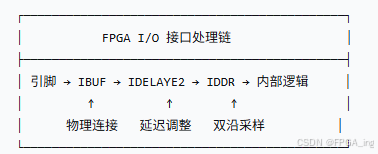

输入信号经过差分转单端后,进行 IDELAY,再给到 IDDR,需要搭配 IDELAYCTRL 才能完成;

IDELAYE2 是一个可编程的输入延迟单元,主要用于对输入信号进行精确的延迟调整(以 Tap 为单位),常用于解决数据与时钟之间的时序对齐问题。

延迟精度:每个 Tap 的延迟约为 78ps(7系列)或更小(后续系列)

延迟范围:最多 31 个 Tap(约 2.4ns)

工作模式:

FIXED:固定延迟模式(配置时设定)

VARIABLE:可变延迟模式(运行时动态调整)

LOADABLE:可加载延迟模式(可重新加载延迟值)

源同步接口对齐:

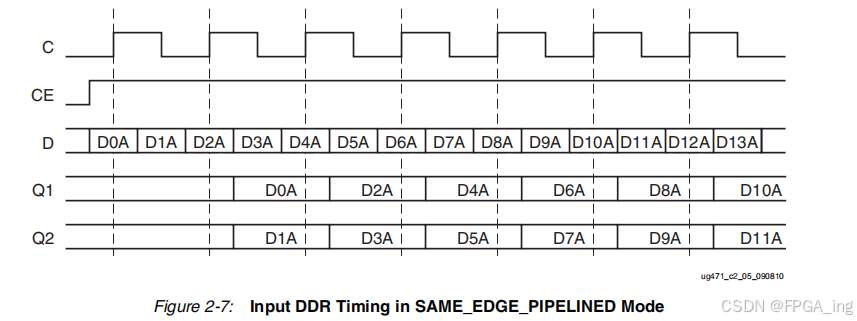

IDDR 是一个专用的输入双数据速率寄存器,用于将外部 DDR(双数据速率)信号转换为 FPGA 内部可处理的 SDR(单数据速率)信号。

DDR 转 SDR:在时钟的上升沿和下降沿都传输数据的外部接口中,IDDR 在时钟上升沿捕获两个数据,并输出两个 SDR 数据流。

时钟域对齐:确保上升沿和下降沿的数据在同一个时钟域中被处理。

IBUF:接收来自引脚的电平信号,转换为 FPGA 内部电平

IDELAYE2:调整数据信号的延迟,使其与采样时钟对齐

IDDR:将 DDR 数据分解为两个 SDR 数据流(Q1=上升沿数据,Q2=下降沿数据)

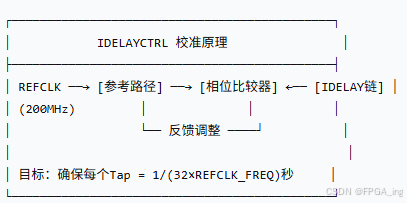

IDELAYCTRL 是 Xilinx FPGA 中一个关键的延迟校准控制器,提供一个稳定的参考时钟(通常 200MHz 或 300MHz),它为 IDELAYE2 和 ODELAYE2 提供精确的延迟校准,确保延迟抽头(Tap)的延迟值在各种工艺、电压和温度(PVT)条件下保持一致。

对于 7 系列 FPGA:

每个 Tap 延迟 = 1 / (32 × REFCLK_FREQ)

如果 REFCLK = 200 MHz:

每个 Tap 延迟 = 1 / (32 × 200,000,000) = 156.25 ps

如果 REFCLK = 300 MHz:

每个 Tap 延迟 = 1 / (32 × 300,000,000) = 104.17 ps

对于 rx_data_in_p/n:

数据为6比特,需要重复6次转换,即可完成;

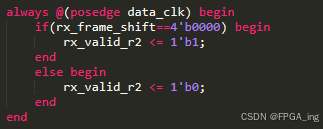

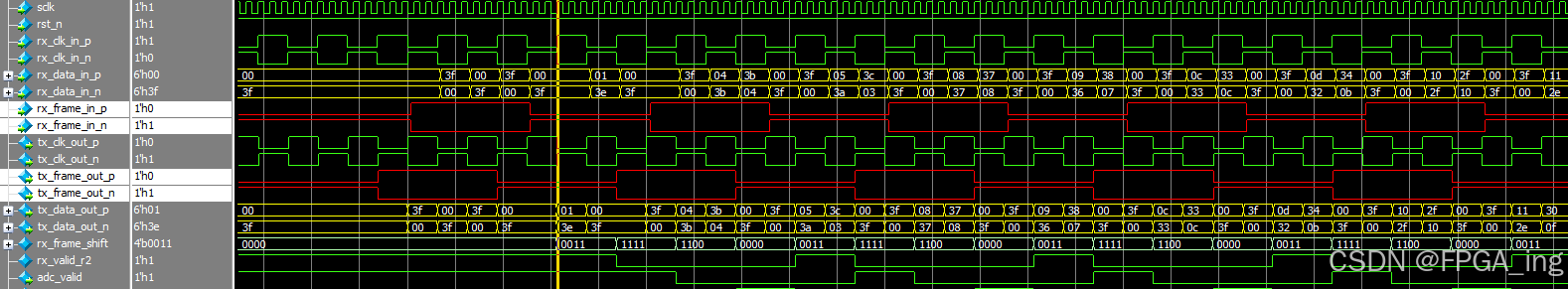

单通道 RX 数据解析时序:

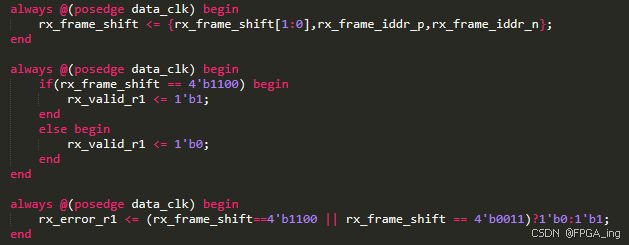

因为是 IDDR 采样,在 Data_clk 第一个时钟周期采集到的Rx_frame 为11,下一个时钟周期采集到值为00;data_clk上升沿采集的为 p,下降沿采集的为n;

对于 rx_data 信号与Rx_frame 类似,参照下图时序,取对应的 Q 或者 I 进行拼接即可;

构建一个移位寄存器,24位,包含了1个完整的12位Q 和1个完整的12位 I 的数据;

在一个完整的 rx_frame 周期下,取出完整的12位 Q 和 I 数据;

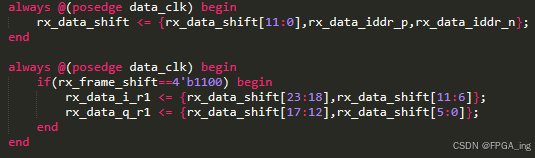

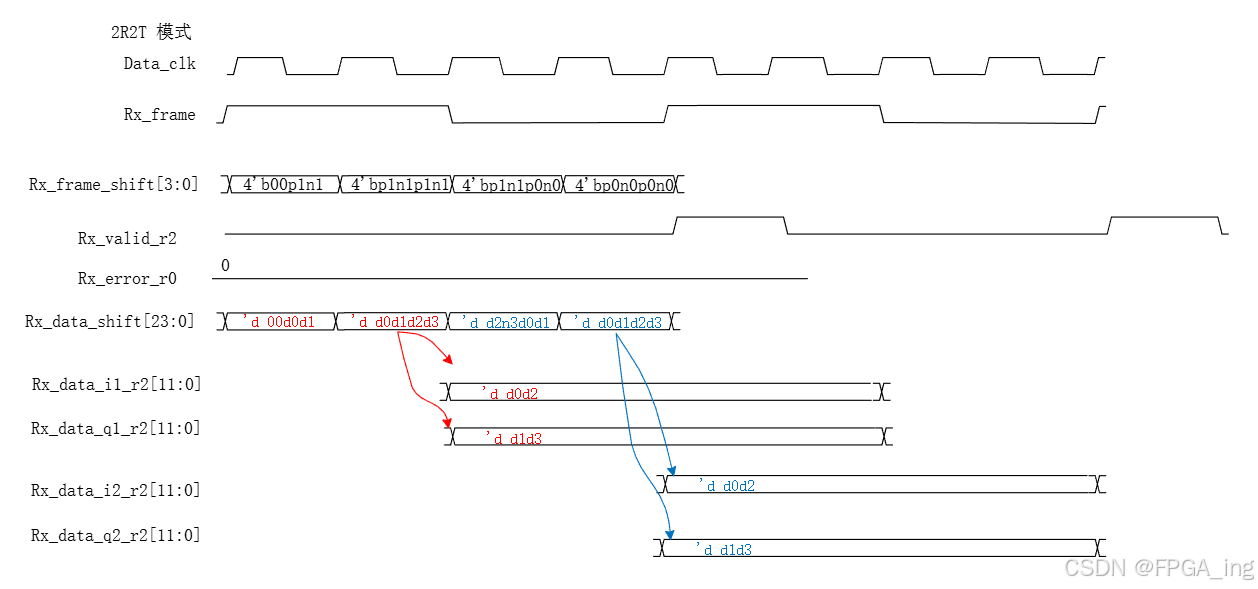

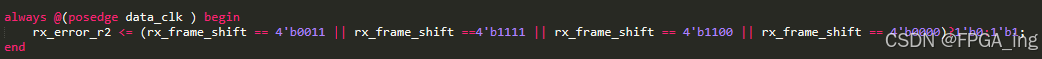

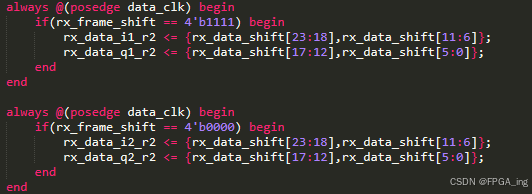

双通道 RX 数据解析时序:

对于2R2T,每隔 4个时钟周期(DATA_CLK)输出两个采样点(I1,Q1, I2,Q2);

数据会在每4拍的 Data_clk(上升沿和下降沿都会算1拍),进行一次输出;

移位寄存器位宽为 24位,每4拍后,得到一个 I 和 Q 的采样值,各占12位;

数据的取值,参考下图时序:

依据寄存器配置参数,选择单通道,或者双通道;

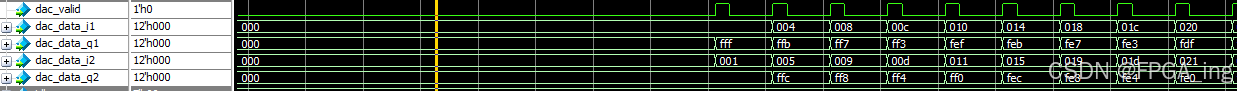

DAC 侧

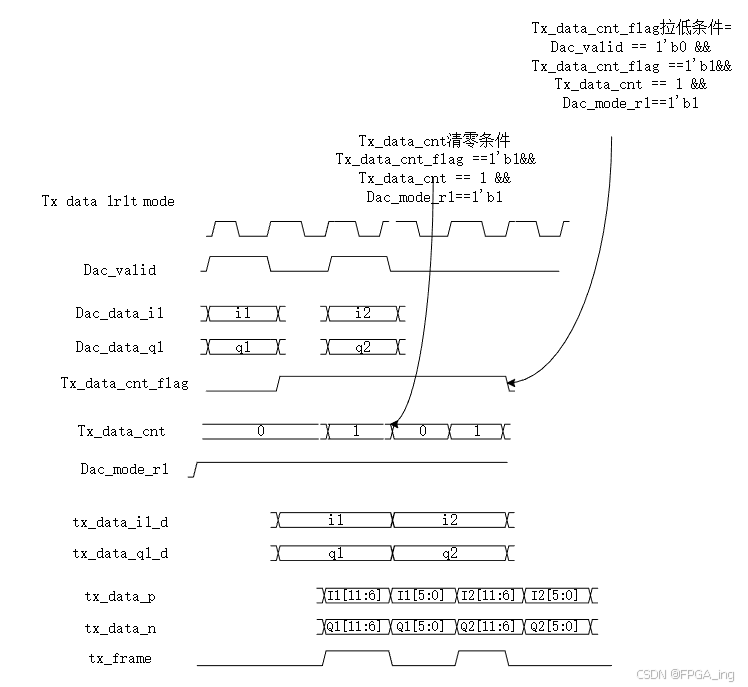

对于1T1R,每 2 个时钟周期SCLK 输入一个数据dac_data,包含12位的 I1 和12位的 Q1,

对其进行拆分,按高6位对应tx_frame高电平和低6位对应tx_frame低电平进行输出;

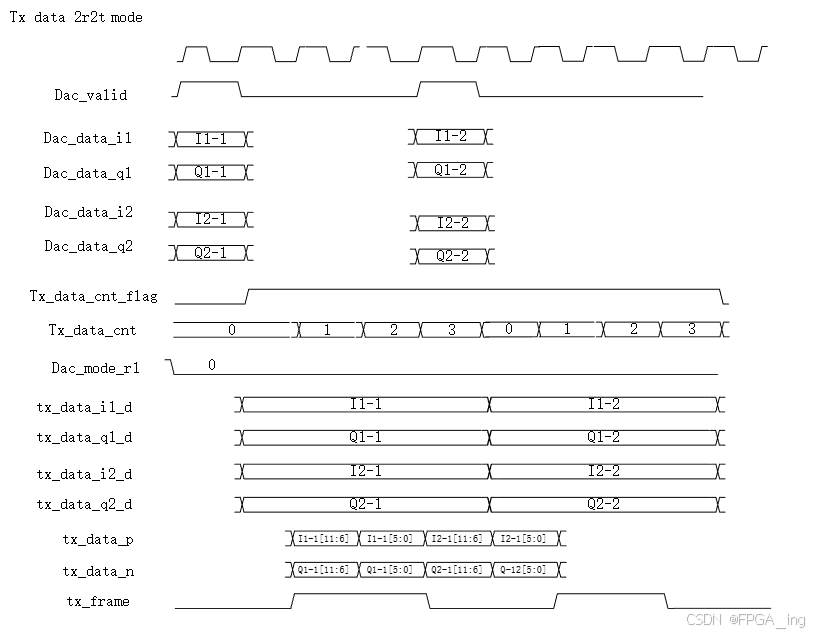

对于2T2R,每 4 个时钟周期SCLK 输入一个数据dac_data,

包含12位的 I1,I2 和12位的 Q1, Q2,

在tx_frame高电平期间分别输出 I1 和 Q1 的高6位,再是低6位;

之后在 tx_frame低电平期间分别输出 I2 和 Q2 的高6位,再是低6位;

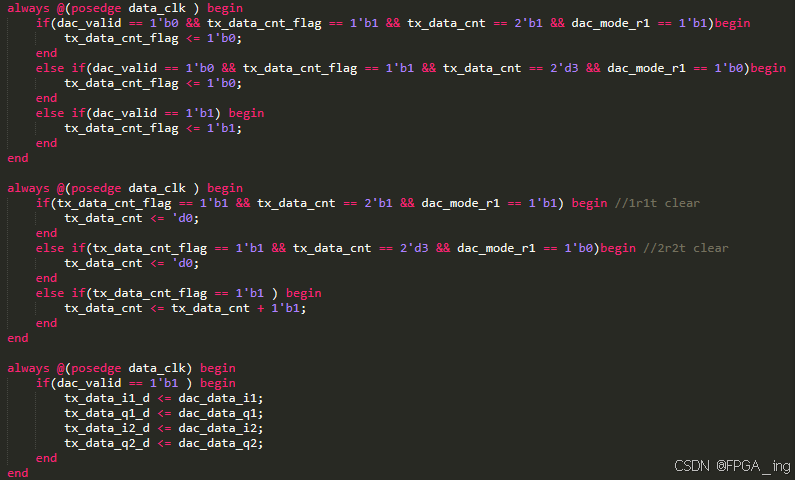

实现逻辑:

对于1T1R,每2拍输出一个数据,计数器0~1;

对于2T2R,每4拍输出一个数据,计数器0~3;

根据 1T1R,2T2R的模式选择,和计数器(兼容1T1R,2T2R)的值进行判断,

对数据tx_data 和 tx_frame (1T1R = 10,2T2R=1100)进行赋值:

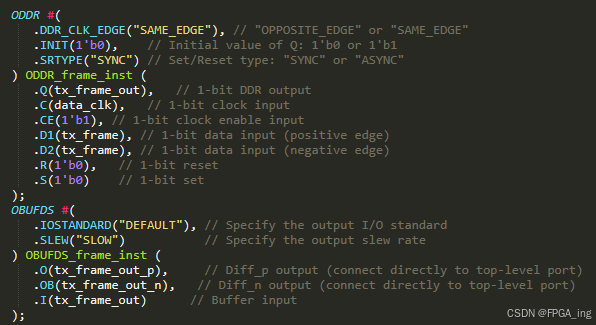

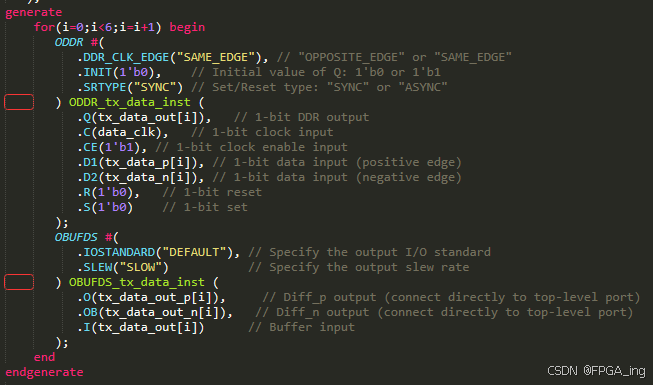

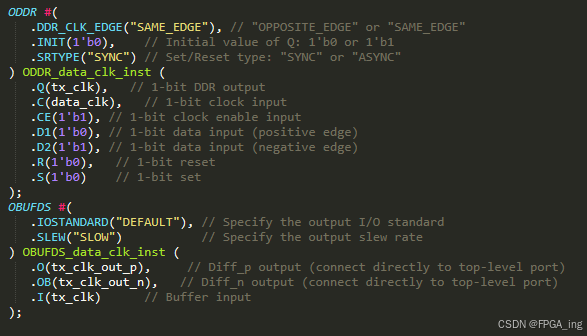

得到的数据和 tx_frame 以及 data_clk 都需要经过ODDR 单沿转双沿,再经过一个OBUFDS 输出出去;

数据为多比特,需要利用for循环,进行单比特发送

ODDR 是一个专用的输出双数据速率寄存器,用于将 FPGA 内部的两个单数据速率(SDR)数据流合并为一个双数据速率(DDR)信号通过单个引脚输出。

SDR 转 DDR:将内部两个单时钟沿的数据合并,在时钟的上升沿和下降沿都输出数据,使数据吞吐量翻倍。

OBUFDS 是一个差分输出缓冲器,用于将内部单端信号转换为差分信号,通过一对差分引脚(P 和 N)输出。

单端转差分:将 FPGA 内部单端信号转换为标准差分信号。

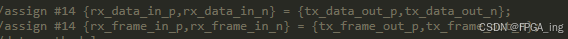

仿真测试:

回环测试,tx 给到 rx;

数据延时不能使用 assign # ;

如果使用此种方法,延时的时间里,数据发生了变化,是不会被传递的;

延时时刻数据保持,延时结束后,数据才会更新,所以在延时的时间段内数据是不会变化的,从而会导致数据丢失;

使用assign 进行数据延时,会导致数据丢失;

因为 assign 语句是不能用于模拟数据的路径延时;

IDELAYE2: