鉴于随着调试FPGA的版本越来越多,版本管理对于开发者是个头大的问题。好在xilinx官方给出了解决方案。

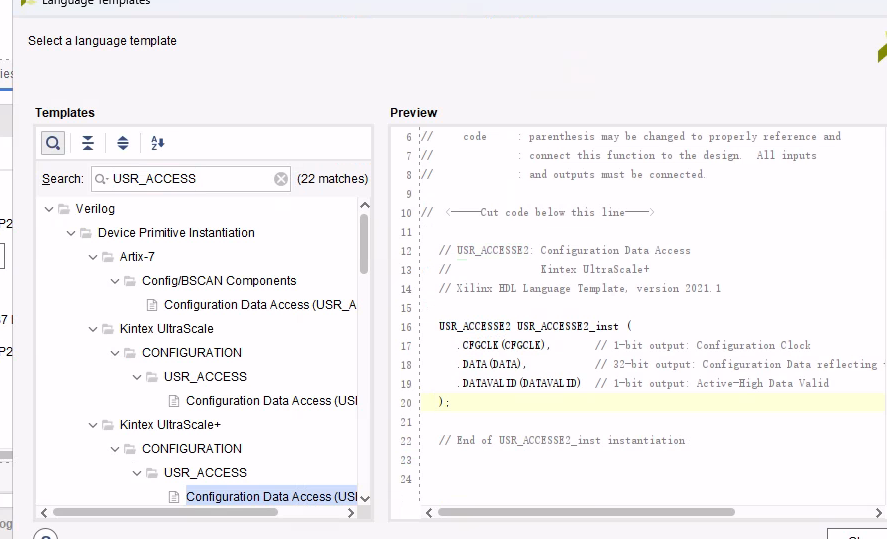

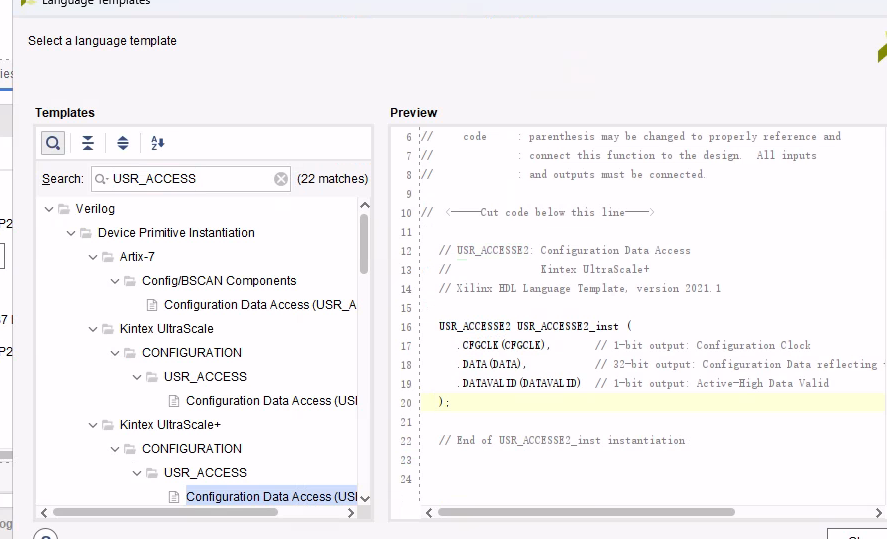

1.搜索原语<USR_ACCESS>,将原语例化到模块当中,可以通过上位机读走。

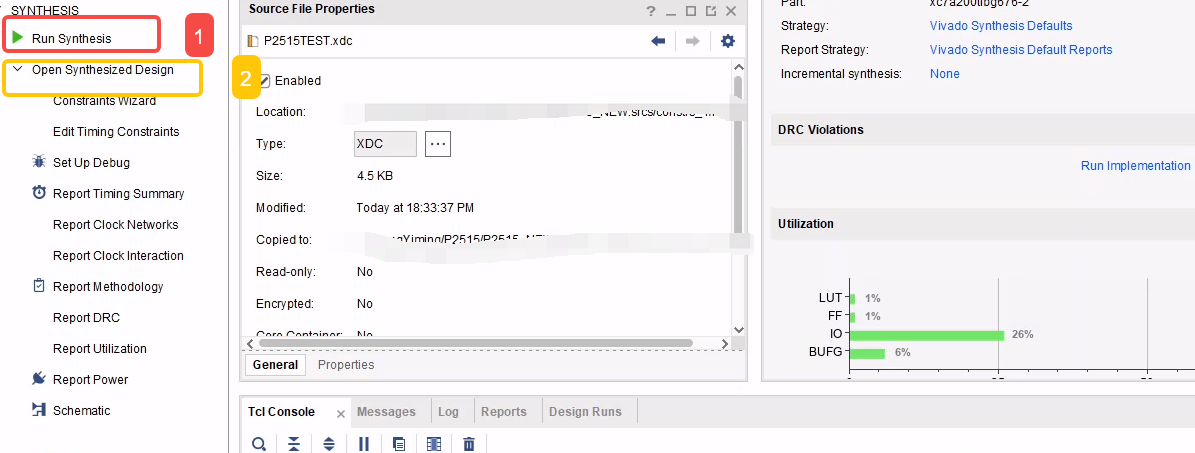

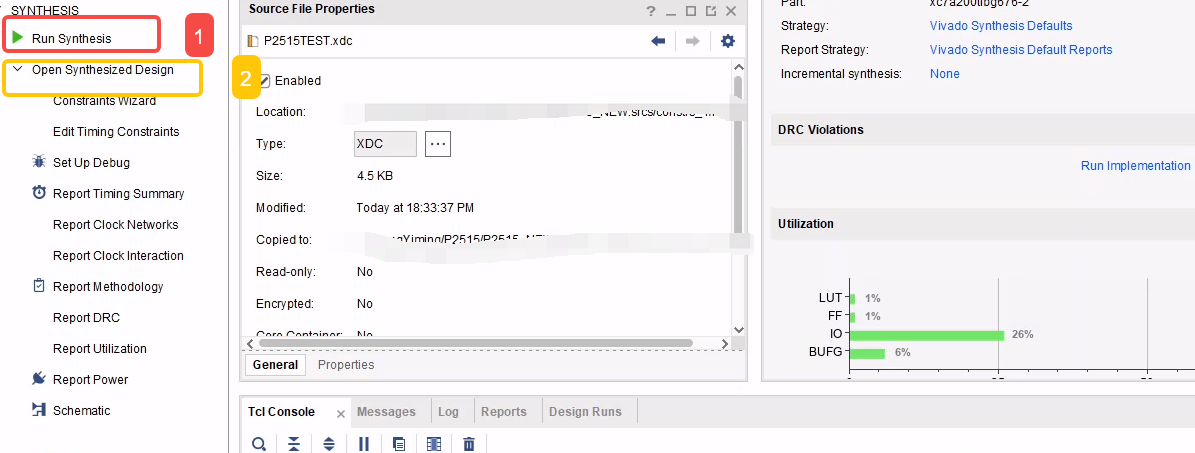

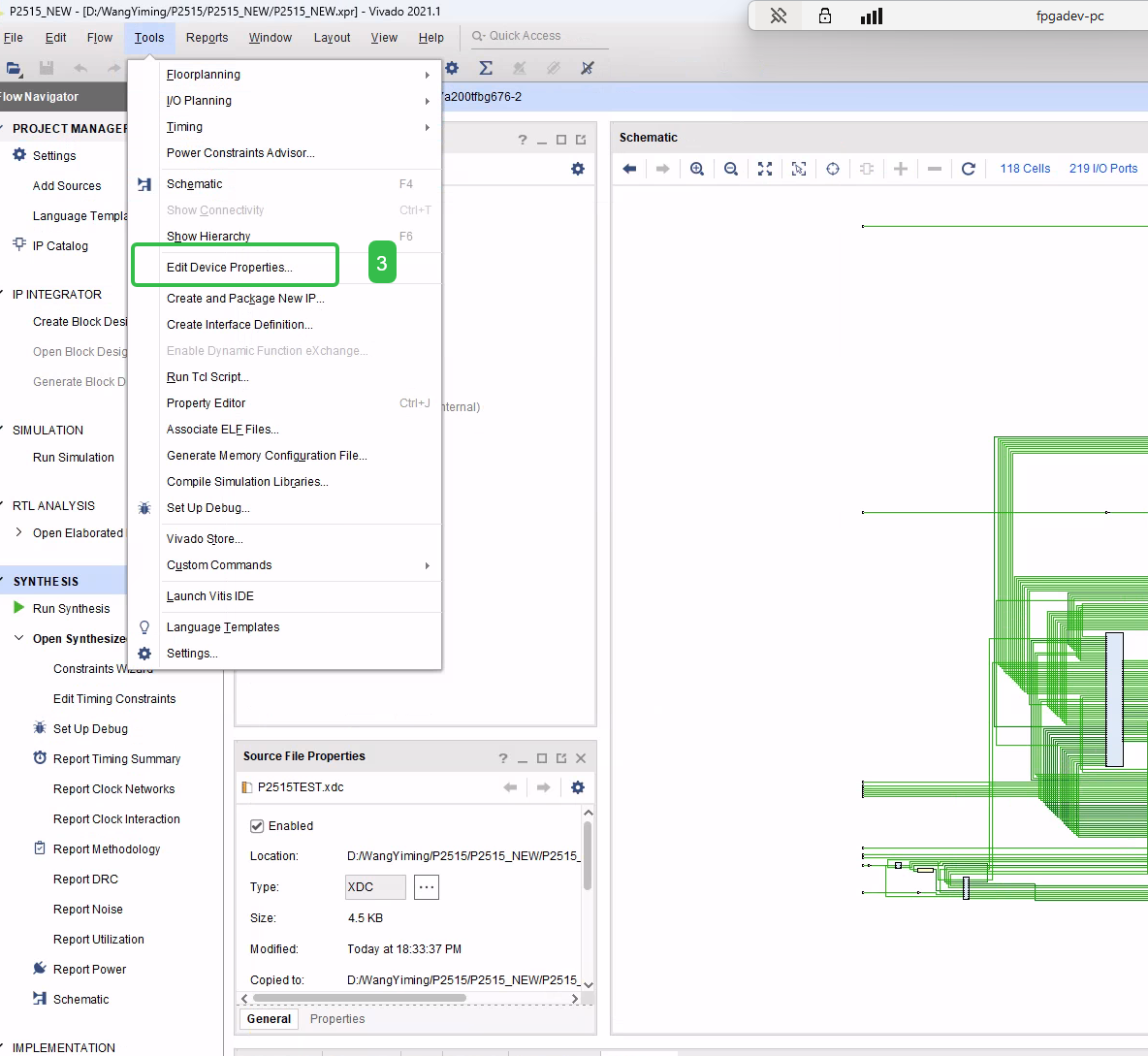

2.综合后打开综合,如下图:

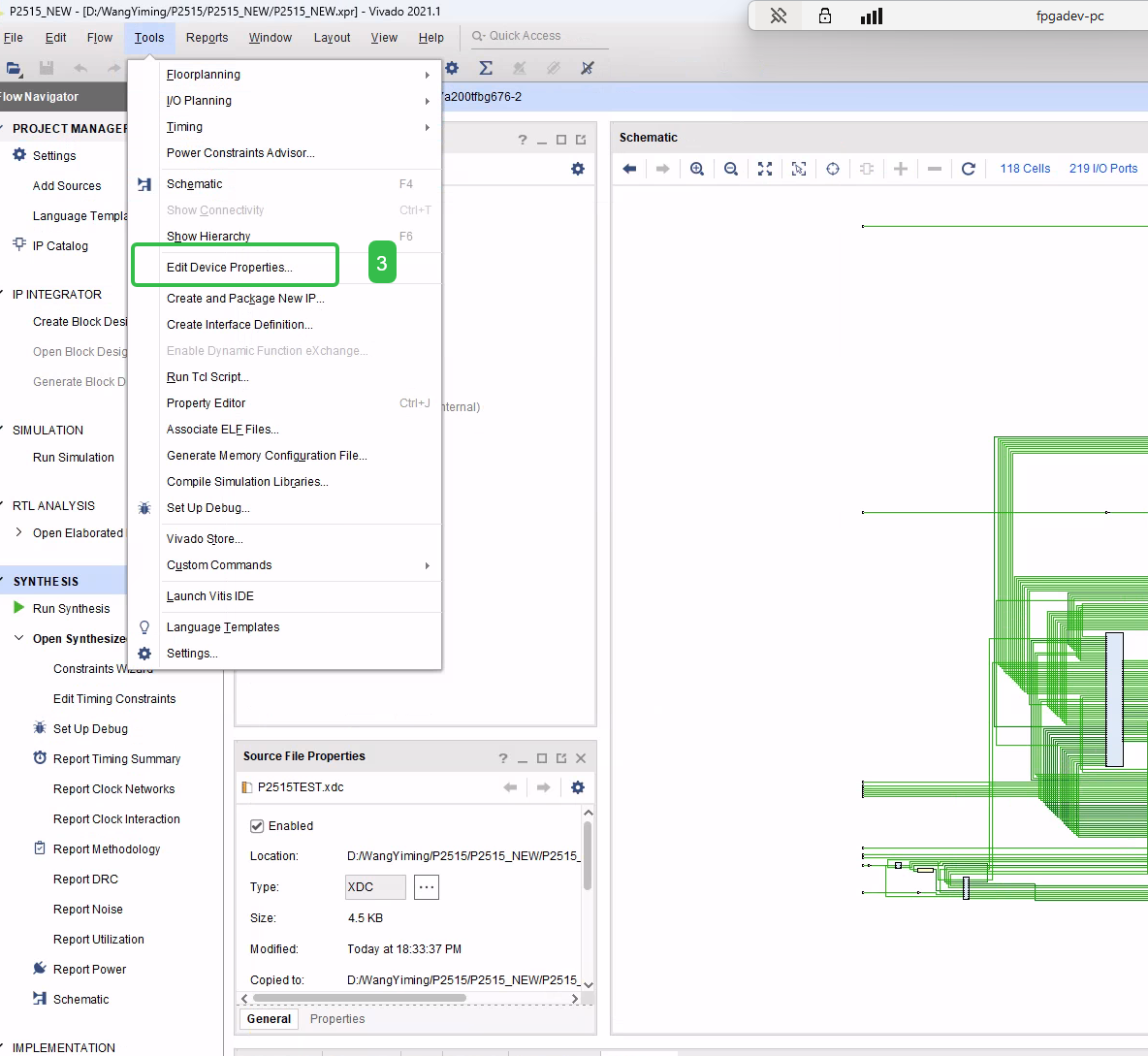

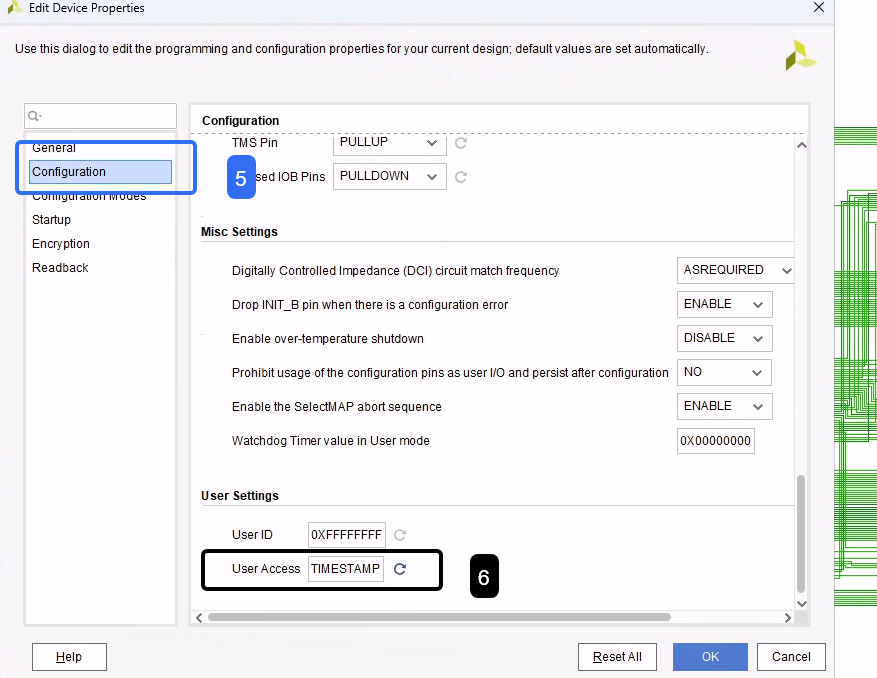

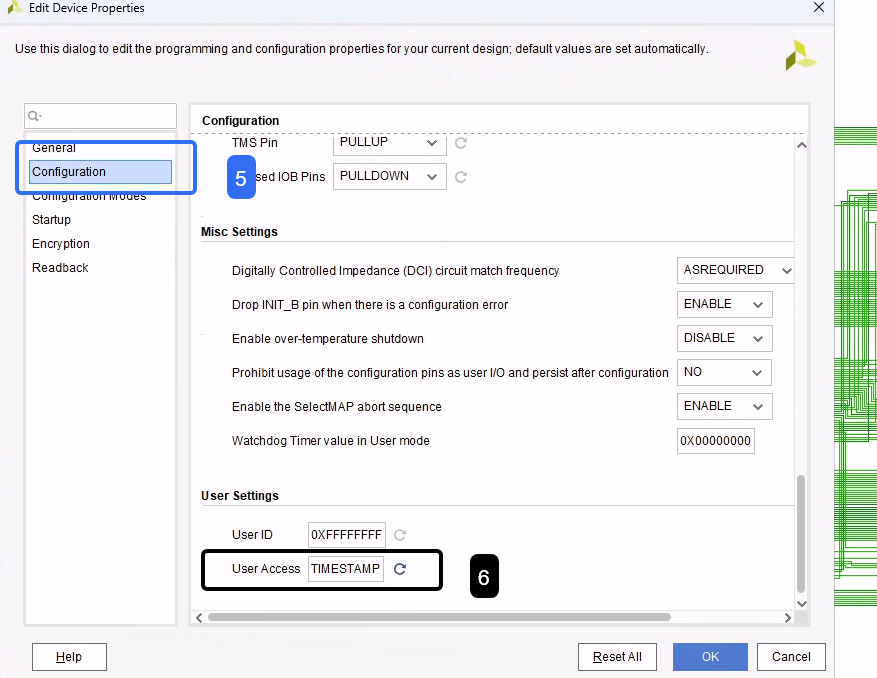

3.点击Edit Device Properties如下图:

4.找到User ACCESS 里面填入<TIMESTAMP>,并保存。

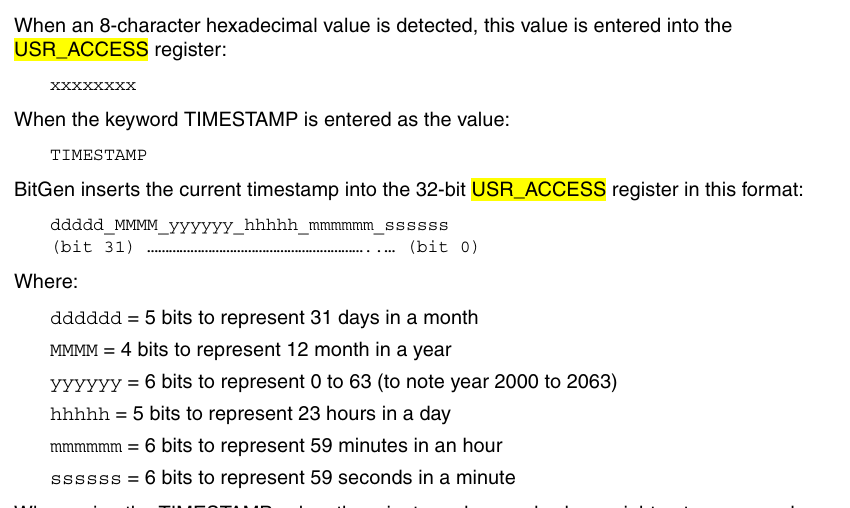

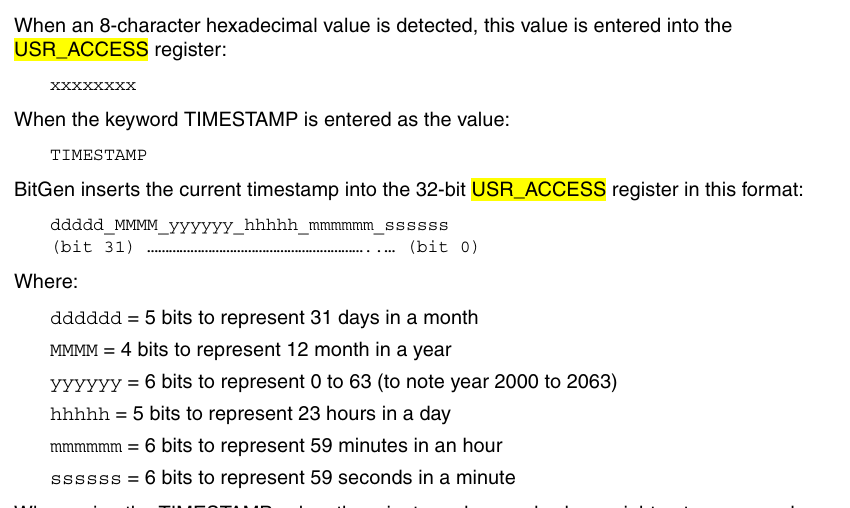

5.后续31bit的数据分别如下图:,逻辑可以根据其值的含义进行解析。从而完成版本管理。

鉴于随着调试FPGA的版本越来越多,版本管理对于开发者是个头大的问题。好在xilinx官方给出了解决方案。

1.搜索原语<USR_ACCESS>,将原语例化到模块当中,可以通过上位机读走。

2.综合后打开综合,如下图:

3.点击Edit Device Properties如下图:

4.找到User ACCESS 里面填入<TIMESTAMP>,并保存。

5.后续31bit的数据分别如下图:,逻辑可以根据其值的含义进行解析。从而完成版本管理。