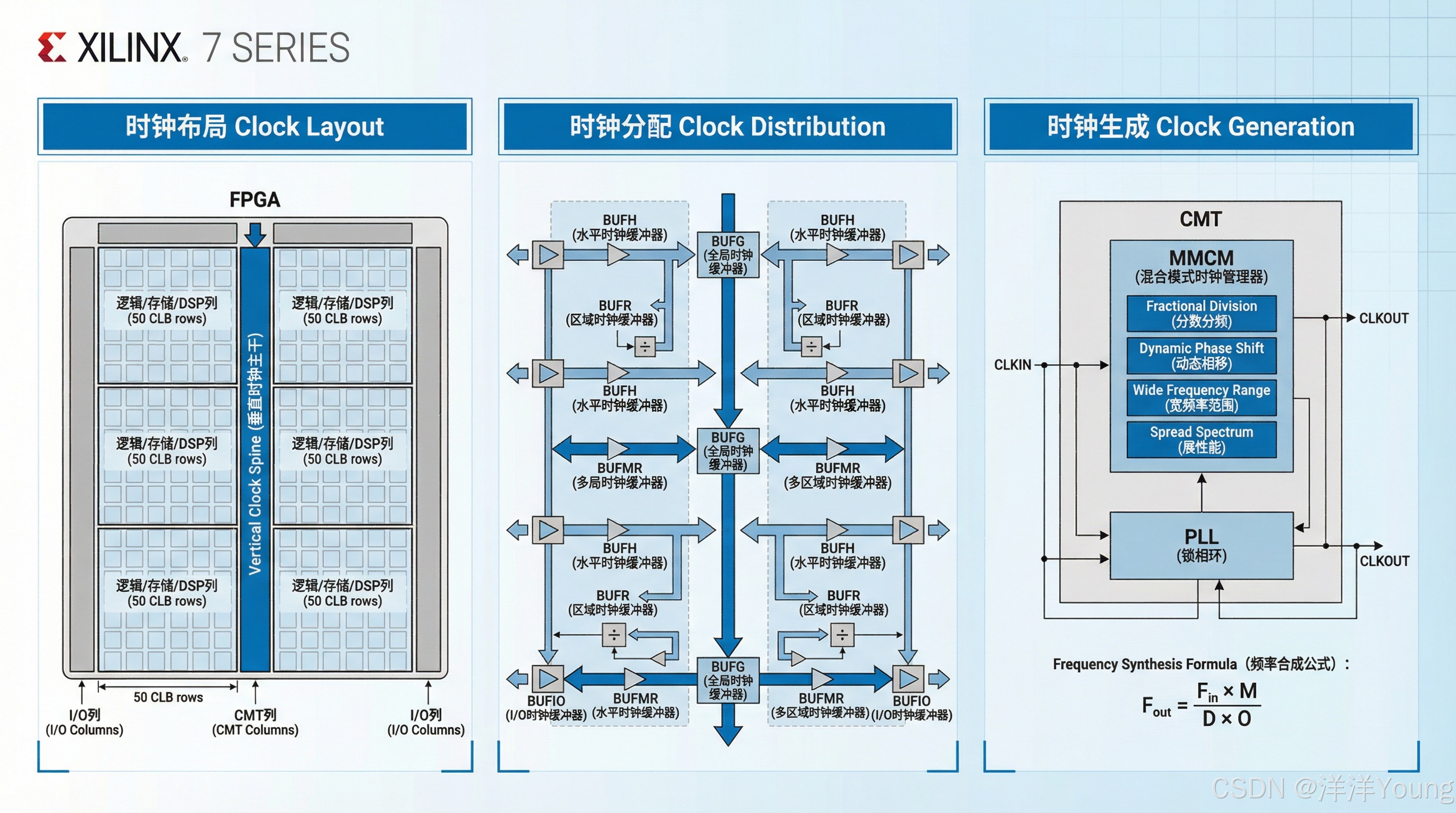

FPGA 的高性能时钟设计面临多重挑战:需为高速 I/O 及存储接口提供纯净的时钟信号,支持宽频率范围内的多时钟域,并在实现高性能的同时保持低功耗。Xilinx 7 系列 FPGA 基于 Virtex-6 的时钟架构,采用全系列统一的时钟系统,为开发人员提供了一套高效、可靠的时钟解决方案。本文主要介绍 Xilinx 7 Series 器件时钟设计所需要了解的知识,包括时钟布局、时钟分配与时钟生成。

目录

[1 Clock Region 时钟布局](#1 Clock Region 时钟布局)

[2 Clock Distribution 时钟分配](#2 Clock Distribution 时钟分配)

[3 Clock Generation 时钟生成](#3 Clock Generation 时钟生成)

[3.1 Clock Management Tile 时钟管理单元](#3.1 Clock Management Tile 时钟管理单元)

[3.2 MMCM 混合模式时钟管理器](#3.2 MMCM 混合模式时钟管理器)

[3.3 PLL 锁相环](#3.3 PLL 锁相环)

(图片由 Nano Banano Pro 生成)

在 FPGA 开发过程中,高性能时钟设计面临多重挑战:

1)需为高速 I/O 及存储接口提供高性能、纯净的时钟信号;

2)在宽频率范围内,支持多个时钟域;

3)实现高性能的同时保持低功耗。

1 Clock Region 时钟布局

Xilinx 7 系列 FPGA 基于 Virtex-6 的时钟架构,采用全系列统一的时钟系统,CMT 列与 I/O 列相邻,以支持高性能接口;每个时钟区域高度统一,包含 50 行 CLB;并且全局时钟资源优化,降低功耗。

All 7 series FPGAs split into uniform height clock regions. Each region has its own resources. All regions can share the available global resources.

Every clock region is 50 rows of CLBs tall. 25 rows above and 25 rows below the central horizontal clocking row (HROW).

All clock regions span from global vertical clock column to the left or right edge of the device.

- 所有 7 系列 FPGA 均被划分为等高的时钟区域。每个区域拥有专属资源,且所有区域均可共享可用的全局资源。

- 每个时钟区域的高度为 50 行 CLB,其中 25 行位于中央水平时钟行(HROW)之上,25 行位于其下。

- 所有时钟区域均从全局垂直时钟列延伸至器件的左边缘或右边缘。

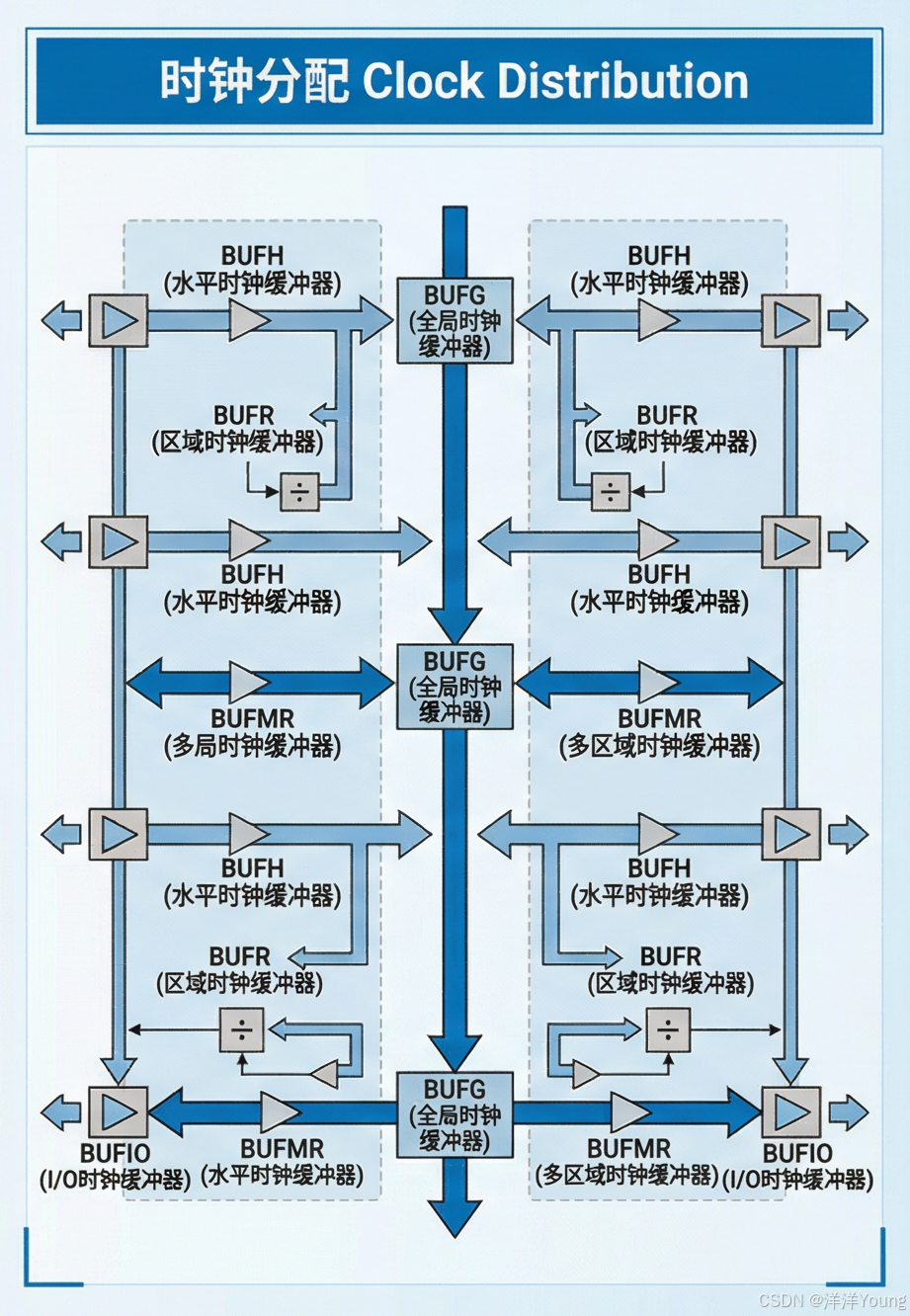

2 Clock Distribution 时钟分配

Xilinx 7 Series 器件提供了全局时钟缓冲器 BUFG,用于驱动全局时钟主干网络。BUFG 在整个器件的高度范围内分配时钟信号,每个器件设有 32 个 BUFG,位于垂直时钟 Spine 的中心位置。

- BUFG:全局时钟缓冲,用于驱动全局时钟

- BUFH:水平时钟缓冲,用于驱动水平时钟

- BUFR:区域时钟缓冲,支持分频功能

- BUFIO:I/O时钟缓冲,专用于驱动I/O逻辑

- BUFMR:多区域时钟缓冲,可驱动相邻区域

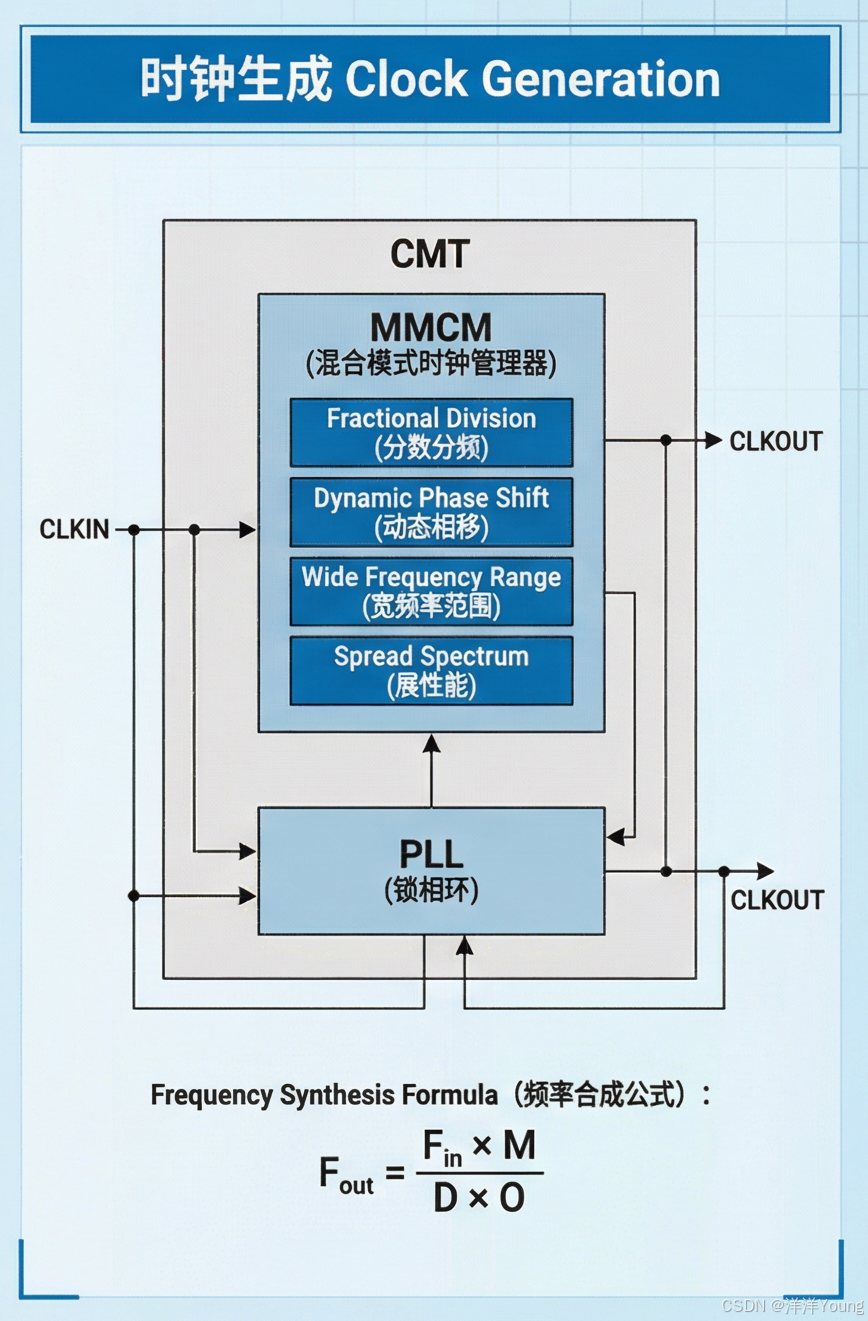

3 Clock Generation 时钟生成

3.1 Clock Management Tile 时钟管理单元

在 Xilinx 7 系列 FPGA 的时钟管理模块(CMT)中,同时包含一个功能完整的 MMCM 和一个相对简洁的 PLL。

此设计允许用户根据需求灵活选择:若无需 MMCM 提供的全部高级功能(如动态相位调整、分数分频等),则可使用面积更小的 PLL,从而释放出芯片空间。

3.2 MMCM 混合模式时钟管理器

MMCM 功能与 Virtex-6 MMCM 类似:

- 具备七路时钟输出及 Feedback 路径

- 支持输入时钟切换

- 可在 OUT0 和 FBOUT 上进行分数分频

- 支持动态相移

- 支持扩频时钟生成

3.3 PLL 锁相环

PLL 延续 Spartan-6 PLL / Virtex-6 MMCM 的特性:

- 具备六路时钟输出及 Feedback 路径

- 支持输入时钟切换