Reference: Zynq-7000 PCB Design Guide + Deepseek + 个人优化

Answer:

For better signal integrity, DDR2 and DDR3 clock, address, command and control signalsneed to be terminated. 根本目的是为了抑制信号在传输线末端反射造成的信号完整性恶化,确保接收端能准确识别逻辑电平。

下面进行详细分解:

1. 核心原理:阻抗匹配与反射消除

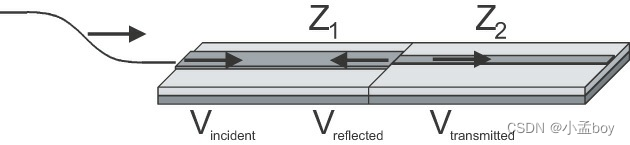

传输线效应:当信号频率升高(DDR2/3 数据率可达数百 Mbps 至 1.6+Gbps)或走线长度达到信号波长的一定比例时,PCB 走线不再是简单的"导线",而是需要被视为 传输线。传输线具有其特征阻抗(通常设计为 50 欧姆)。

信号反射:如果传输线的 终端负载阻抗 与 传输线特征阻抗 不匹配,信号到达末端时,能量无法被完全吸收,一部分会反射回源端。如下图:

这会导致:

-

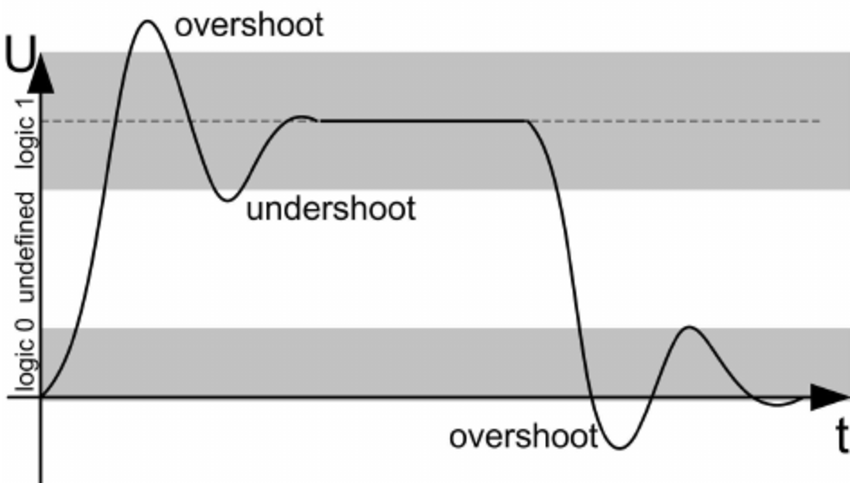

过冲/下冲:电压超出规定的逻辑高/低电平范围。如下图:

-

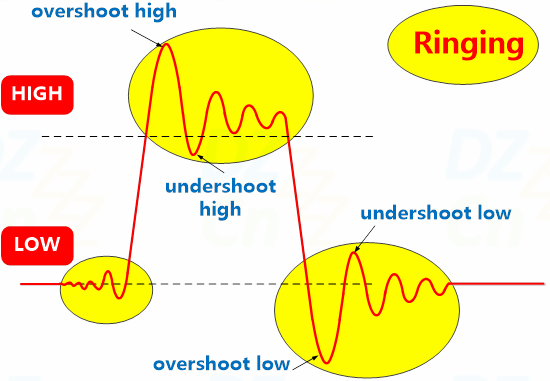

振铃:在逻辑电平切换后出现振荡,严重时会引发误触发。

-

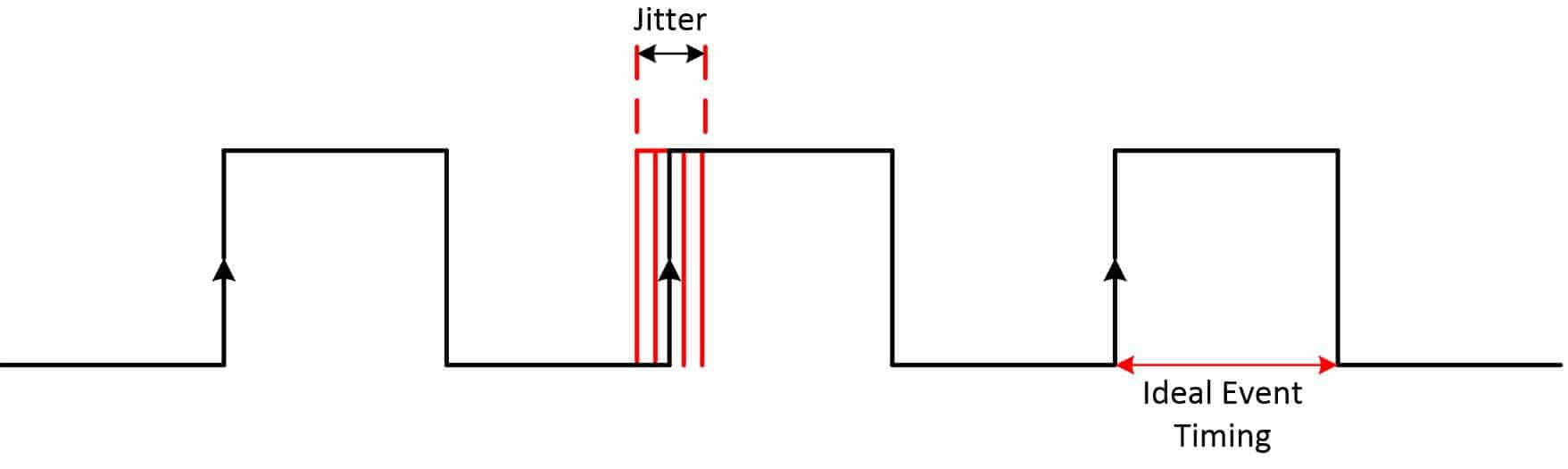

时序抖动:边沿变得不清晰,建立和保持时间窗口被压缩,甚至导致采样错误。如下图:

2. 为什么 DDR3 特别需要端接?

这与它们的工作模式和拓扑结构密切相关。

数据线(DQ,DQS):通常是点对点的(从控制器到单个存储器),或者采用多负载的 Fly-by 拓扑(DDR3 常见),其端接策略(如 ODT)相对独立。

时钟、地址 、命令、控制信号:这些是单向广播信号。一个控制器要驱动多个内存芯片(颗粒)。这些信号线会形成多点分支的拓扑,信号在到达线路末端的颗粒后,如果阻抗不连续,会产生强烈的反射。

高数据率与快速边沿:DDR3 的时钟频率很高,信号边沿非常陡峭(上升时间很短),这包含了丰富的高频成分,使得传输线效应更加显著。任何阻抗不连续点都容易成为反射源。

3. DDR3 端接方式

为了解决上述问题,终端端接在内存控制器和内存模块上被广泛应用。

DDR3 的端接:

-

Fly-by 拓扑:DDR3 的地址/命令/控制/时钟信号线采用 "fly-by"走线,即信号依次经过每个内存颗粒,最后在线路末端进行端接。这减少了支线长度,改善了时序一致性。

-

片内端接:DDR3 颗粒内部集成了可编程的片上端接电阻,不仅用于数据线(DQS),也可用于地址/命令/控制线。

-

动态开关:控制器可以动态地打开或关闭特定颗粒的 ODT。例如,当向某个颗粒写数据时,只打开该颗粒的 ODT,而关闭其他颗粒的 ODT,从而减少不必要的负载和功耗,并优化信号质量。

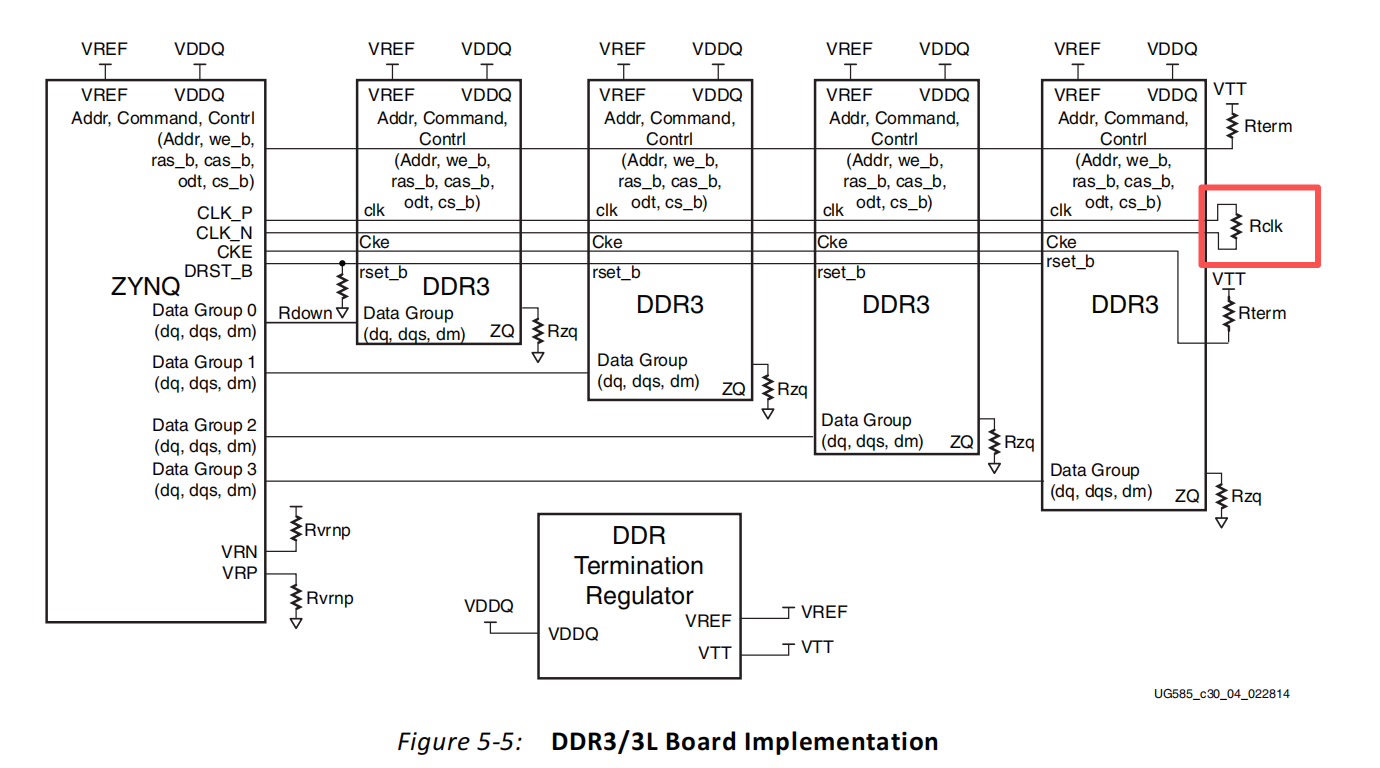

DDR3 的 CLK 端接示意图如下:

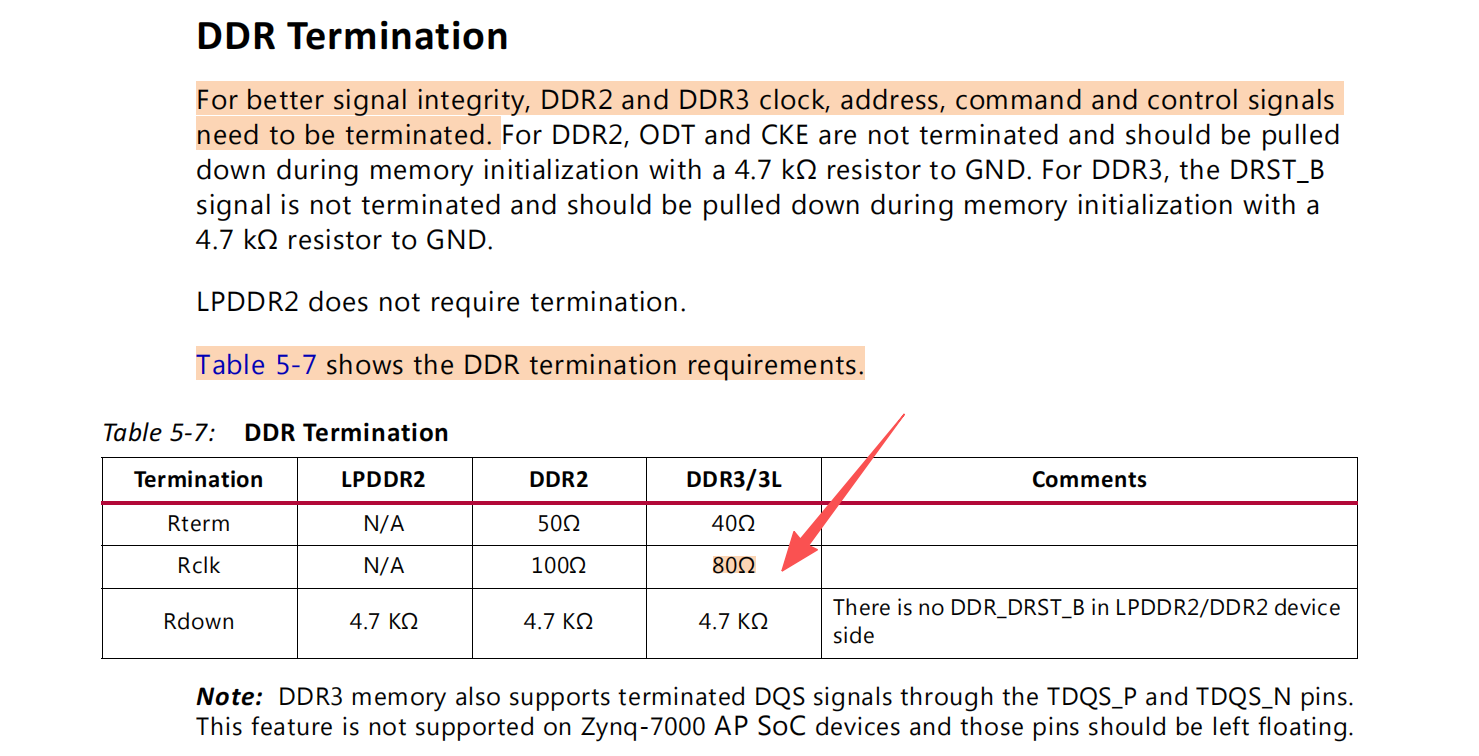

DDR3 的 CLK 端接参数如下:

4. 总结

对于 DDR3 系统,对时钟、地址、命令和控制信号进行终端端接(包括源端串联端接和负载端并行端接)是一项强制性的设计要求。它是解决高速信号在多点广播拓扑中因阻抗不匹配而产生反射问题的关键技术,是保证整个内存子系统信号完整性和时序正确性的基石。

DDR3 通过 Fly-by 拓扑和更灵活的 ODT 技术,在此基础之上进一步提升了性能和信号质量。