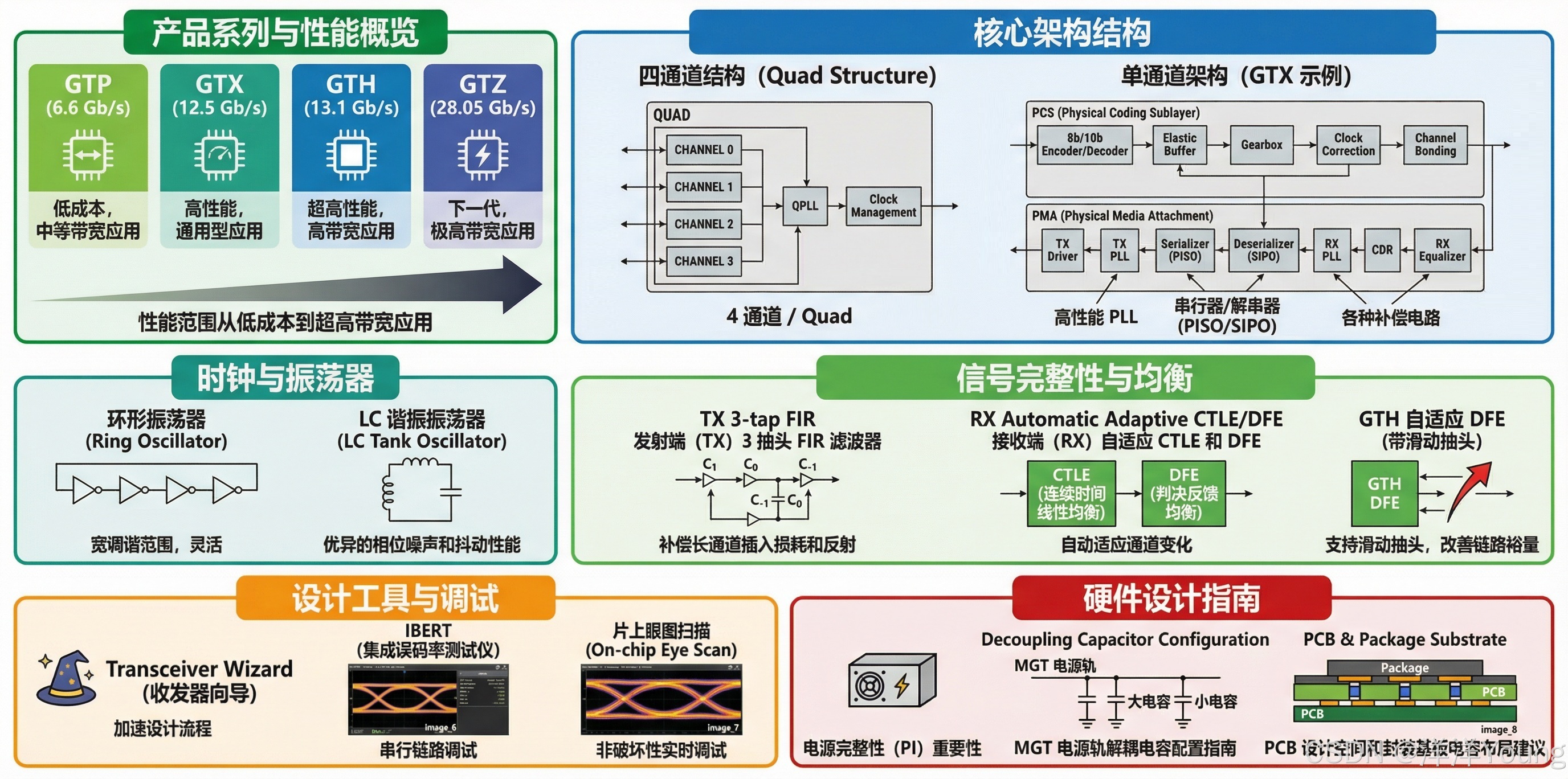

Xilinx 7 系列器件提供了四类高速串行通信收发器,分别是 GTP、GTX、GTH 和 GTZ,支持 500Mbps 至 28.05 Gbps 传输速率,覆盖不同性能与成本需求。本文主要介绍 Xilinx 7 系列器件高速串行收发器概述、核心架构与时钟设计。

目录

[1 Transceivers Overview 收发器概述](#1 Transceivers Overview 收发器概述)

[2 Transceivers Architecture 收发器架构](#2 Transceivers Architecture 收发器架构)

[2.1 Transceivers Layout 收发器物理布局](#2.1 Transceivers Layout 收发器物理布局)

[2.2 Transceivers Channel 收发器单通道设计](#2.2 Transceivers Channel 收发器单通道设计)

[3 Transceivers Clocking 收发器时钟设计](#3 Transceivers Clocking 收发器时钟设计)

(图片由 Nano Banano Pro 生成)

1 Transceivers Overview 收发器概述

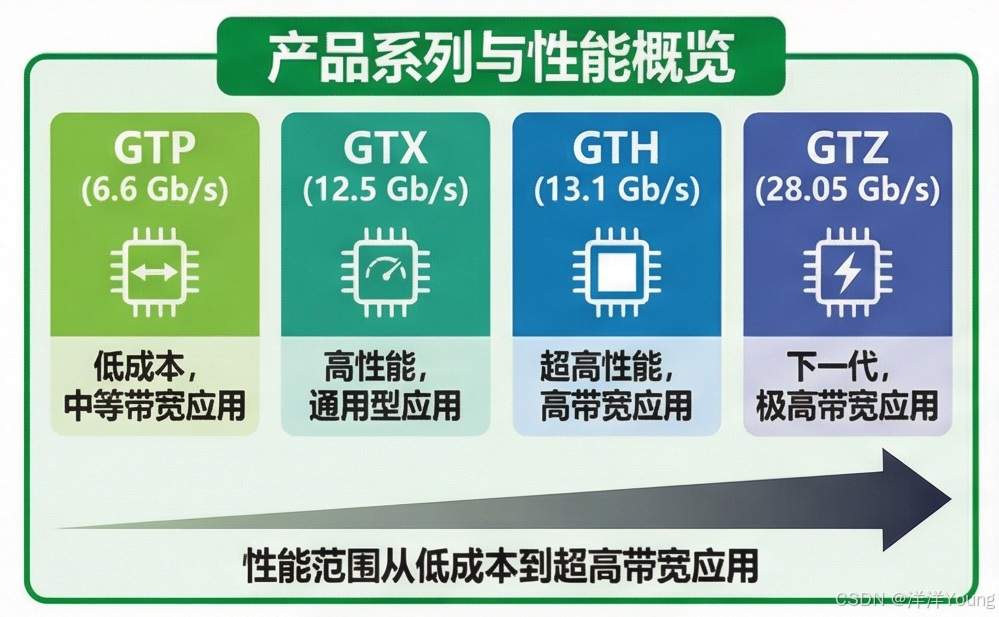

Xilinx 7 系列器件提供了四类高速串行通信收发器,分别是 GTP、GTX、GTH 和 GTZ,覆盖不同性能与成本需求。

- GTP:低成本低功耗,速率 < 6.6 Gbps,适合大批量、低功耗场景。

- GTX:中端主流,速率 < 12.5 Gbps,平衡性能与成本。

- GTH:高性能低功耗,速率 < 13.1 Gbps,适合高通道数、高带宽应用。

- GTZ:最高性能,速率 < 28.05 Gbps,适用于 100G/400G 网络、光传输等。

其中 GTP 是 Artix-7 中用于高速串行通信的模块,支持 500 Mb/s 至 6.6 Gb/s 的传输速率,具有低功耗、高集成度的特点,支持多种通信协议(如 PCIe、SATA、SRIO、Interlaken、XAUI等),支持 8b/10b 编解码、64b/66b 编码、PRBS 生成与检测、时钟校正、通道绑定等功能。

2 Transceivers Architecture 收发器架构

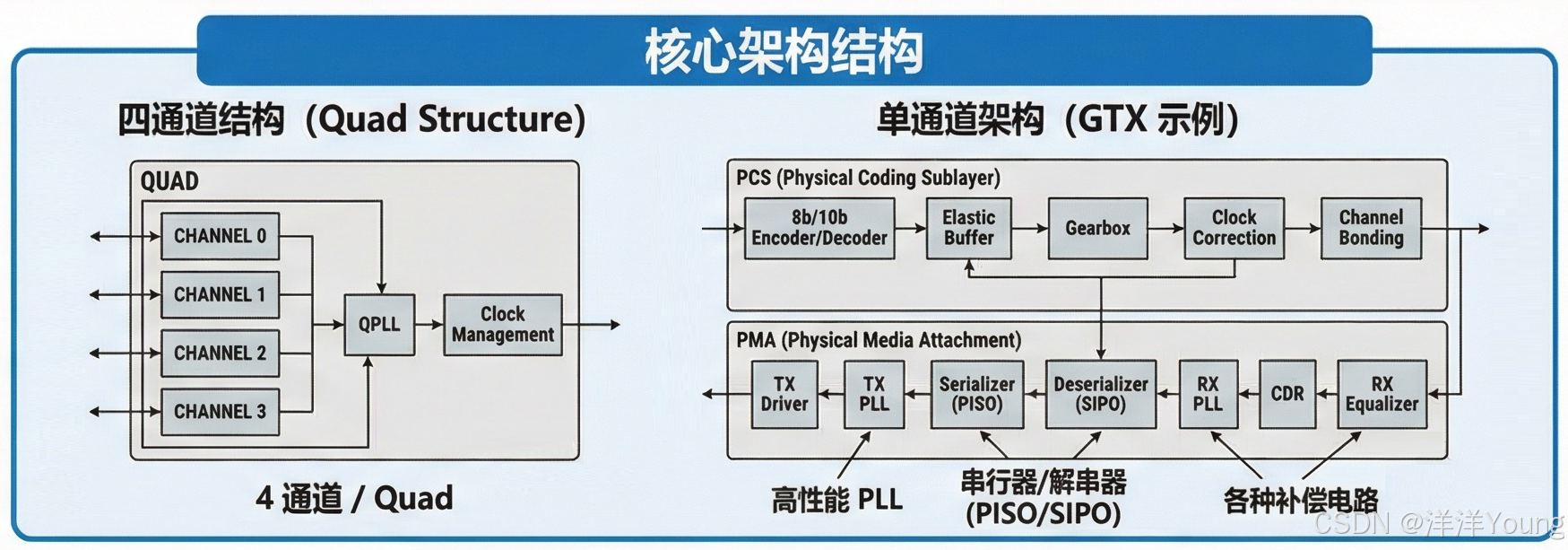

7 系列收发器以四通道(Quad Structure)形式组织,每个 Quad 包含 4 个发射器(TX)与 4 个接收器(RX)。锁相环(QPLL)置于收发器 Quad 内部,并且被设计为一个独立的功能块。

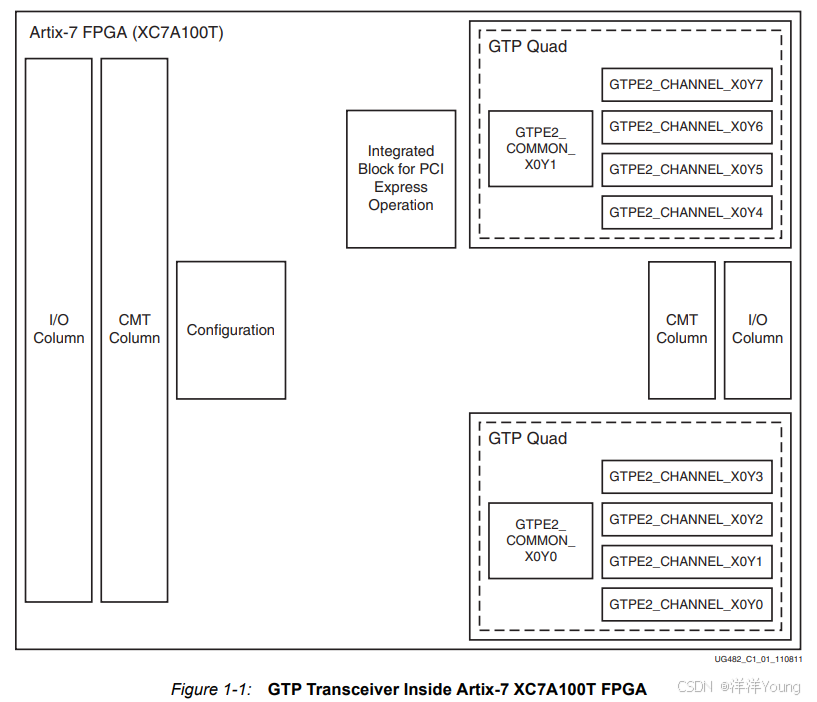

2.1 Transceivers Layout 收发器物理布局

收发器 Quad 在芯片的一侧或两侧以列状形式排列:

- Artix-7:收发器位于芯片顶部和底部(采用引线键合封装芯片)

- Kintex-7:在同一列中混合布置收发器与普通 I/O

- Virtex-7:采用完整的收发器列

2.2 Transceivers Channel 收发器单通道设计

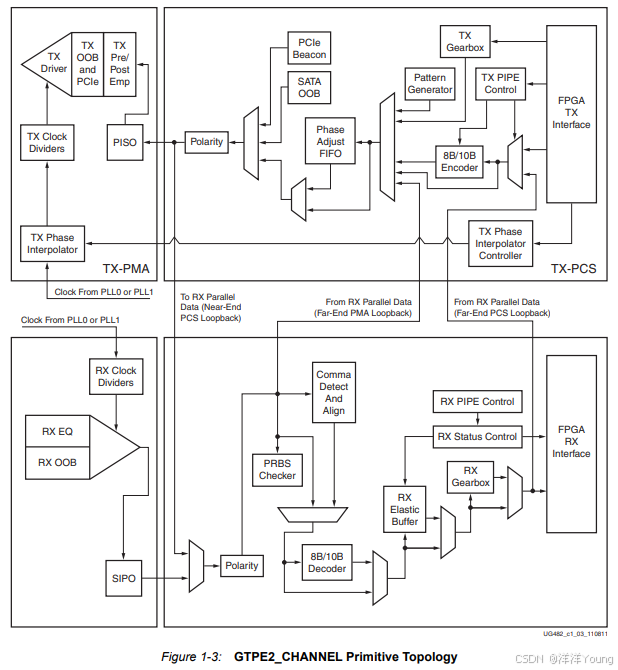

7 系列 FPGA 收发器采用分层架构设计,分为物理媒体接入层(PMA)和物理编码子层(PCS)。PMA 负责模拟信号处理,包括差分输入/输出缓冲器、时钟数据恢复(CDR)、均衡器和时钟生成电路;PCS 则处理数字逻辑功能,如 8b/10b 编解码、通道绑定、时钟校正和齿轮箱(支持 64b/66b 编码)。

每个 GTP 收发器通道(GTPE2_CHANNEL)独立包含发射器(TX)和接收器(RX),四个通道与一个共享的 GTPE2_COMMON 模块(集成两个环形振荡器PLL)构成一个 Quad。

3 Transceivers Clocking 收发器时钟设计

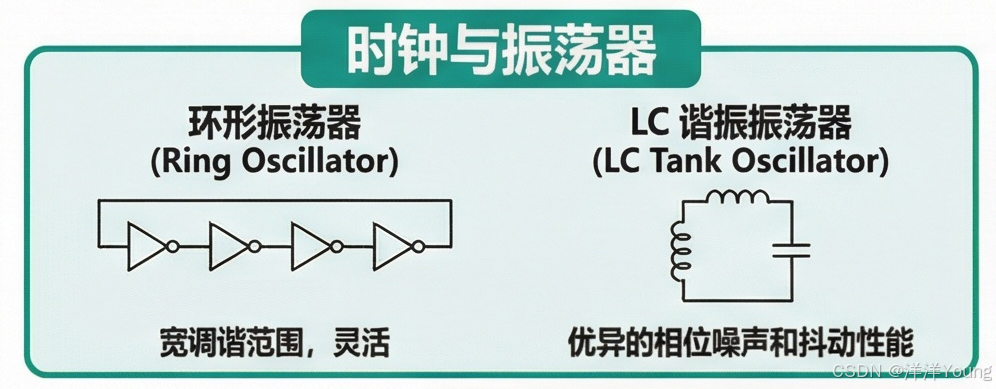

7 系列器件支持两种时钟生成技术,分别是环形振荡器(Ring Oscillator)和 LC 谐振振荡器(LC Tank Oscillator)。

Ring 振荡器用于实现灵活性,支持宽频率范围,缺点是高频时钟随机抖动差(10Gbps 时 Jitter 为 1-3ps rms RJ)。

LC Tank 振荡器用于高性能场景,10Gbps 速率下 Jitter 为 300-600fs ms RJ,缺点是频率范围窄,且牺牲面积和集成度。

|-------------|-----|-----|-----|-----|

| PLL 类型 | GTP | GTX | GTH | GTZ |

| LC Tank 振荡器 | | √ | √ | √ |

| Ring 振荡器 | √ | √ | √ | |

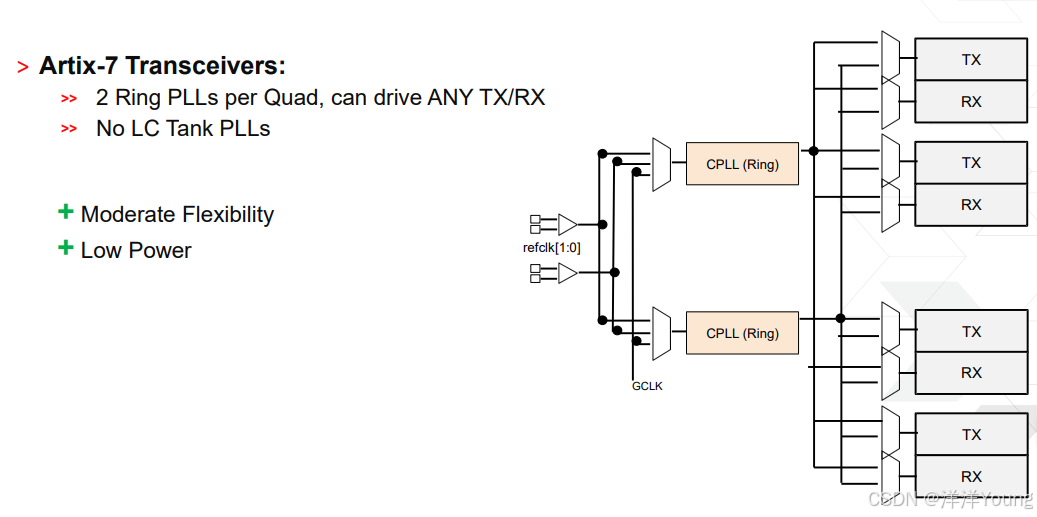

Artix-7 GTP 收发器:

- 每个 Quad 内部包含 2 个环形 PLL,可驱动任意通道的 TX/RX

- 无 LC Tank PLL

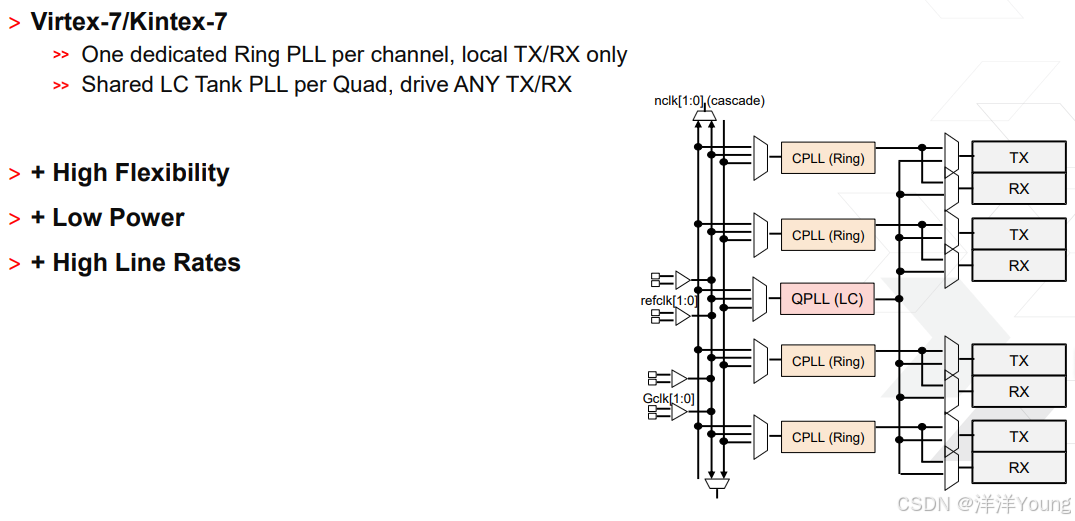

Virtex-7/Kintex-7 GTX/GTH 收发器

- 每通道对应 1 个专用环形 PLL,仅驱动对应通道的 TX/RX

- 每个 Quad 内部包含 1 个 LC Tank PLL,可驱动任意通道的 TX/RX

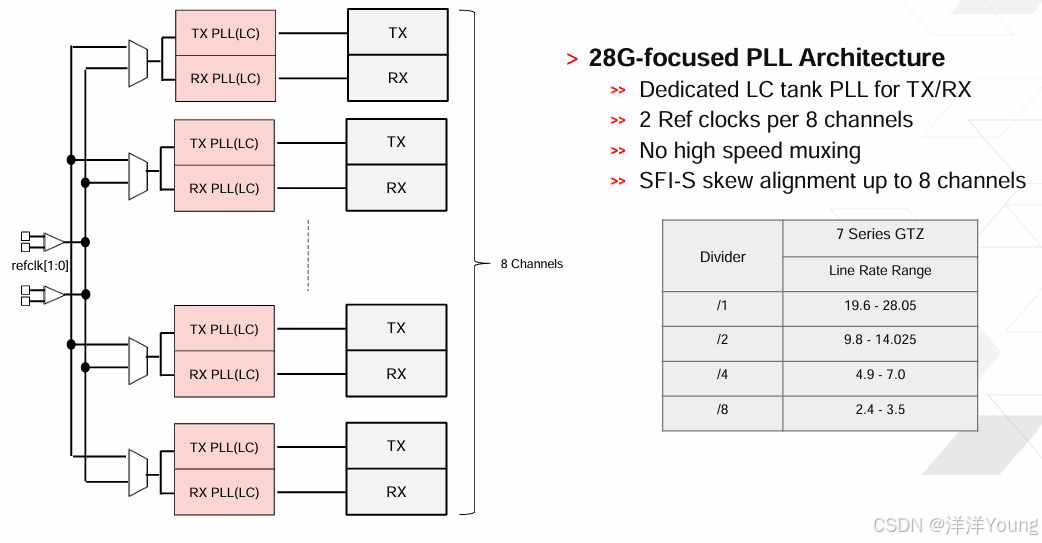

Virtex-7 GTZ 收发器

- 28Gbps 专用 PLL 架构

- 每个通道的 TX/RX 使用专用的 LC Tank PLL

- 每 8 个通道共享 2 个参考时钟