本篇教程基于ShiMetaPi 研发的FPGA+ARM开发板------GM-3568JHF展开。

01 案例简介

本案例旨在ARM 端运行 Linux 系统,基通过 FSPI 总线对 FPGA DRAM 进行读写测试。

02 ARM端和FPGA端通信流程

2.1 ARM端实现SPI Master功能

打开SPI设备节点:打开/dev/spidev4.0设备节点。

配置FSPI总线:使用ioctl命令配置FSPI总线的极性、相位、通信速率和数据长度等参数。

选择传输模式:可以选择单线模式、双线模式或四线模式。当设置为四线模式时,数据的发送和接收都将采用四线模式。本案例仅支持四线模式。

数据传输:将数据发送至FSPI总线,并从FSPI总线读取数据。

校验数据:校验传输的数据,然后打印出读写速率和误码率。

2.2 FPGA端实现SPI Slave功能

数据存储:FPGA将SPI Master发送的数据保存至DRAM。

数据读取:当SPI Master发起读数据请求时,FPGA从DRAM读取数据,并通过FSPI总线传输至SPI Master。

03 操作流程

打开终端,将本案例 bin 目录下(05-开发资料\软件开发资料\linux_demo\smdt_fpga_fspi_demo\bin)的可执行程序 smdt_spi_rw 拷贝至开发板文件系统 (源码可以在 src 路径下查看)。

#修改 Linux 内核日志的显示级别,内核的日志级别被设置为只显示紧急或更高级别的消息

echo 1 4 1 7 > /proc/sys/kernel/printk在终端执行如下指令,切换到 smdt_fpga_fspi_demo 可执行程序所在目录

#切换到 smdt_spi_rw 可执行程序所在目录

cd '可执行文件所在目录'

#查看 smdt_spi_rw 是否在该目录下

ls若可执行文件 smdt_spi_rw 在当前目录下,则修改可执行文件的权限

#修改文件权限

chmod 777 smdt_spi_rw

#查询是否修改成功

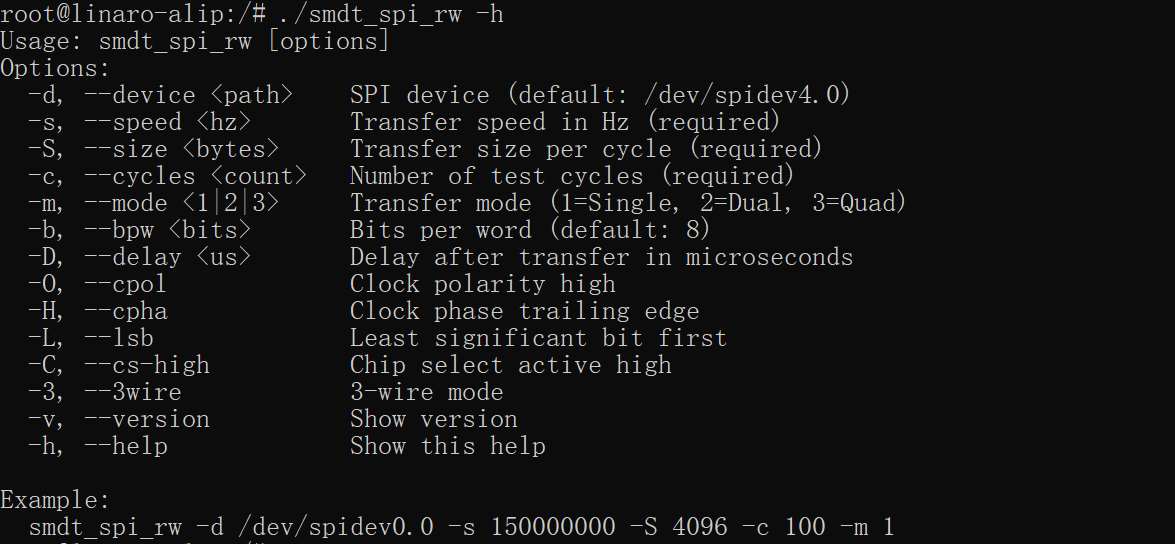

ls -ld smdt_spi_rw查询确认文件修改权限成功后,执行 ./smdt_spi_rw -h 可以查看该程序的帮助信息

#查看帮助信息

./smdt_spi_rw -h执行结果如下图:

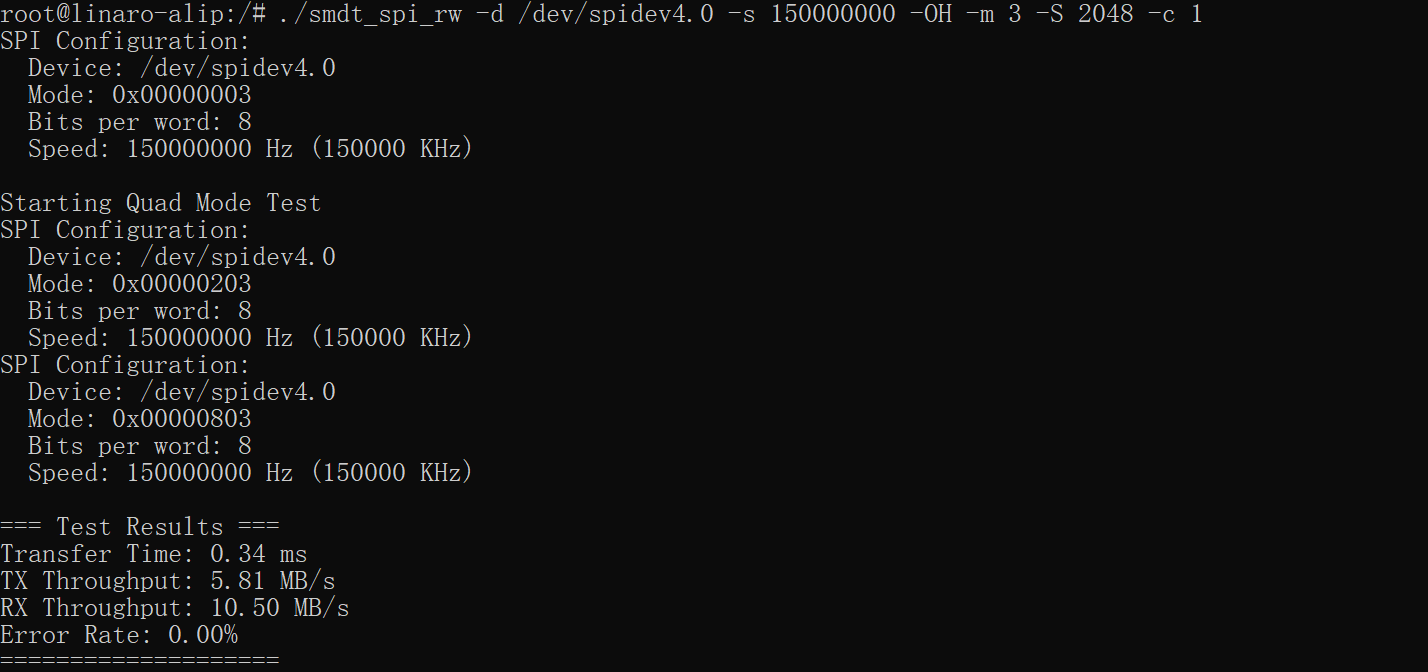

3.1 功能测试

输入以下指令。在ARM端,通过配置为四线模式的FSPI总线,将2048字节的随机数据写入FPGA的DRAM中,随后读取这些数据进行校验,并打印出FSPI总线的读写速度以及计算出的误码率,执行结果如下图所示。

./smdt_spi_rw -d /dev/spidev4.0 -s 150000000 -OH -m 3 -S 2048 -c 1

# 参数说明如下:

# `-d`:用于指定设备节点。

# `-s`:用于设置通信时钟的频率,单位是赫兹(Hz)。

# `-O`:表示时钟极性反转,即CPOL(Clock Polarity)设置为1。

# `-H`:表示在时钟周期开始时的第二个边沿采集数据,即CPHA(Clock Phase)设置为1。

# `-m`:选择传输模式,其中1代表单线模式,2代表双线模式,3代表四线模式。

# `-S`:设置传输数据的大小,单位是字节(Byte)。

# `-c`:设置循环传输数据包的次数。

从上图可知,本次实测写速率为 5.81 MB/s,读速率为 10.5 MB/s,误码率为 0.00%。

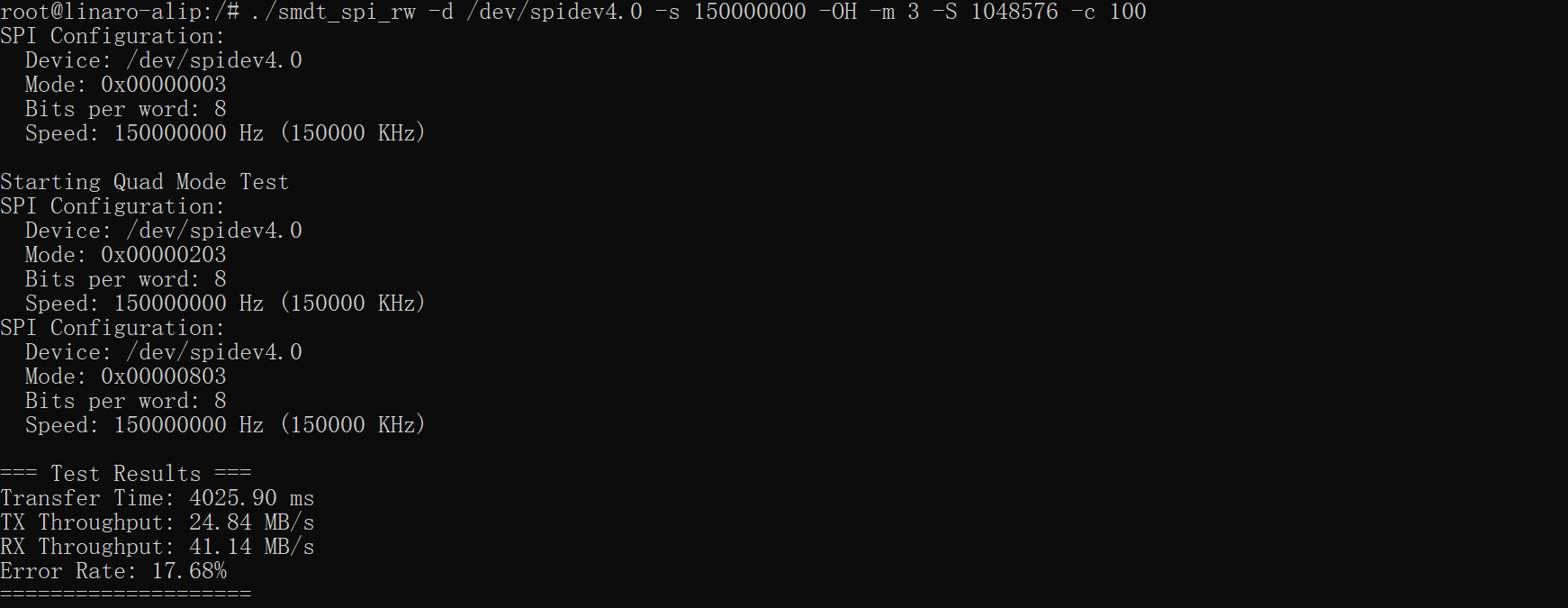

3.2 性能测试

进行性能测试时,需要将FSPI总线的通信时钟频率设置至150MHz。在此设置下,ARM将通过FSPI总线向FPGA的DRAM写入1MB的随机数据,随后读取这些数据,并重复此过程100次。测试过程中不进行数据校验,最终将输出FSPI总线的读写速度和错误率。执行结果如下图。本案例设计一次读写 2048Byte 随机数据至 FPGA DRAM,因此误码率较高。

./smdt_spi_rw -d /dev/spidev4.0 -s 150000000 -OH -m 3 -S 1048576 -c 100