本博文主要交流设计思路,在本博客已给出相关博文160多篇,希望对初学者有用。注意这里只是抛砖引玉,切莫认为参考这就可以完成商用IP设计。

RoCE v2 子系统模型是用来模拟 RoCE v2 功能仿真模型。在 RoCE v2 协议中,本地主机与远程主机之间往往需要进行复杂的指令、信息、数据交互,使得在进行仿真验证时如何模拟复杂网络环境成为一个急需解决的问题。

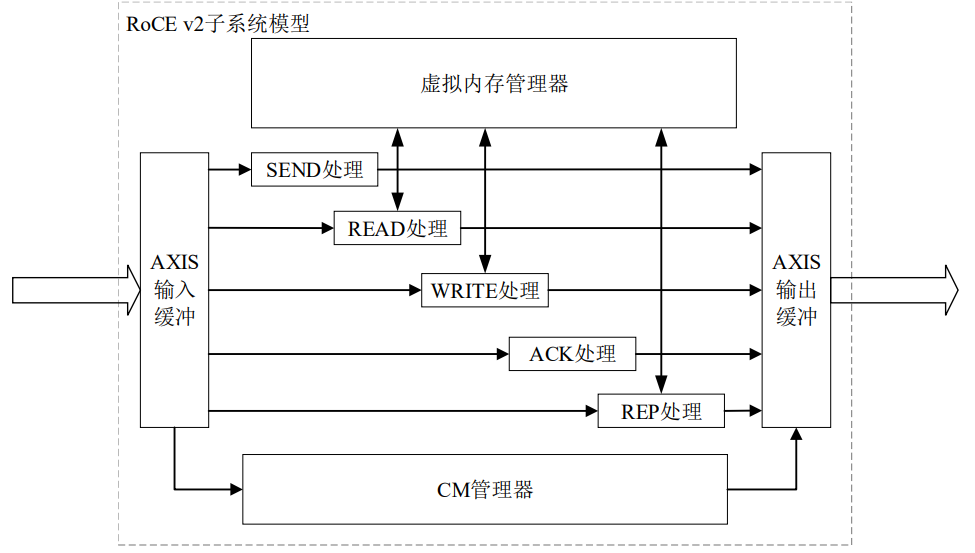

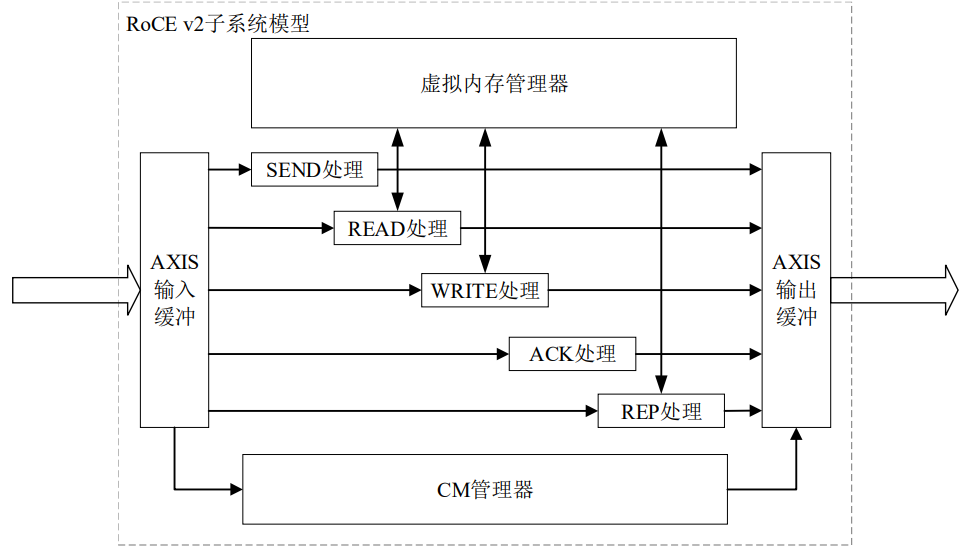

因此,本IP设计了一个RoCE v2 子系统模型并将其整合到验证平台中,使得 RoCE v2 高速数据传输系统能够进行复杂网络环境下的仿真验证。RoCE v2 子系统模型包含两个 AXIS 总线接口、一个虚拟内存管理器、一对输入输出缓冲、五个处理单元及一个 CM 管理器。

RoCE v2 子系统模型结构如图 所示。

1 所示:

图1 RoCE v2 子系统模型结构如图

AXIS 总线接口及输入输出缓冲:用于从 DUT 的 AXIS 总线接口接收网络数据包或向 DUT 的 AXIS 总线接口发送数据包。当接收到数据包时,将数据包存放到输入缓冲内并判断其操作类型,而后根据不同的操作类型将数据包分发到 CM 管理器或不同的包处理单元中。当需要发送数据包时,将数据包存放到输出缓冲中,输出缓冲内的数据包将按照存放顺序依次发出。

虚拟内存管理器:用于模拟远程主机的内存。由于 RoCE v2 协议是直接操作远程主机内存的协议,为了便于判断数据正确性,需要在 RoCE v2 子系统模型设置虚拟内存管理器用于模拟远程主机内存,来配合 DUT 进行数据读取或数据写入操作。

CM 管理器:用于进行连接管理和队列管理。配合 DUT 进行连接、断链、创建队列、删除队列等操作。同时存储队列信息,在收到数据包时进行队列有效性判断。

五个处理单元:分别用于处理 SEND、READ、WRITE、ACK 及 REP 包。其中,READ 处理单元、WRITE 处理单元及 REP 处理单元与虚拟内存管理器相连,这三个单元同时也负责数据的存取操作控制。

除此之外,RoCE v2 子系统模型也负责接收及发送 ARP 及 ICMP 数据包,其用于验证 DUT 中网络嗅探模块相关功能。

B站已给出相关性能的视频,如想进一步了解,请搜索B站用户:专注与守望