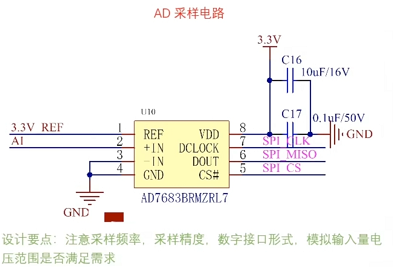

这个电路是基于AD7683BRMZRL7 的 16 位高精度单通道 AD 采样方案,核心功能是将模拟输入信号转换为 16 位数字量,通过 SPI 接口输出给主机。下面从模块拆解 、工作原理 、设计要点展开分析:

一、核心模块与元件作用

1. 电源去耦模块(C16、C17)

- C16(10uF/16V):低频去耦电容,滤除 3.3V 电源的低频纹波,缓解电源瞬态波动,保证 ADC 供电稳定性。

- C17(0.1uF/50V):高频去耦电容,滤除电源的高频噪声(如开关电源纹波、电磁干扰),减少噪声对 ADC 采样精度的影响。

- 布局要求:必须紧贴 ADC 的 VDD 引脚放置,缩短电源回路走线,降低寄生电感。

2. 参考电压模块(3.3V REF)

- 3.3V REF :直接连接到 ADC 的

REF引脚(1 脚),作为 ADC 的参考电压,决定模拟输入的电压范围(0~V_REF,即 0~3.3V)。 - 精度影响:参考电压的稳定性直接决定采样精度,3.3V REF 的纹波和漂移会引入采样误差,若需更高精度,可替换为精密参考源(如 REF3033)。

3. 模拟输入模块(AI、IN-/GND)

- AI :模拟输入信号,连接到 ADC 的同相输入引脚

IN(2 脚),信号范围需满足 0~3.3V(与参考电压匹配)。 - IN-(3脚)接地 :采用单端输入模式,适合采集单极性模拟信号(如传感器输出的 0~3.3V 电压)。若需差分输入,可将 IN - 接另一路模拟信号。

4. 数字接口模块(SPI 通信)

ADC 通过 SPI 三线接口与主机通信,引脚定义:

| 引脚 | 功能 | 说明 |

|---|---|---|

| CS(5 脚) | 片选信号 | 低电平有效,拉低时启动 AD 转换并允许数据读取 |

| DOUT(6 脚) | SPI 数据输出 | 转换完成后输出 16 位数字量(MSB 优先) |

| DCLKOUT(7 脚) | 时钟输出 | 悬空未用(本电路由主机时钟驱动,无需 ADC 输出时钟) |

二、核心工作原理

AD7683 是逐次逼近型(SAR)ADC,转换流程如下:

- 启动转换 :主机拉低

CS引脚,ADC 启动 16 位逐次逼近转换。 - 采样保持:模拟输入信号被采样并保持在内部电容上。

- 数字转换:通过内部 DAC 和比较器,逐位确定数字量,完成 16 位转换(最高 250kSPS 采样率)。

- 数据输出 :转换完成后,主机通过

SCLK时钟同步,从DOUT读取 16 位数字量(分辨率为 )。

)。 - 结束转换 :主机拉高

CS,ADC 进入待机模式,降低功耗。

三、设计要点解读

-

采样频率匹配AD7683 最高采样率为 250kSPS,需保证 SPI 时钟速度(最高 20MHz)与采样率匹配,避免数据传输瓶颈。若需更高采样率,需选择更快的 SPI 主机或 ADC。

-

采样精度保障

- 参考电压稳定性:3.3V REF 需低纹波(<1mV),必要时可在 REF 引脚增加 100nF 滤波电容。

- 输入噪声抑制:若模拟输入有高频噪声,可在 AI 与 IN 引脚之间增加 RC 低通滤波(如 1kΩ 电阻 + 100nF 电容),减少噪声对采样的影响。

- 电阻精度:若需分压适配输入范围,需使用 1% 以上精度的电阻,避免引入额外误差。

-

数字接口时序SPI 通信需严格遵循 AD7683 的时序要求:

CS拉低后,需等待至少 100ns 再发送 SCLK。- 16 位数据传输完成后,需拉高

CS以结束本次转换。

-

输入电压范围验证模拟输入电压必须在 0~V_REF(0~3.3V)范围内,否则 ADC 会饱和输出全 0 或全 1。若输入信号超过 3.3V,需增加钳位电路(如 TVS 管、稳压管)保护 ADC。

四、典型应用场景

该电路适合高精度单极性信号采集,例如:

- 传感器信号采集(如温湿度传感器、压力传感器的 0~3.3V 输出);

- 电池电压监测(0~3.3V 范围内的电压采样);

- 工业模拟量采集(如 0~3V 电流环信号转换)。