在三相电机驱动系统的设计中,芯片的逻辑接口易用性、电源保护完备性与封装选择灵活性,是与驱动性能同等重要的考量因素。EG2124A 作为屹晶微电子三相驱动系列中的重要成员,在继承单芯片集成三路半桥驱动的基础上,做出了两项关键优化:采用HIN/LIN双通道高电平有效的标准化同相输入逻辑 ,并为VCC与VB电源提供独立的欠压保护(UVLO)。同时,其提供TSSOP20与QFN24两种封装,为不同空间约束的应用提供了选择。本解析将聚焦于其相较于EG2133的**"逻辑标准化"与"保护增强"改进**,系统阐述其如何降低软件复杂度、提升系统鲁棒性,并为追求高可靠性、易开发的三相无刷电机驱动项目提供一个均衡而实用的解决方案。

一、芯片核心定位

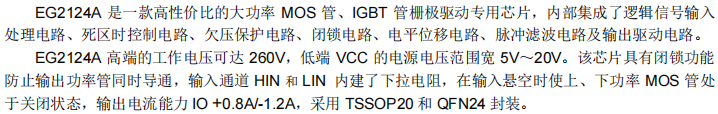

EG2124A 是一款逻辑接口标准化、保护功能增强的三相独立半桥驱动芯片。它在单芯片内集成三路260V耐压的半桥驱动器 ,每路驱动能力为0.8A/1.2A ,并通过采用HIN和LIN均为高电平有效 的标准逻辑、集成VCC/VB双路欠压保护 ,显著提升了系统的易用性与安全性,是EG2133的理想互补与升级选择。

二、关键电气参数详解

电源电压与保护特性

-

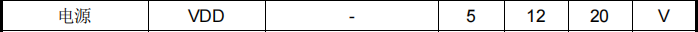

VCC工作电压范围:5V 至 20V

满足绝大多数MOS管驱动需求,推荐典型工作电压为12V。

-

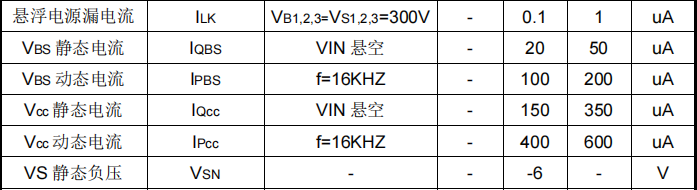

VCC欠压保护(UVLO):

开启电压(Vcc(on)):4.3V(典型)

关断电压(Vcc(off)):4.2V(典型)

确保电源电压充足后芯片才工作,迟滞小,反应灵敏。

-

VB欠压保护(UVLO):

开启电压(VB(on)):4.1V(典型)

关断电压(VB(off)):4.0V(典型)

独立监控每路高压侧自举电源,防止高侧因供电不足而驱动不良。

-

静态电流(Icc):< 350μA(典型,输入悬空)

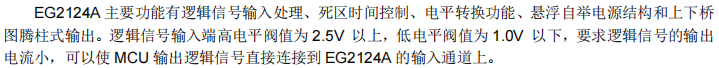

输入逻辑特性(核心简化点)

- HIN1/2/3(高端输入)与 LIN1/2/3(低端输入)均为高电平有效,且均内置下拉电阻(典型240kΩ)。

高电平阈值:> 2.5V

低电平阈值:< 1.0V - 逻辑兼容性:采用最直观的同相控制逻辑(HIN控制HO,LIN控制LO),与绝大多数MCU及PWM控制器接口无缝连接,极大降低了软件编程复杂度与出错概率。

- 悬空安全状态:输入悬空时均被下拉至低电平,输出HO=LO=0,处于安全关断状态。

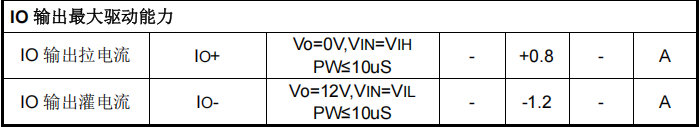

输出驱动能力

- 拉电流能力(IO+):0.8A(典型)

- 灌电流能力(IO-):1.2A(典型)

驱动能力定位:略低于EG2133(1.2A/1.4A),专注于驱动主流中小功率MOSFET,满足大多数三相电机驱动需求。

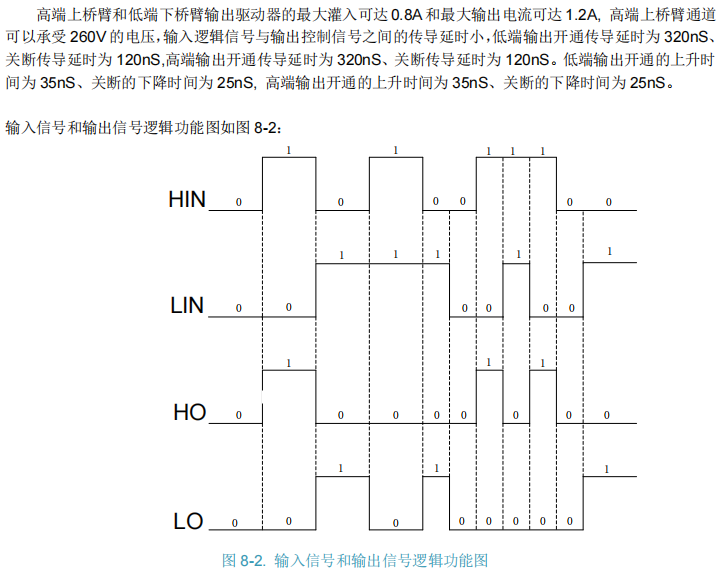

开关时间特性(典型值 @ VCC=12V, CL=1nF)

- 低端输出(LO)与高端输出(HO)时序一致:

开通延时(Ton):320ns

关断延时(Toff):120ns

上升时间(Tr):35ns

下降时间(Tf):25ns

特点:高低侧开关时间参数完全对称,有利于三相驱动的波形平衡,简化控制算法。

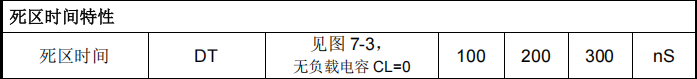

内部死区时间

- 死区时间(DT):100ns(典型,范围50ns - 300ns)

芯片内部固定,有效防止桥臂直通。

高压耐受能力

- 高端悬浮电源耐压:260V

适用于单相整流或较低电压的三相整流应用场景。

三、芯片架构与工作原理

三相独立半桥集成架构:

- 内部集成三套完全独立的驱动通道,包括逻辑处理、电平位移、UVLO和输出级,共享VCC和GND。

标准化同相逻辑与互锁机制:

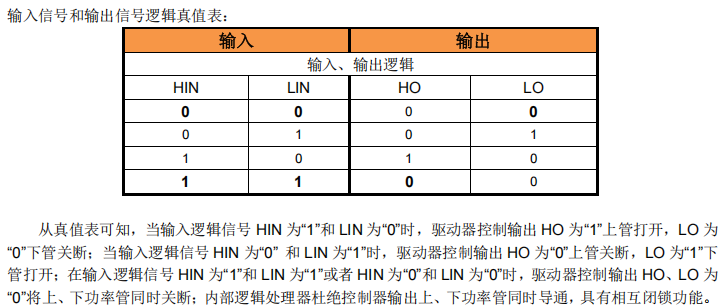

- 逻辑真值表(以其中一路为例):

HIN=1, LIN=0 -> HO=1, LO=0 (上管开,下管关)

HIN=0, LIN=1 -> HO=0, LO=1 (上管关,下管开)

HIN=0, LIN=0 或 HIN=1, LIN=1 -> HO=0, LO=0 (强制全关)

闭锁功能:当输入相同时(同为高或低),输出强制全关,提供基础的硬件直通保护。

双路独立欠压保护(UVLO):

- 分别监测VCC和每路的VB电压,任何一路电压不足都会强制关闭对应输出,增强了系统在电源波动或启动过程中的可靠性。

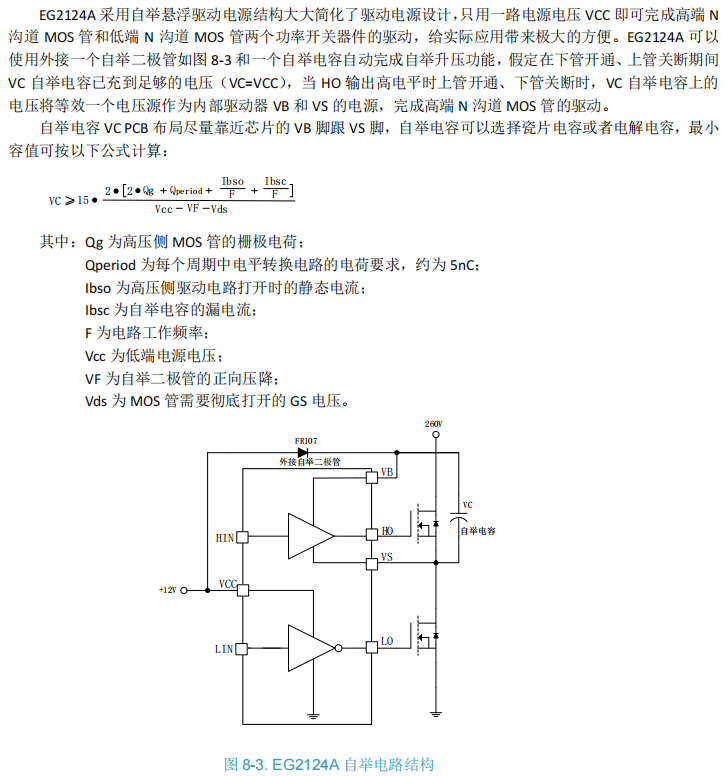

自举悬浮电源设计:

- 每路高端驱动需外接自举二极管和电容。

四、应用设计要点

逻辑接口设计(极为简单):

- 软件控制逻辑直观:需要开启哪一侧MOS管,就向对应的HIN或LIN输出高电平。

- 紧急停机:将所有路的HIN和LIN同时置为低电平(或同时置为高电平),即可实现全局快速硬件关断。

电源与去耦设计:

- VCC引脚:必须就近放置 0.1μF 陶瓷电容和 10μF 以上电解电容。

- 利用其较低的UVLO阈值(4.3V),可适应更宽范围的电源输入,但需确保最低工作电压高于此值。

自举电路设计:

- 电容(Cb)计算:数据手册提供了详细的计算公式,需根据高侧MOS管的栅极电荷(Qg)、工作频率(F)、VCC电压及二极管压降(VF)综合计算。初始设计可选用0.47μF - 1μF 的陶瓷电容。

- 二极管(Db)选型:必须选用快恢复二极管(如UF4007)。

- 布局:自举电容和二极管应尽量靠近对应的VB和VS引脚。

PCB布局规范(关键,尤其对于QFN封装):

- 功率地与信号地分离:采用星型单点连接,连接点尽量靠近芯片GND引脚。

- 驱动回路最小化:HO和LO走线短而粗,栅极电阻靠近MOS管。

- VCC与自举电容就近放置。

- QFN24封装散热:芯片底部的裸露焊盘(EP)必须良好焊接至PCB地平面,并尽可能通过过孔连接至内部或底层地平面以辅助散热。

MOS管选型建议:

- 选择耐压 ≥ 400V的MOS管。

- 其栅极电荷(Qg)应与0.8A/1.2A的驱动能力匹配,确保开关速度满足系统频率要求。

五、典型应用场景

三相直流无刷电机(BLDC)驱动器:

- 用于变频器、电动工具、风机、水泵、轻型电动车控制器等,其标准逻辑简化了与各种MCU或驱动算法的适配。

三相永磁同步电机(PMSM)驱动器:

- 适用于对控制接口简易性有要求的伺服驱动场合。

其他需要三路半桥驱动的功率转换系统。

六、调试与故障处理

常见问题与对策:

-

芯片无输出:

检查VCC电压是否高于4.3V(开启阈值)。

检查所有HIN和LIN信号是否符合标准逻辑(高电平开启)。由于其逻辑简单,此处出错概率低。

-

某一相高端输出(HO)不工作:

测量该相VB-VS电压,确认是否高于4.1V(VB开启阈值)。

检查该相自举二极管和电容。

-

三相电流不平衡或电机抖动:

检查三路自举电容的容值是否一致,布局是否对称。

测量三路HO和LO的开关波形,对比延时和边沿是否一致。

-

芯片在重载下进入保护:

监测VCC电源在负载突变时是否跌落到4.2V(关断阈值)以下,优化电源路径和去耦。

检查VB电压在高占空比时是否充足。

-

QFN封装焊接不良:

检查芯片底部焊盘是否充分焊接,这可能导致散热不良或电气连接不可靠。

七、设计验证要点

逻辑与保护功能验证:

- 验证标准真值表功能,特别是"11"和"00"输入时的强制关断互锁功能。

- 测试VCC和VB的欠压保护功能:缓慢调节电压,观察输出在阈值点附近的动作。

动态性能与一致性测试:

- 测量三路输出的死区时间,确认其存在且一致(约100ns)。

- 在额定负载下,同时观测三路栅极驱动波形,检查其对称性(开通/关断延时、上升/下降时间)。

自举电路压力测试:

- 在最高工作频率、最大占空比条件下,长时间运行并监测三路VB-VS电压的稳定性。

热性能测试(尤其QFN封装):

- 在最高环境温度、满载条件下连续运行,使用热成像仪或热电偶测量芯片表面及PCB对应区域的温度,评估散热设计。

系统EMI预评估:

- 由于开关边沿较快(35ns/25ns),需关注驱动回路的振铃,并在必要时优化栅极电阻或布局。

八、总结

EG2124A 通过 "标准化同相输入逻辑" 和 "VCC/VB双路欠压保护" 两大核心改进,在EG2133的高集成度基础上,大幅提升了开发友好性与系统鲁棒性 。

其逻辑接口的简化使得软件适配几乎无门槛,而双重UVLO保护 则增强了在复杂电源环境下的可靠性。0.8A/1.2A的驱动能力与完全对称的开关时序 ,足以应对广泛的三相中功率驱动需求。

TSSOP20与QFN24的双封装选项 ,进一步拓宽了其应用场景。

选择EG2124A,意味着选择了一个易用、安全且封装灵活 的三相驱动核心。

成功应用的关键在于遵循稳健的功率电路布局原则,并充分利用其标准逻辑简化控制系统设计。

文档出处

本文基于屹晶微电子 EG2124A 芯片数据手册 V1.1 版本整理编写,并结合三相电机驱动设计实践。具体设计与元器件选型请务必以官方最新数据手册为准,在实际应用中建议重点验证其双路欠压保护功能及多通道驱动波形的一致性。