AU5615 是一款频率转换器、其主要完成多输出的时钟配置,可提供 12 路差分输出或 24 路单端输出。主要通过 I2C/SPI 串行接口实时配置,本次测试之中使用I2C进行调试。

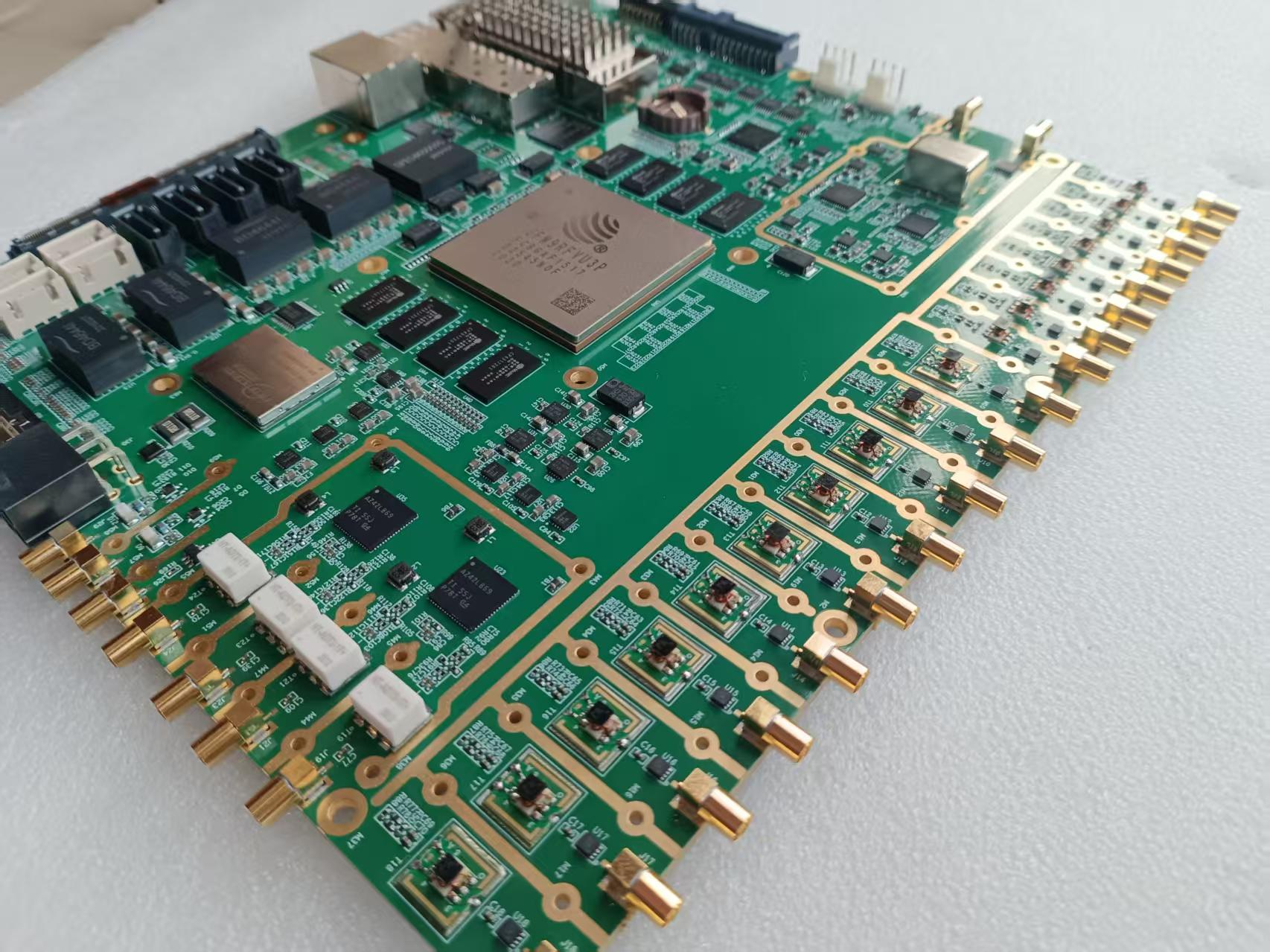

硬件使用UD LAN-407平台。LAN-407采用复旦微的RFSOC(VU3P)+华为310P(AI模块)。

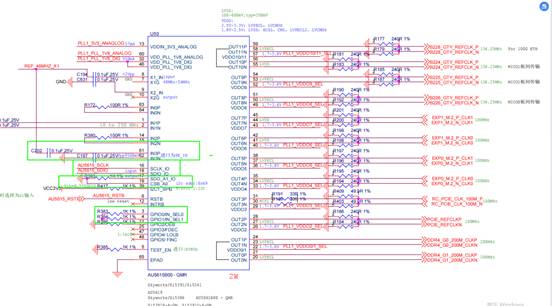

原理图

调试时,需要先保证输入电源的可靠性,用万用表进行测量后使用,调试过程之中FPGA端需要关注的信号为I2C串口信号和AU5615的复位信号。

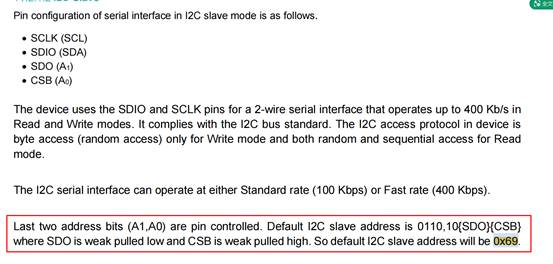

IIC设备的地址说明

AU5615的地址高4bit为0110,低4bit为10{SDO}{CSB},需要根据实际的硬件连线来确定。

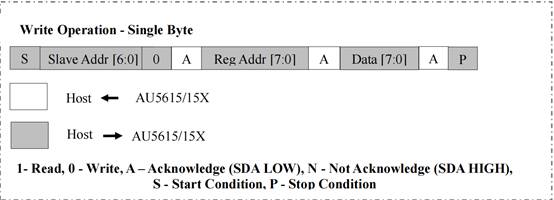

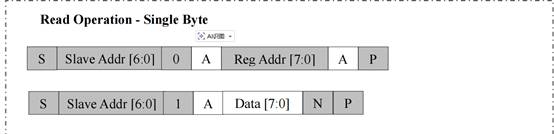

IIC的时序

对于I2C设备的读写时序,FPGA侧需要关注的是ack有无及时相应,一般而言,只要能够正确相应ack,即I2C能够正确进行通信,这个调试就完成一多半了。

写时序

读时序

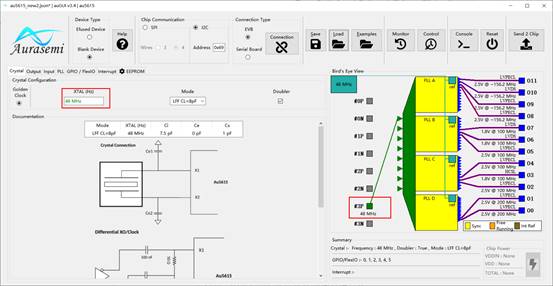

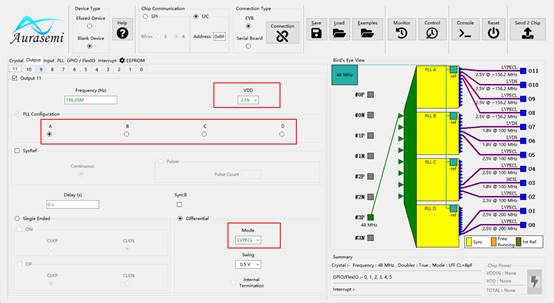

时钟配置

AU5615需要使用时钟配置软件进行配置时钟,最终输出相应的寄存器值。

配置

首页配置对应的时钟,需要与原理图保持一致。

配置输出差分时钟需要选择4个PLL之中的1个。以及对应的VDD和mode需要与原理图一致。

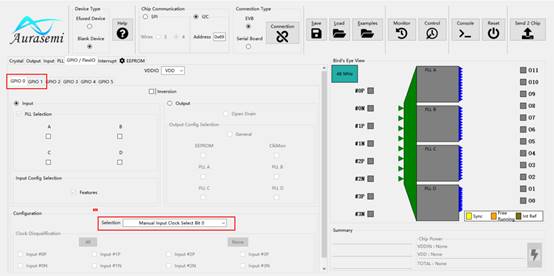

针对GPIO进行配置时,根据硬件的连线确定GPIO功能,这里需要格外注意GPIO0和GPIO1的配置,需要与实际的硬件原理图保持一致。

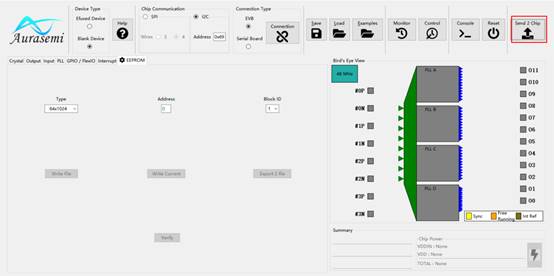

配置导出

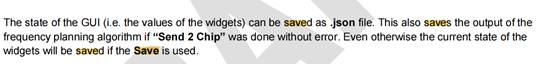

导出时先保存json文件,在点击send2chip,然后再点击save,才能导出相应的csv文件。

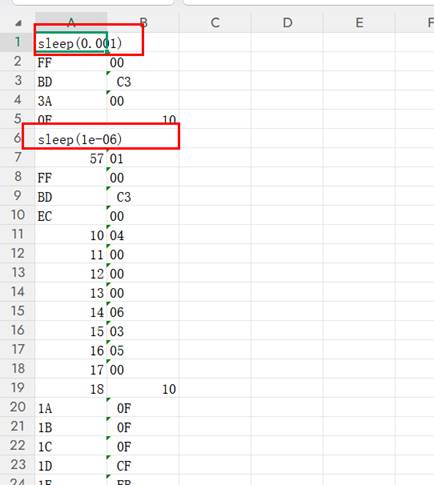

导出的csv包含sleep部分,代表着延时等待。在执行时需要延时对应的时间在发送下一个命令

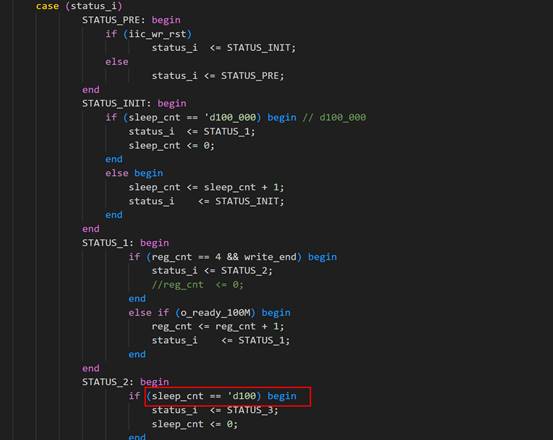

代码部分

FPGA代码部分的逻辑比较简单,就是1个状态机将配置的寄存器写入完成即可。在这个基础卷国家之中补充了可以用vio去控制读取的代码逻辑。

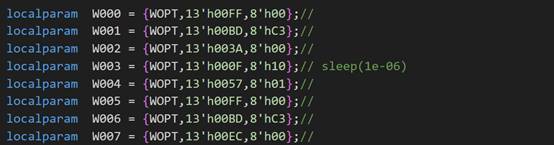

如下为配置的一部分寄存器,sleep需要等待指定的时间后发出下一个命令。

核心状态机的一部分,与上面的参数保持一致,主要功能就是在对应的寄存器处进行等待。