在FPGA和SoC设计中,UART(通用异步收发传输器)是最常用的串行通信接口之一。Xilinx提供的AXI UART Lite IP核是一个轻量级、可配置的UART控制器,它通过AXI4-Lite接口与系统总线连接,非常适合在嵌入式系统中添加简单的串行通信功能。本文将基于官方产品指南PG142(v2.0)对该IP核进行详细解析,帮助开发者快速理解其架构、寄存器、配置方法以及使用流程。

1. 概述

AXI UART Lite IP核用于实现UART协议与AXI4-Lite接口的桥接。它支持全双工通信,内置16Byte(字节)深度的发送FIFO和接收FIFO,可减少CPU干预。其特性包括:

-

AXI4-Lite接口:用于寄存器访问和数据传输。

-

可配置的数据位:5~8bit位。

-

可选的奇偶校验:无(No Parity)、奇校验(Odd)、偶校验(Even)。

-

可选波特率:通过内部波特率发生器(BRG)实现,在GUI界面进行选择。

-

中断支持:当接收FIFO非空或发送FIFO空时产生中断(可屏蔽)。

-

独立收发:发送和接收通道独立运行。

该IP核适用于需要UART通信但资源有限的场景,例如MicroBlaze软核处理器或Zynq处理器系统中的外设扩展。

2. IP核架构

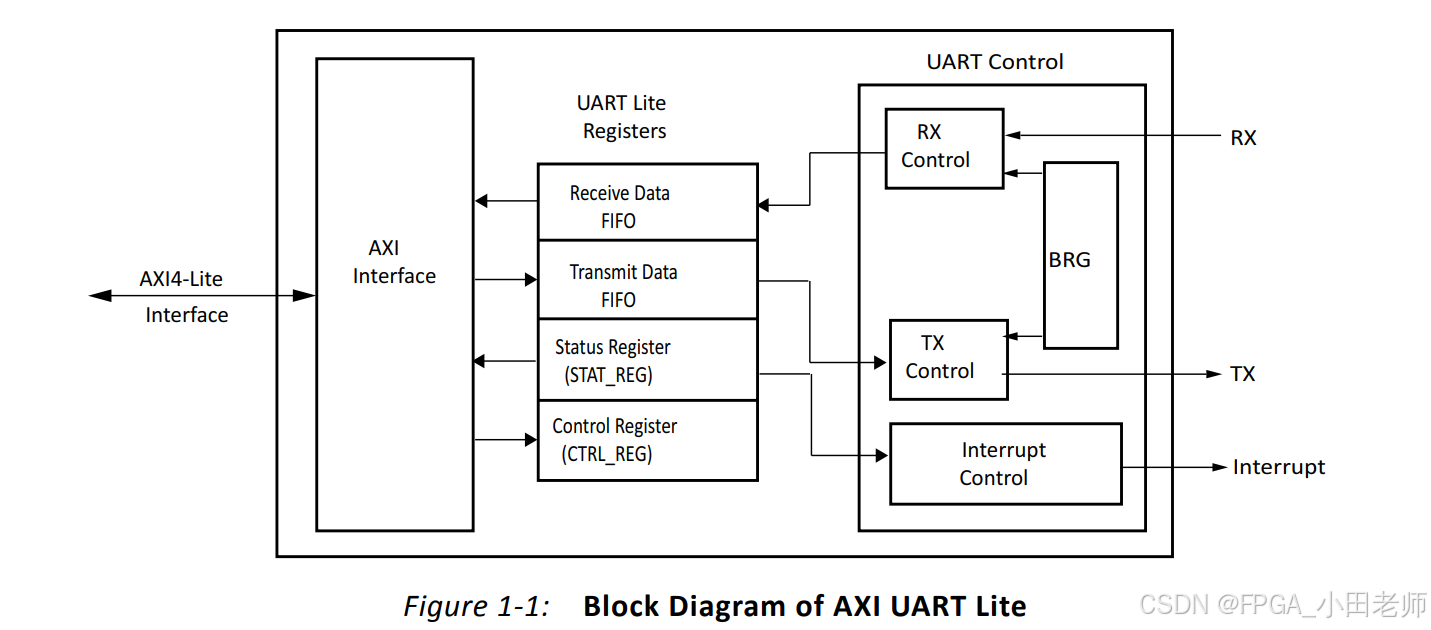

AXI UART Lite的内部结构如下图所示

主要包含以下模块:

-

AXI接口:实现AXI4-Lite从机(Slave)接口,负责与系统总线的通信,处理读写请求。

-

UART Lite寄存器:包含控制寄存器(CTRL_REG)、状态寄存器(STAT_REG)以及发送FIFO / 接收FIFO(各16字节)。

-

UART控制(UART Control):

-

Rx控制:以"配置的波特率"采样接收数据,并存入接收FIFO。

-

Tx控制:从发送FIFO中读取数据,通过UART_TX引脚串行发送。

-

波特率发生器(BRG):根据系统时钟和配置产生所需的波特率。

-

中断控制:管理中断使能和中断产生逻辑。

-

3. 端口信号

IP核的I/O信号分为三类:

| 信号名 | 方向 | 描述 |

|---|---|---|

| 系统信号 | ||

| s_axi_aclk | 输入 | AXI时钟 |

| s_axi_aresetn | 输入 | 异步复位,低有效 |

| interrupt | 输出 | 中断输出,上升沿 |

| AXI4_lite通道信号 | 参考AXI4Lite协议,包括读写地址、数据、响应等 | |

| UART接口信号 | ||

| rx | 输入 | 串行接收数据 |

| tx | 输出 | 串行发送数据(复位后为1) |

AXI4Lite相关信号的具体定义参考【FPGA数据总线】详解AXI4-LITE总线。

4. 寄存器空间

IP核通过四个32位寄存器进行控制,地址偏移如下:

| 地址偏移 | 寄存器名 | 描述 |

|---|---|---|

| 0x00 | Rx FIFO | 接收数据FIFO(只读) |

| 0x04 | Tx FIFO | 发送数据FIFO(只写) |

| 0x08 | STAT_REG | 状态寄存器(只读) |

| 0x0C | CTRL_REG | 控制寄存器(只写) |

4.1 接收FIFO (Rx FIFO)

-

深度:16字节(Byte)

-

访问:只读

-

读取"空FIFO"会导致SLVERR总线错误

-

数据位宽可配置(5~8位)

4.2 发送FIFO (Tx FIFO)

-

深度:16字节(Byte)

-

访问:只写

-

写满FIFO会产生SLVERR,数据不会写入

-

数据位宽可配置

4.3 控制寄存器 (CTRL_REG) [地址0x0C]

| 位 | 名称 | 访问 | 复位值 | 描述 |

|---|---|---|---|---|

| 4 | Enable Intr | 写 | 0 | 中断使能:1=使能,0=禁止 |

| 1 | Rst Rx FIFO | 写 | 0 | 写1清除接收FIFO |

| 0 | Rst Tx FIFO | 写 | 0 | 写1清除发送FIFO |

| 其他位 | Reserved | - | 0 | 保留 |

4.4 状态寄存器 (STAT_REG) [地址0x08]

| 位 | 名称 | 访问 | 描述 |

|---|---|---|---|

| 7 | Parity Error | 读 | 奇偶错误指示(读后清零) |

| 6 | Frame Error | 读 | 帧错误指示(停止位为0,读后清零) |

| 5 | Overrun Error | 读 | 溢出错误(接收新数据但FIFO满,读后清零) |

| 4 | Intr Enabled | 读 | 当前中断使能状态 |

| 3 | Tx FIFO Full | 读 | 发送FIFO满标志 |

| 2 | Tx FIFO Empty | 读 | 发送FIFO空标志 |

| 1 | Rx FIFO Full | 读 | 接收FIFO满标志 |

| 0 | Rx FIFO Valid Data | 读 | 接收FIFO有数据(非空) |

5. 配置参数

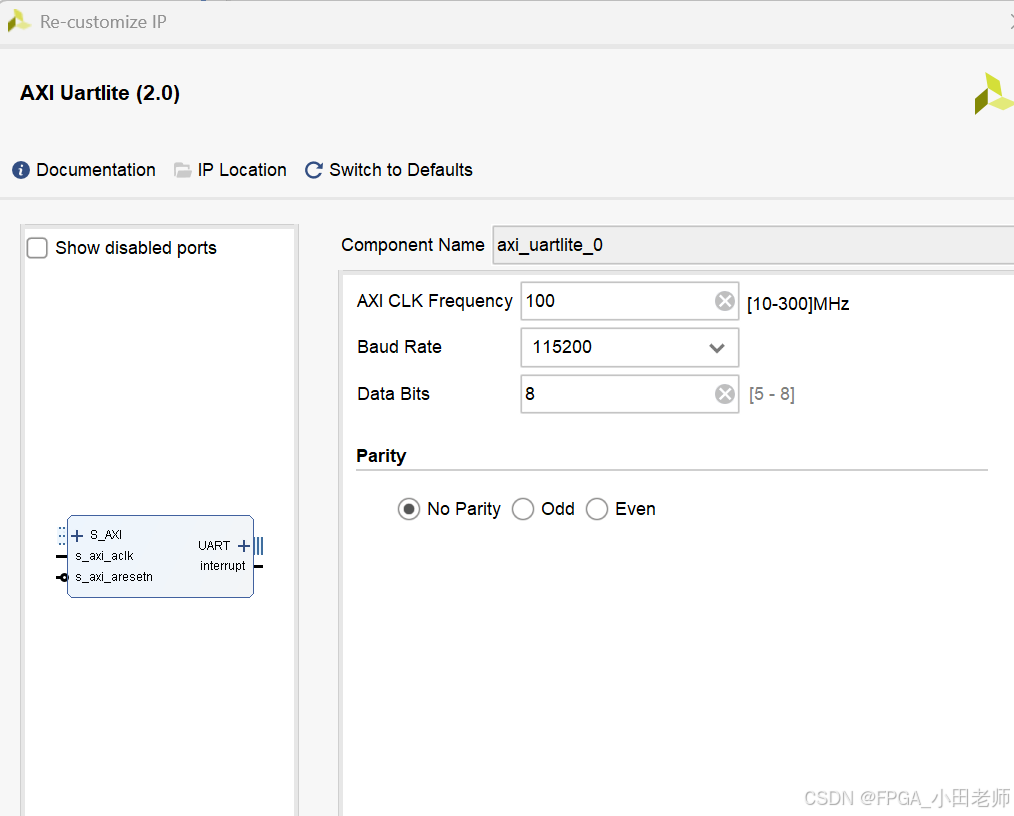

在Vivado中定制IP时,可以设置以下参数:

-

AXI CLK Frequency:系统时钟频率(MHz),用于波特率计算。

-

Baud Rate:目标波特率,支持以下常用值(单位bps):110, 120, 300, 4800, 9600, 14400, 19200, 38400, 57600, 115200, 128000, 230400, 460800, 921600。GUI会自动检查时钟频率的容差,只允许设置有效的波特率。

-

Data Bits:数据位,可选5、6、7、8。

-

Parity:奇偶校验模式:None、Odd(奇)、Even(偶)。

6. 时钟与复位

-

时钟 :所有操作同步于

s_axi_aclk。 -

复位 :

s_axi_aresetn为低有效同步复位,复位后所有寄存器恢复默认值,FIFO被清空。

7. 编程序列

典型使用流程如下:

-

初始化:根据需要,向CTRL_REG写入适当的值,例如使能中断、清除FIFO。

-

发送数据:向Tx FIFO写入待发送字节(注意FIFO满标志)。

-

接收数据:轮询STAT_REG的Rx FIFO Valid Data位,当该位为1时从Rx FIFO读取数据。

-

中断处理:如果使能了中断,当中断触发时,读取STAT_REG确定中断来源(接收数据可用或发送FIFO空),然后进行相应处理。

具体的使用方式见下一篇:AXI_UARTLite IP核仿真(待更新)。

总结

AXI UART Lite IP核是一个简单易用、资源占用少的UART控制器,非常适合在Xilinx FPGA或Zynq SoC中快速添加串行通信功能。通过AXI4-Lite接口,它可以轻松集成到处理器系统中,并且提供了灵活的配置选项以满足不同应用需求。无论是作为调试接口,还是与外部设备通信,AXI UART Lite都是一个可靠的选择。