第1篇:初识FPGA的"身世"与"骨架"------FPGA内部结构总览

写在前面的话

欢迎来到《FPGA内部模块详解》系列的第一篇文章。在开始这段探索之旅前,让我们先思考一个问题:为什么FPGA能够在40多年的历史中长盛不衰,甚至在AI时代焕发新生?

1985年,当Xilinx(现为AMD一部分)的联合创始人Ross Freeman发明全球首款商用FPGA------XC2064时,他一定预见到这项技术将改变半导体产业的格局。从最初的85,000个晶体管、64个逻辑块,到今天拥有1380亿个晶体管、千万级逻辑单元的Versal系列,FPGA始终站在技术创新的前沿。

本文将作为整个系列的地图,带你俯瞰FPGA的"身世"与"骨架",为后续深入每个核心模块打下基础。

一、FPGA是什么?------从"门电路"到"可编程逻辑"

1.1 一个简单的思想实验

想象一下,如果你有无穷无尽的最基本逻辑门(与门、或门、非门),还有一把神奇的烙铁,可以瞬间将它们连接成任何你能想象到的电路------加法器、计数器、甚至一个简单的CPU。你会怎么做?这正是FPGA架构所要回答的基本问题。

FPGA 的全称是 现场可编程门阵列 (Field Programmable Gate Array)。顾名思义,它是一种可以通过软件手段更改、配置器件内部连接结构和逻辑单元,完成既定设计功能的数字集成电路。

1.2 FPGA的"乐高"哲学

把FPGA想象成一盒高品质的乐高积木。你可以按照图纸搭建一个城堡,玩腻了可以拆掉,重新搭成一艘宇宙飞船。这就是FPGA最迷人的地方------ 硬件级的软件化灵活调整 。

与ASIC(专用集成电路)的"一次定型,终身不变"不同,FPGA允许工程师在芯片设计中途、甚至在产品制造完成后,依然可以重新定义芯片功能来执行不同任务。这种灵活性加快了产品上市速度,也催生了"无晶圆厂"商业模式------企业无需拥有晶圆厂,只需具备愿景、设计能力与FPGA,即可打造突破性硬件。

二、FPGA的技术演进:从"胶合逻辑"到"AI加速器"

要理解今天的FPGA为何如此强大,有必要简单回顾它的发展历程:

| 阶段 | 时间 | 核心特征 | 典型应用 |

|---|---|---|---|

| FPGA 1.0 | 1980s-1990s | 胶合逻辑单元 | 连接不同逻辑器件、可编程I/O |

| FPGA 2.0 | 1990s-2017 | 连接浪潮 | 网络接口、存储接口、复杂功能集成 |

| FPGA 3.0 | 2017至今 | 数据加速 | AI推理、数据中心加速、异构计算 |

关键的里程碑事件包括:

- 1990年代:首次将嵌入式RAM和DSP集成到FPGA中

- 2001年:首款集成SerDes(高速串行收发器)的FPGA问世

- 2011年:采用2.5D CoWoS封装的Virtex-7 2000T开创了先进封装技术

- 2012年:Zynq系列将Arm处理器与可编程逻辑整合,开启SoC FPGA时代

- 2019年:Versal系列引入AI引擎和可编程片上网络(NoC)

今天的FPGA已经从单纯的"可编程逻辑"进化为"异构计算平台",在AI从云端走向边缘的浪潮中,扮演着GPU与CPU之间不可或缺的角色。

三、FPGA的"骨架":六大核心组成部分

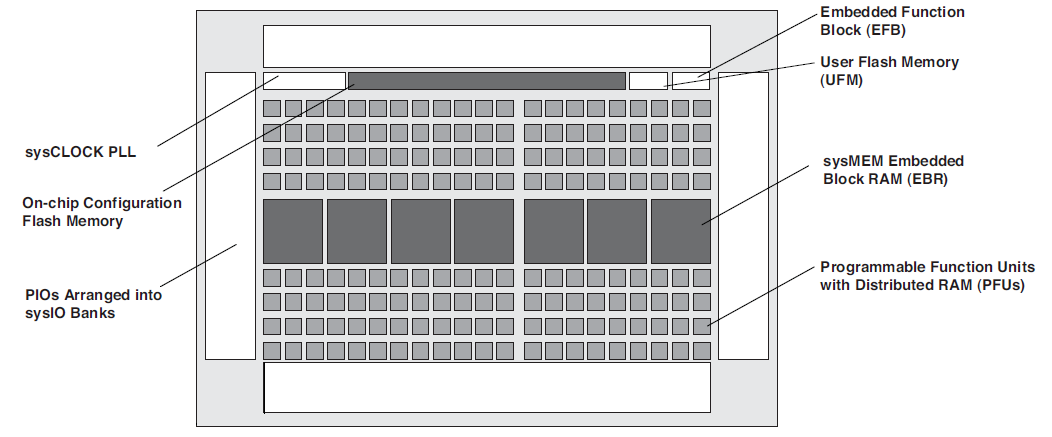

让我们把FPGA芯片放在显微镜下,解剖它的内部结构。一个典型的现代FPGA主要由以下六大模块构成:

3.1 可编程输入输出单元(IOB)

IOB是FPGA与外部世界通信的桥梁。为了适应多种电气标准,FPGA的I/O被划分为若干个独立的 Bank 。每个Bank有自己的供电电压(VCCIO),可以独立支持不同的I/O标准(如LVCMOS、LVDS、SSTL等)。

3.2 基本可编程逻辑单元(CLB/PFU)

这是FPGA的"逻辑心脏"。CLB由查找表(LUT)、触发器(FF)、进位链和多路选择器等组成。

LUT的本质 :LUT实际上是一个小型RAM。以6输入LUT为例,它可以实现2^64种可能的函数中的任何一种------这个数字之大,甚至超过了银河系中原子的估算数量。通过将逻辑函数的真值表预先写入LUT,输入信号相当于地址,查表输出就是逻辑运算结果。

3.3 嵌入式块内存(BRAM)

BRAM是FPGA中专用的存储资源,可以配置为单端口RAM、双端口RAM、FIFO、ROM等常用存储结构。每个BRAM块通常为18Kb或36Kb,可以级联成更大容量的存储器。

3.4 数字信号处理单元(DSP Slice)

DSP Slice是FPGA的"算力引擎",通常包含乘法器、加法器/累加器和流水线寄存器。它们能够高效实现乘加运算(如FIR滤波器、FFT),是FPGA在信号处理和AI加速领域的核心武器。

3.5 时钟管理模块(DCM/PLL/MMCM)

时钟网络是FPGA的"心跳"。时钟管理模块负责:

- 频率合成 :倍频/分频产生所需时钟

- 相位调整 :消除时钟偏斜(Clock Skew)

- 抖动滤除 :提高时钟质量

3.6 丰富的布线资源(Interconnect)

布线资源是FPGA的"神经网络",连通所有内部单元。根据长度和用途,可分为:

- 全局布线 :用于时钟、复位等全局信号

- 长线资源 :Bank间高速信号

- 短线资源 :基本逻辑单元间的互连

- 分布式布线 :专用控制信号

补充说明 :除了上述六大部分,现代FPGA还包含两类重要资源------ 内嵌底层功能单元 (如软核处理器)和 内嵌专用硬核 (如PCIe硬核、SerDes、ARM硬核处理器)。这些将在后续的Hard IP章节详细介绍。

四、FPGA的核心价值:为什么需要它?

4.1 FPGA vs. CPU vs. GPU

| 维度 | CPU | GPU | FPGA |

|---|---|---|---|

| 计算模型 | 顺序执行(冯诺依曼) | 并行执行(SIMD) | 空间计算(定制硬件) |

| 灵活性 | 软件可编程 | 软件可编程 | 硬件可重构 |

| 并行性 | 有限 | 高(数据并行) | 极高(流水线+数据并行) |

| 延迟 | 高(指令开销) | 较高 | 极低(硬件直通) |

| 适用场景 | 控制密集型 | 计算密集型(规整) | 流式计算、不规则并行 |

4.2 FPGA vs. ASIC

ASIC就像一座精心雕刻的雕塑------完成后很难改变;FPGA则像橡皮泥,可以反复重塑。两者的核心差异在于:

- ASIC的优势 :性能极致、功耗最优、大规模量产成本低

- FPGA的优势 :无需流片成本、可现场修改、上市时间快、适应小批量定制需求

4.3 FPGA的不可替代性

FPGA的可重构性解决了"硬件刚性"与"需求动态性"的根本矛盾:

- 缩短开发周期 :芯片设计公司用FPGA做原型验证,避免流片失败的风险

- 降低成本 :小批量、多品种的应用(军工、工业控制)无需承担高昂流片费

- 延长硬件生命周期 :通信基站可通过远程加载新配置,支持协议升级

- 分时复用 :同一硬件在不同时间实现不同功能

五、FPGA设计开发流程简介

了解完FPGA的内部结构,我们简单过一下FPGA的开发流程,这有助于理解后续各模块在实际项目中的角色:

- 功能定义/器件选型 :根据系统需求选择合适的FPGA型号(资源规模、速度等级、封装)

- 设计输入 :使用Verilog/VHDL等硬件描述语言描述电路

- 功能仿真 :验证逻辑功能的正确性

- 逻辑综合 :将HDL代码映射到LUT、FF等基本单元

- 布局布线 :将综合后的网表布局到芯片上,并用布线资源连接

- 编程调试 :生成比特流文件,下载到FPGA,上板验证

在整个流程中,约束文件起着至关重要的作用------它告诉工具时钟频率、引脚位置、I/O标准等信息,是连接设计与芯片的"说明书"。

六、本系列预告:接下来我们将深入哪些模块?

通过今天的"总览",你已经了解了FPGA的整体骨架。在接下来的文章中,我们将逐一深入每个模块,揭开它们的神秘面纱。

七、本章小结

今天我们完成了FPGA世界的首次巡礼:

- 了解了FPGA的起源 :从1985年的XC2064到今天的异构计算平台

- 认识了FPGA的六大核心模块 :IOB、CLB、BRAM、DSP、时钟管理、布线资源

- 理解了FPGA的独特价值 :可重构性带来的灵活性、并行性、快速上市优势

- 预览了FPGA的开发流程 :为后续学习打下基础

正如一位工程师所说:"人生只有一次,FPGA却可以重写。"这种可重写的特性,正是FPGA永恒魅力的源泉。

思考题 :如果让你用FPGA实现一个简单的计数器,你会用到今天介绍的哪些模块?它们各自承担什么角色?