按字母顺序排列的一类对象列表

BD_ADDR_SEG

描述

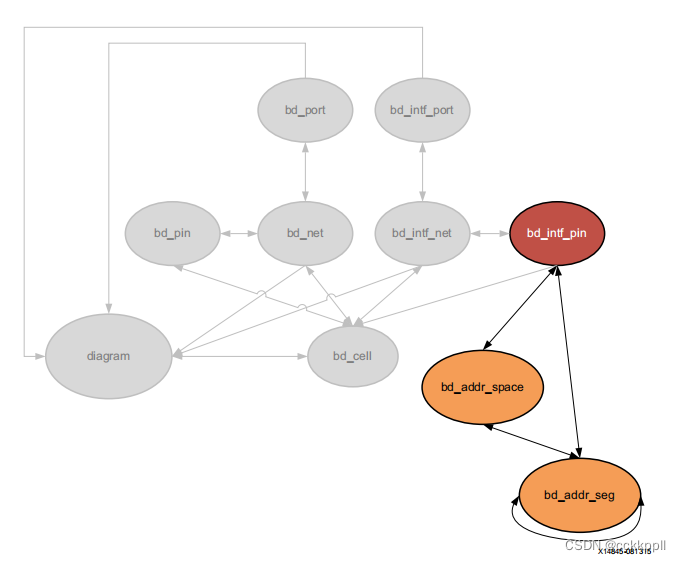

地址段或bd_addr_seg对象描述一个范围的位置和大小记忆力它们有一个范围(大小)和一个可选的起始偏移。对于各种内存映射的主接口和从接口,IP集成商遵循行业用于捕获存储器要求和能力的标准IP-XACT数据格式端点主控和从控。可寻址从属接口引用一个地址段容器,称为内存地图这些内存映射通常以从接口引脚命名,例如S_AXI,尽管这不是必需的。内存映射包含从属地址段。这些地址段对应于所述从接口的地址解码窗口参考所述存储器映射。什么时候在内存映射中指定,从属段必须有一个范围,并且可以有硬偏移,(指示从设备只能映射到位于的主地址空间其偏移或孔径)。例如,一个典型的AXI4Lite从接口引用的内存映射只有一个地址段,表示存储器的范围。然而,有些奴隶,就像一座桥,会具有多个地址段;或者每个地址解码窗口的地址范围。使用将从地址段分配到主地址空间assign_bd_address或create_bd_addr_seg命令。寻址主接口引用一个称为address的地址段容器空格或bd_addr_Space。地址空间由上的接口引脚bd_intf_pin引用

细胞。在外部AXI主机的情况下,地址空间由外部引用接口端口,bd_intf_port。不同协议的几个接口可以引用相同的主地址空间。例如,Microblaze处理器的数据地址空间是由其DLMB、M_AXI_DP和M_AXI_DC接口引用。地址空间包含主地址段。这些主地址段参考已经被分配到主地址空间中的从地址段,以及主设备访问它的偏移量和范围。

相关对象

bd_addr_seg对象同时引用主地址段和从地址段。这个bd_addr_space对象同时引用内存映射和主地址空间。您可以查询所有相关地址空间和地址段之间的关系。

例如

Get the slave address segments of a memory map space.

get_bd_addr_segs -of_objects [get_bd_addr_spaces /mdm_1/S_AXI]

Get the master address segments of amaster address space.

get_bd_addr_segs -of_objects [get_bd_addr_spaces /Microblaze_0/Data]

Get the slave adress segment from its referenced master address segment, or the

master address segment from its referencing slave address segment.

get_bd_addr_segs -of_objects [get_bd_addr_segs <slave or master>_segment]

Get the addr_segs referencing/referenced by interfaces.

Get all Master or slave interfaces.

set vMB [get_bd_intf_pins -of_objects [get_bd_cells *] -filter {Mode == "Master"}]

set vSB [get_bd_intf_pins -of_objects [get_bd_cells *] -filter {Mode == "Slave"}]

Get master segments

set vMS [get_bd_addr_segs -of_objects $vMB]

Get slave segments

set vSS [get_bd_addr_segs -of_objects $vSB]

属性

块设计地址段对象bd_addr_seg的属性包括以下,具有示例值:

Property Type Read-only Visible Value

ACCESS string false true read-write

CLASS string true true bd_addr_seg

EXEIMG string false true

MEMTYPE string false true data

NAME string false true SEG_axi_gpio_0_Reg

OFFSET string false true 0x40000000

PATH string true true /microblaze_0/Data/SEG_axi_gpio_0_Reg

RANGE string false true 0x00010000

SECURE bool false true 0

USAGE string false true register

要报告bd_addr_seg对象的属性,可以复制并粘贴以下内容

命令输入Vivado Design Suite Tcl shell或Tcl控制台:

report_property -all [lindex [get_bd_addr_segs ] 0]