FPGA开发板:AX7020;Xilinx 公司的 Zynq7000 系列的芯片XC7Z020-2CLG400I,400引脚 FBGA 封装。

HARDWARE PLATFORM在2019以后的vivado中已经没有了。本期实际上已经与MATLAB无关,主要介绍通过VITIS等方法进行程序固化。

目录

ZYNQ是如何启动的?

对于ZYNQ来说,必须要有PS端的配合才能固化程序。

- ZYNQ的启动由ARM主导,在非JTAG模式下启动,处理器首先执行BootRom里的代码,包括一些最基本的驱动以及把FSBL(first stage boot loader)代码搬运到OCM(on-chip memory)中。

- 处理器开始执行FSBL代码,包括:初始化vivado工程中对ZYNQ核的配置;加载PL端bitstream;加载second stage bootloader到DDR(Double Data Rate双倍速率同步动态随机存储器);交给second stage bootloader。

- second stage bootloader(跑系统的情况下使用)。

生成FSBL文件

fsbl.elf在硬件平台工程中。zynq_fsbl是fsbl的BSP(板级支持包),包含了许多外设文件。在fsbl.debug中添加调试宏定义:

分别build硬件平台工程和APP工程,在APP工程中的debug文件夹中生成了对应的BOOT.bin。BOOT.bin是启动文件,可以放到SD卡启动,也可以烧写到QSPI Flash。

也可以点击APP工程右键选择Create Boot Image,在其中add之前生成的fsbl.elf和bitstream文件(本例没有)。

SD卡启动

将SD卡格式为FAT32格式,放入BOOT.bin,调整启动模式为SD卡启动,打开putty配置串口,板子上电启动:

QSPI启动:

开发板配有一篇256Mbit的QSPI FLASH芯片(W25Q256)。QSPI启动实际上是把程序烧写到FLASH芯片中。

Vitis烧写

在Vitis中选择Xilinx>Program Flash,配置如下:

将开发板的启动模式设为QSPI,再次启动,在putty里面看到:

vivado烧写

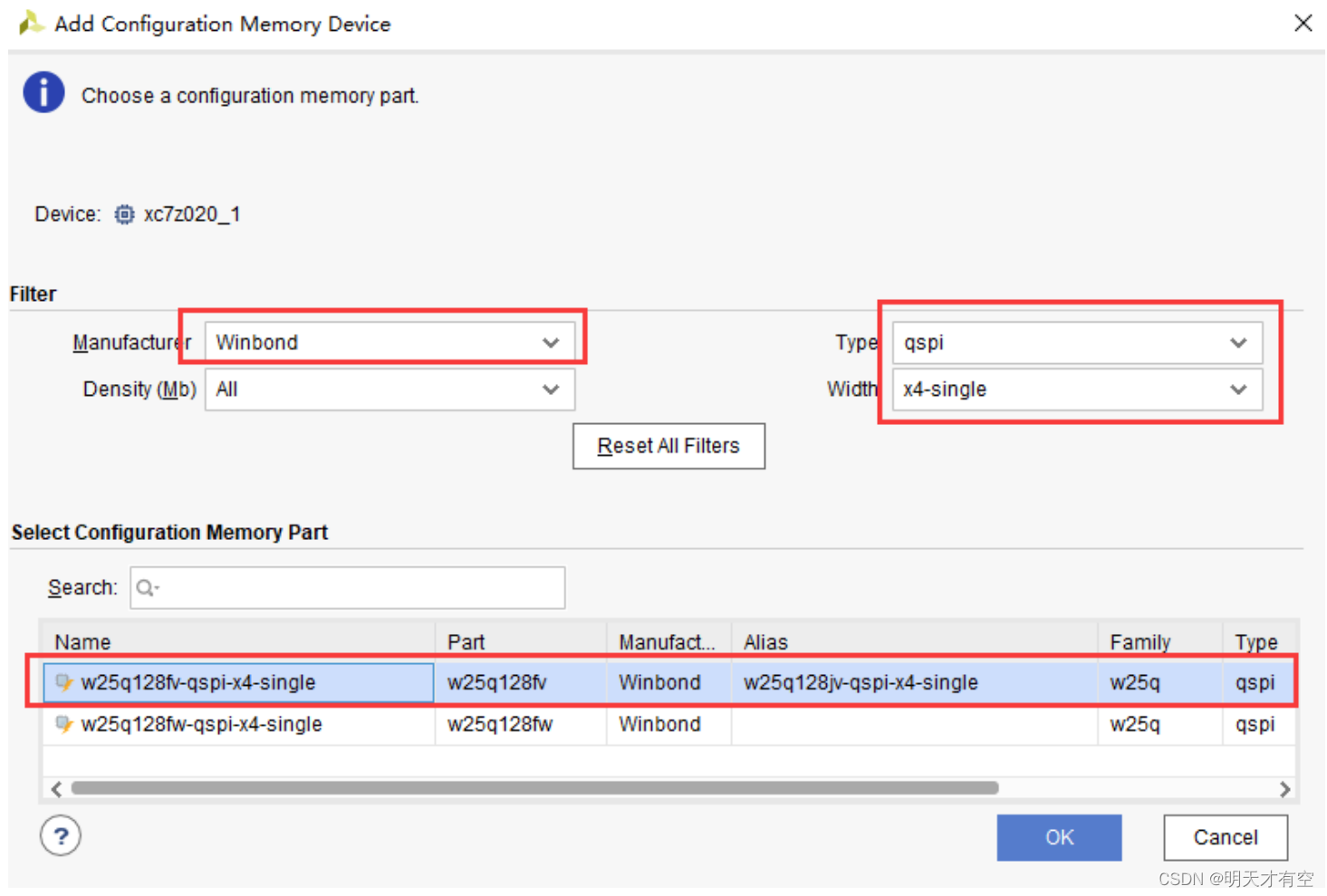

在HARDWARE MANGER右键 Add Configuration Memory Device,配置如下:

然后右键选择编译文件,选择要烧写的boot和fsbl文件,烧写时使用JTAG启动模式。

批处理文件快速烧写

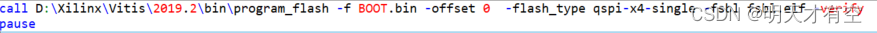

编写.bat文件如下:

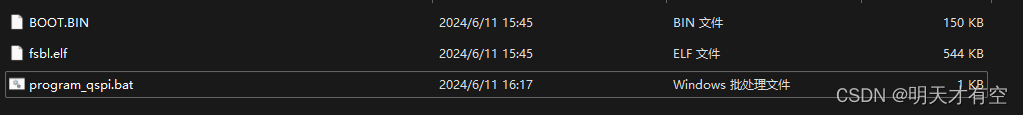

路径对应的是vitis的安装路径,把要烧录的文件放在一起:

插上JTAG线后双击bat文件即可烧写。