Allegro光绘Gerber文件、IPC网表、坐标文件、装配PDF文件导出打包

- 一、Gerber文件层叠与参数设置

- 二、装配图文件设置导出

- 三、光绘参数设置

- 四、Gerber孔符图、钻孔表及钻孔文件输出

- 五、输出Gerber文件

- 六、输出IPC网表

- 七、导出坐标文件

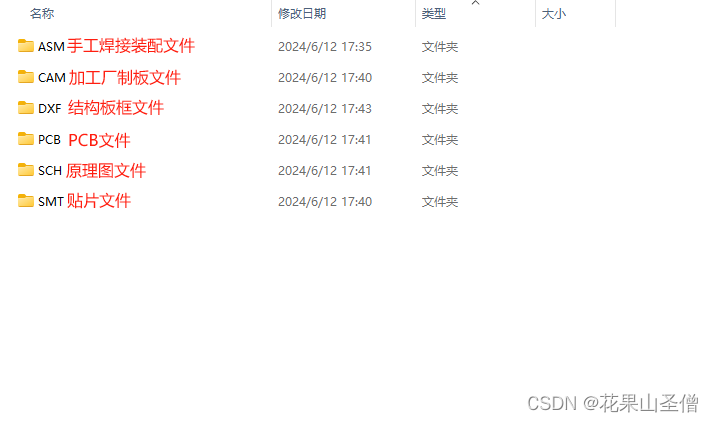

- 八、文件打包

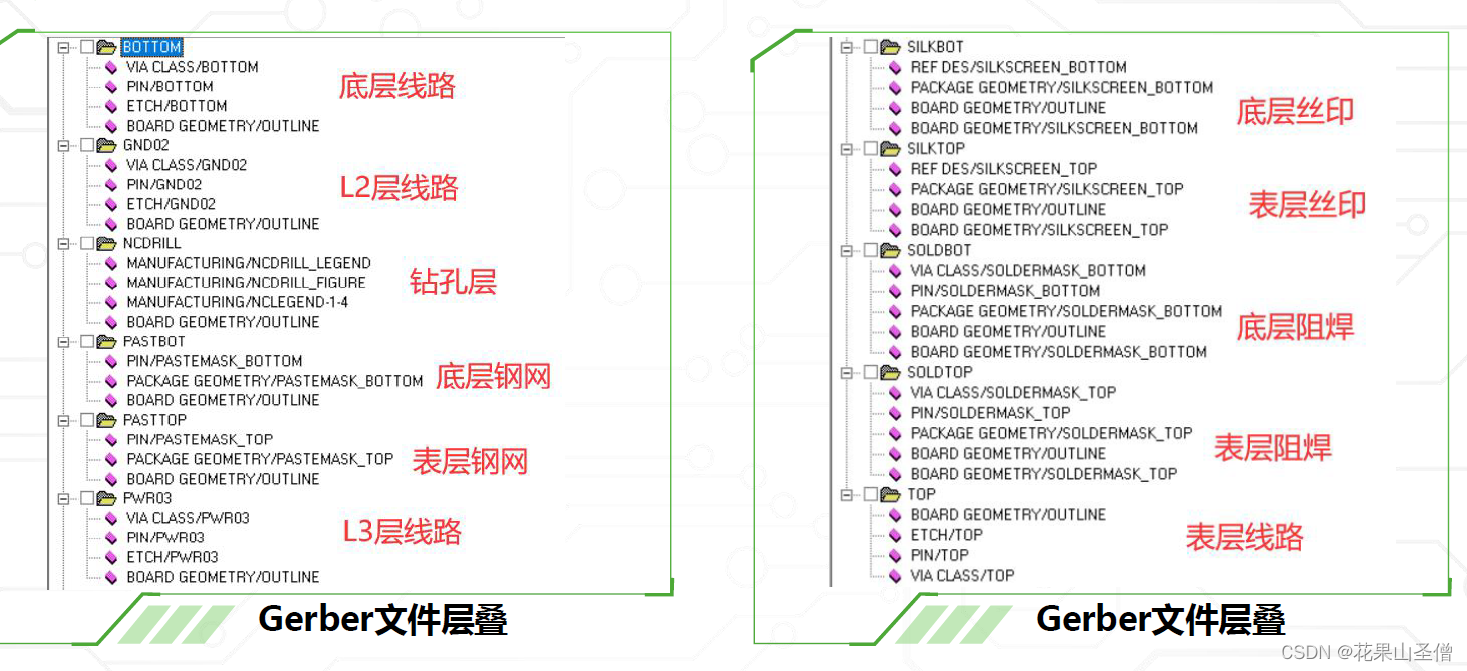

一、Gerber文件层叠与参数设置

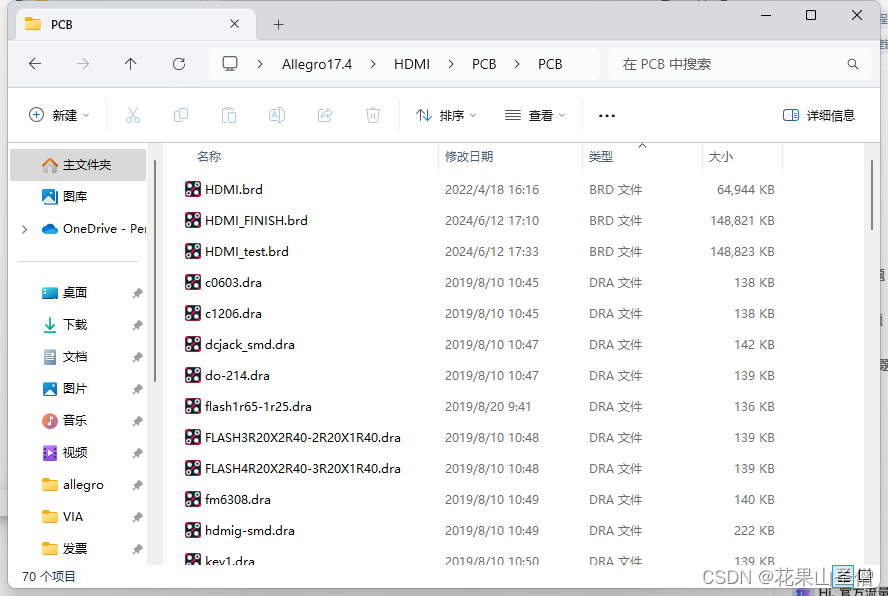

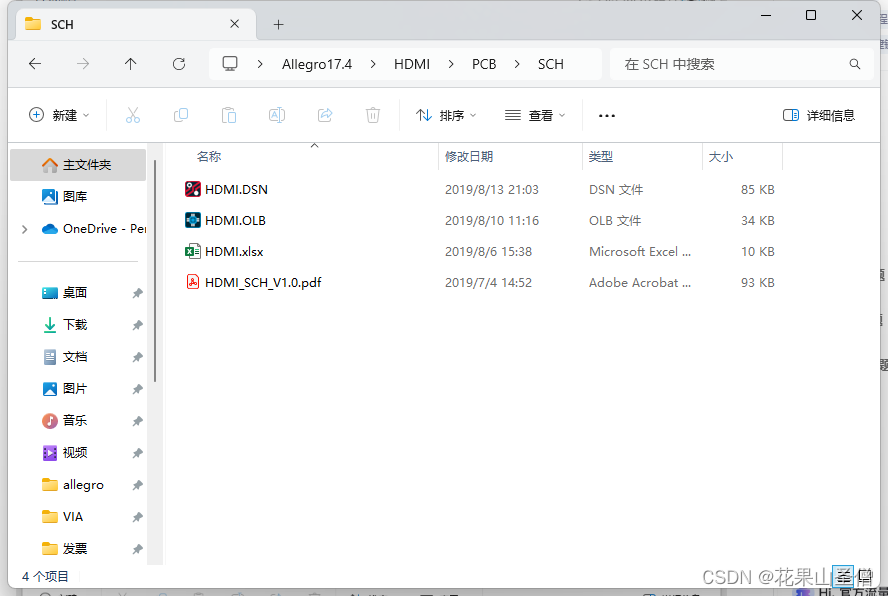

一般要的层叠信息文件如下图所示

那么具体怎么操作呢,请看下文

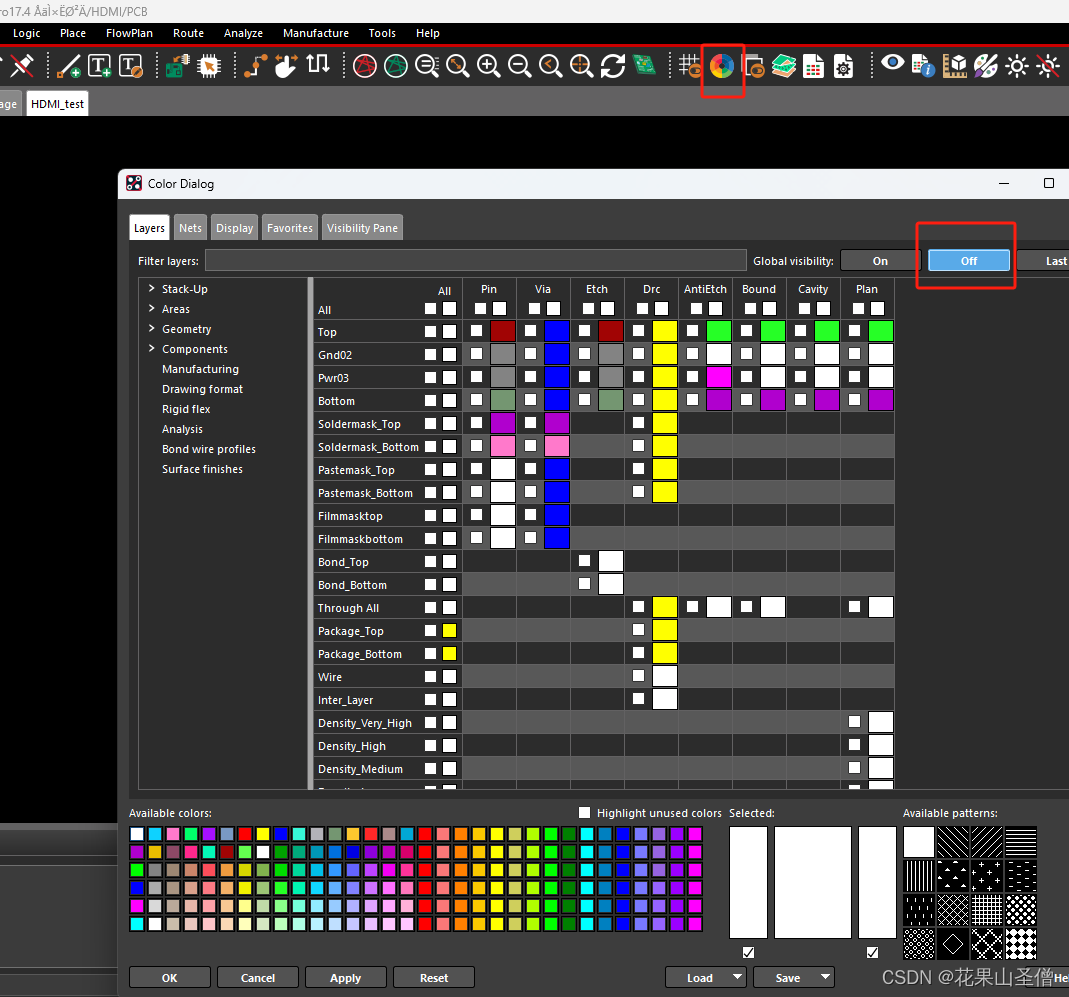

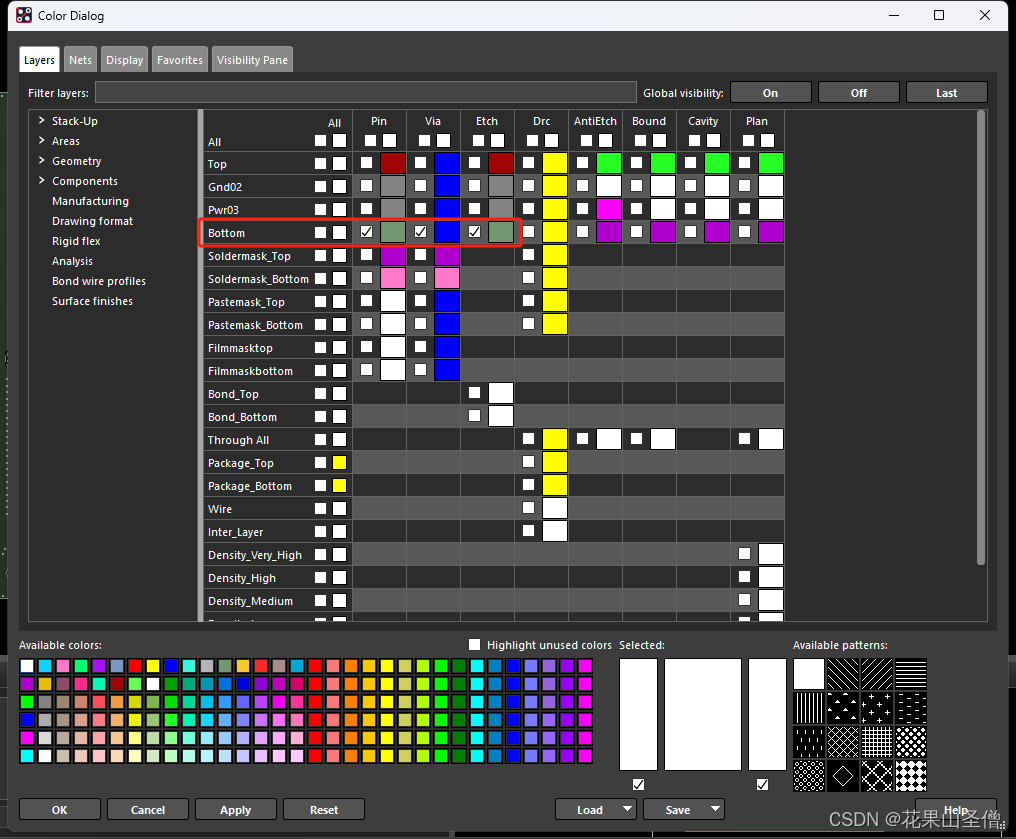

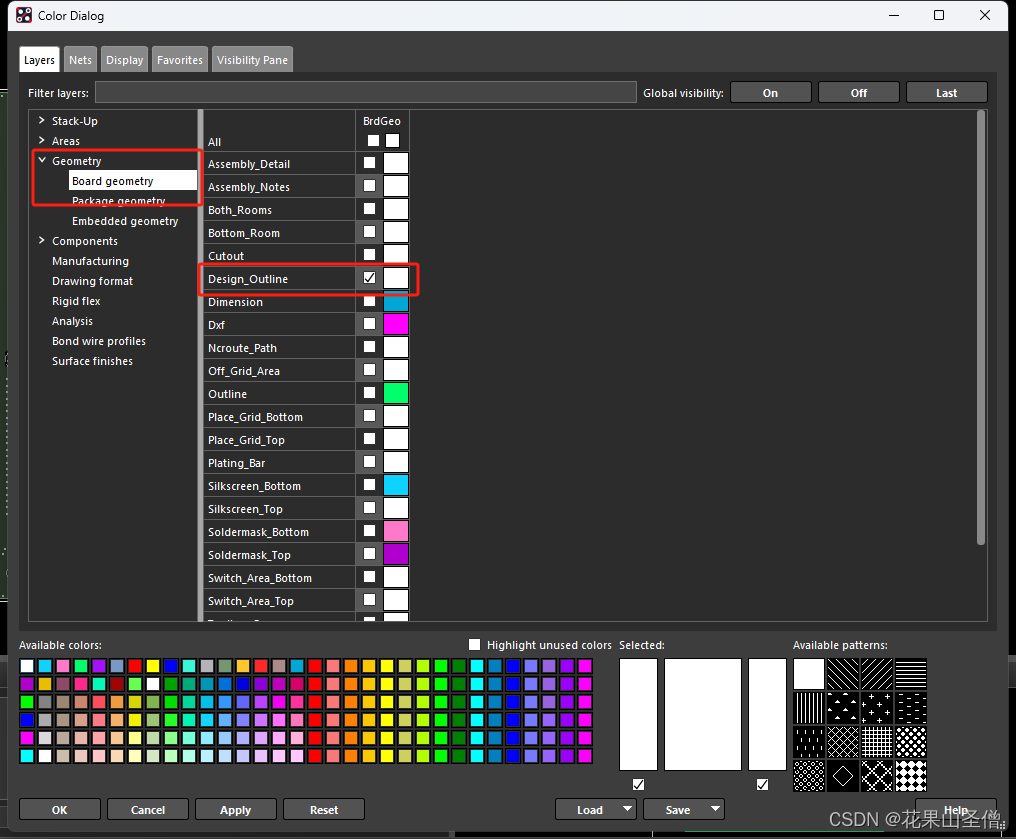

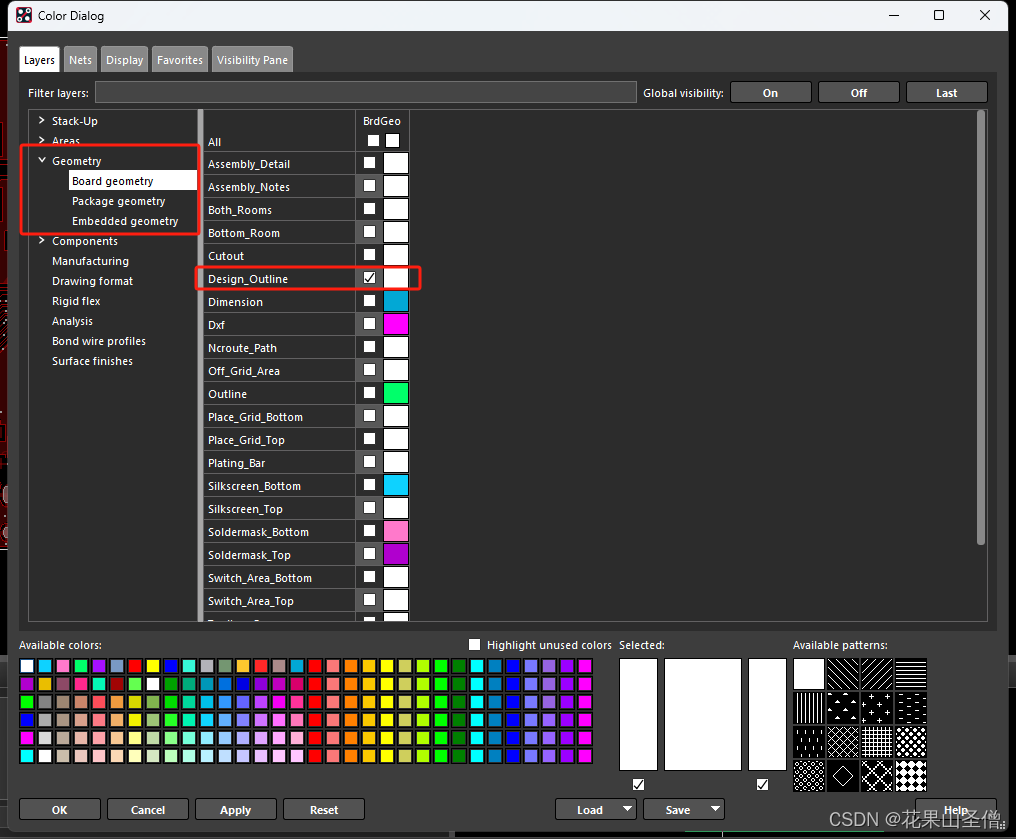

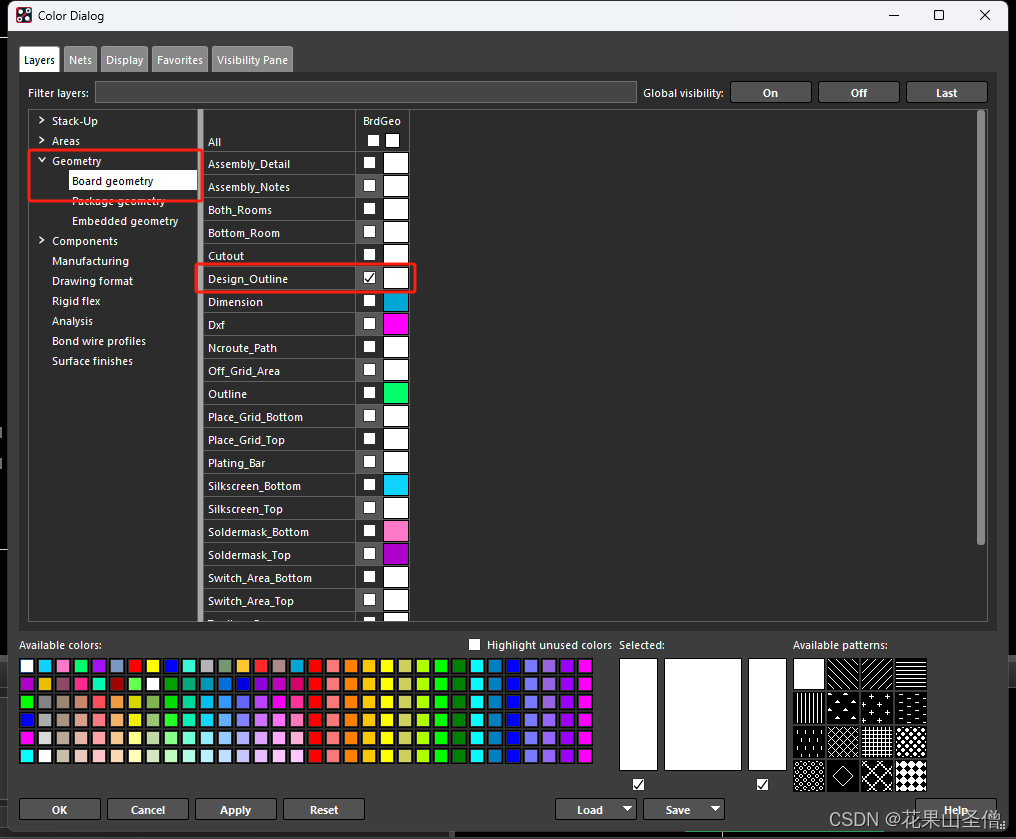

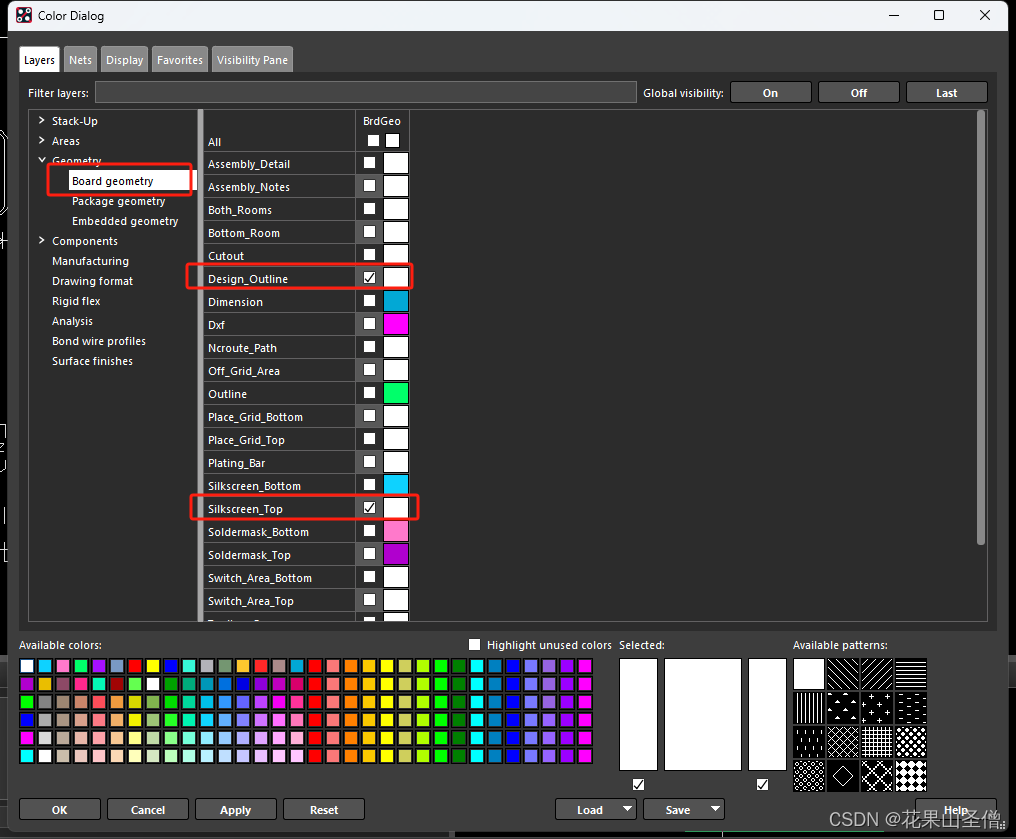

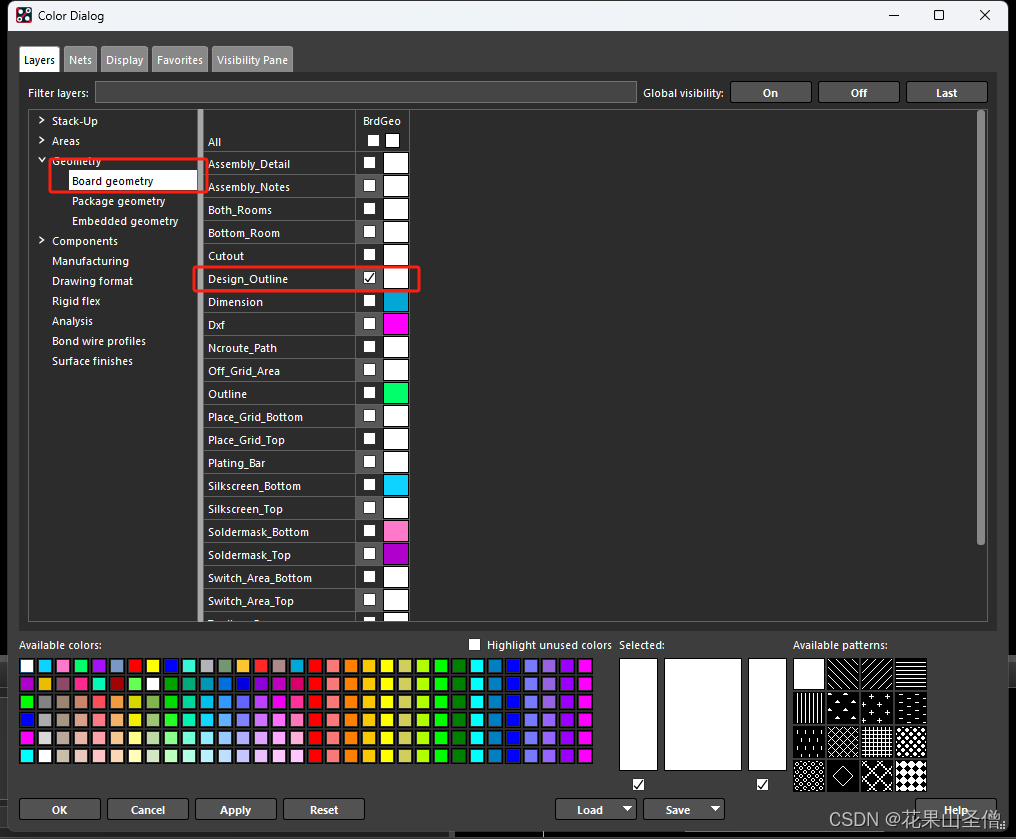

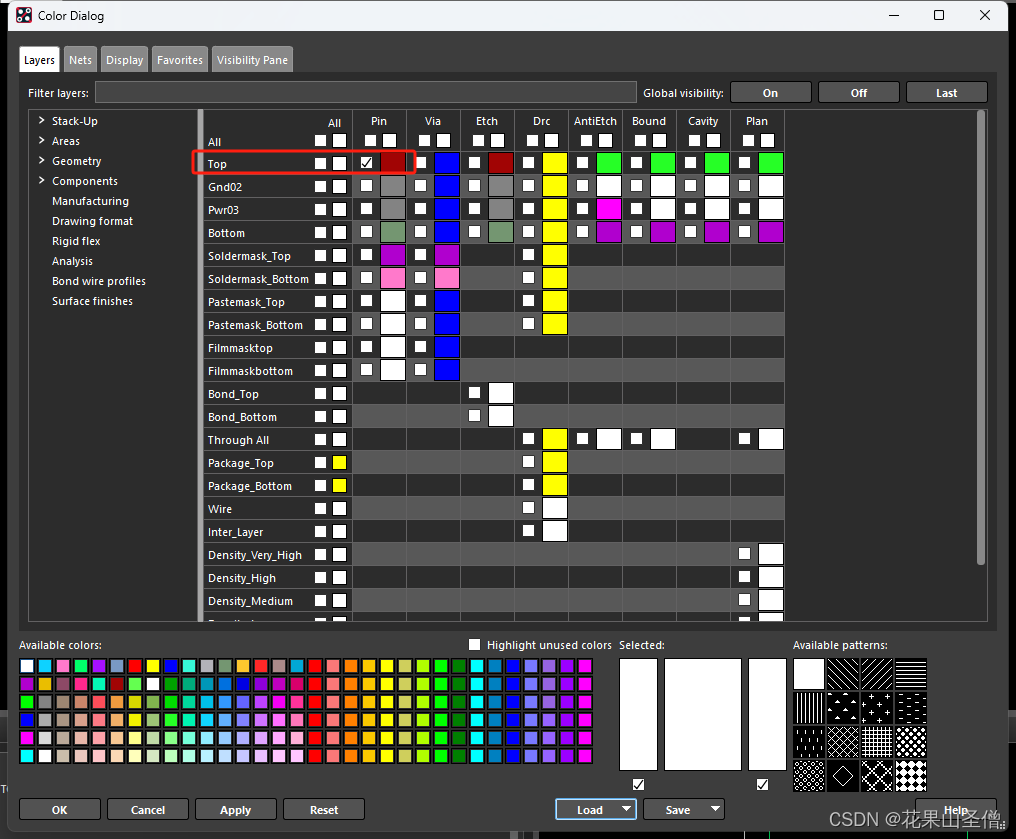

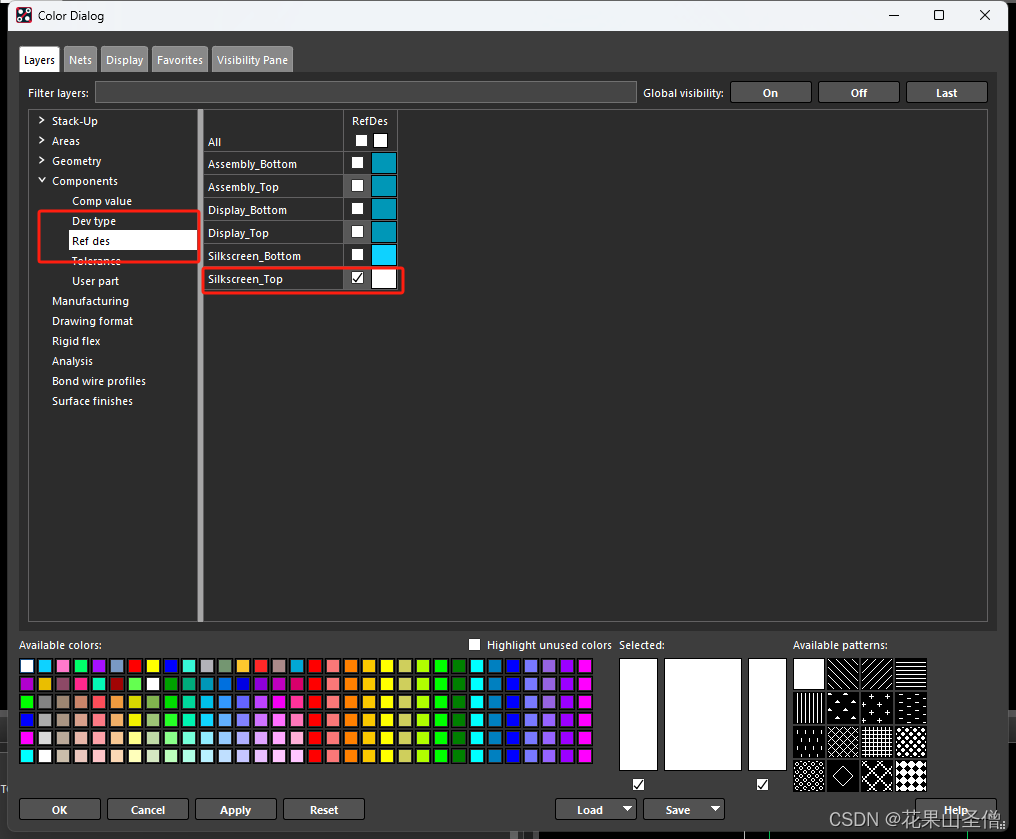

- 我们先添加底层线路文件,需要过孔,引脚,线路,板框这四个层叠,先打开颜色管理器,点击Off

- 然后选中相应的四层,再点击Apply,OK,如图

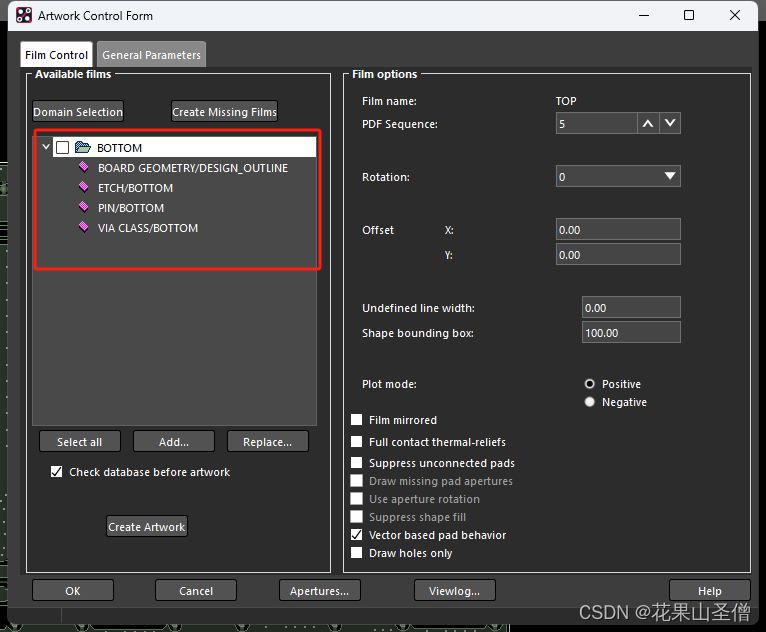

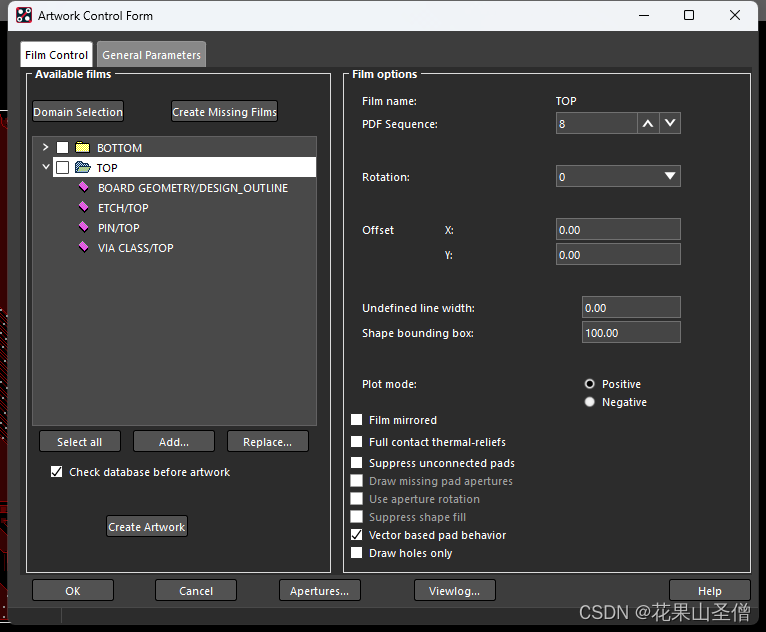

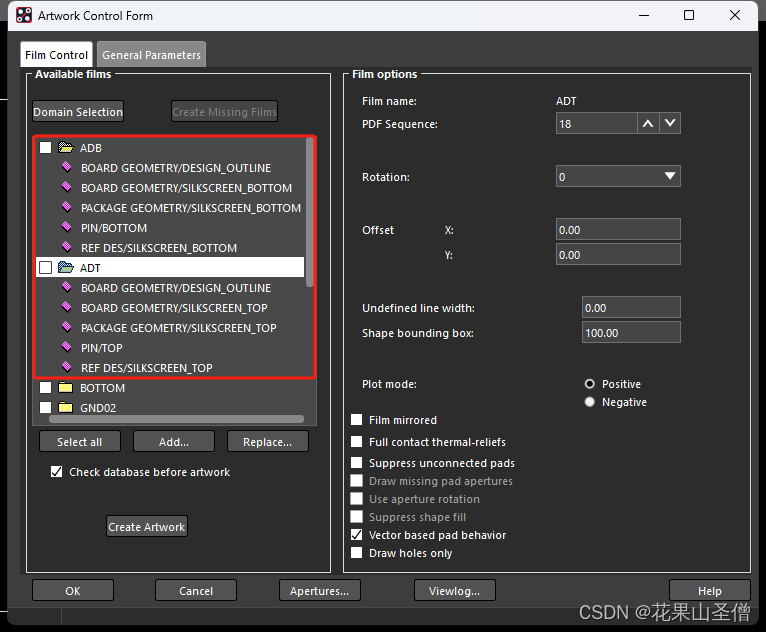

- 点击任务栏的Manufacture-->Artwork...,在原有的文件夹上右键Add,然后输入名称就可以了

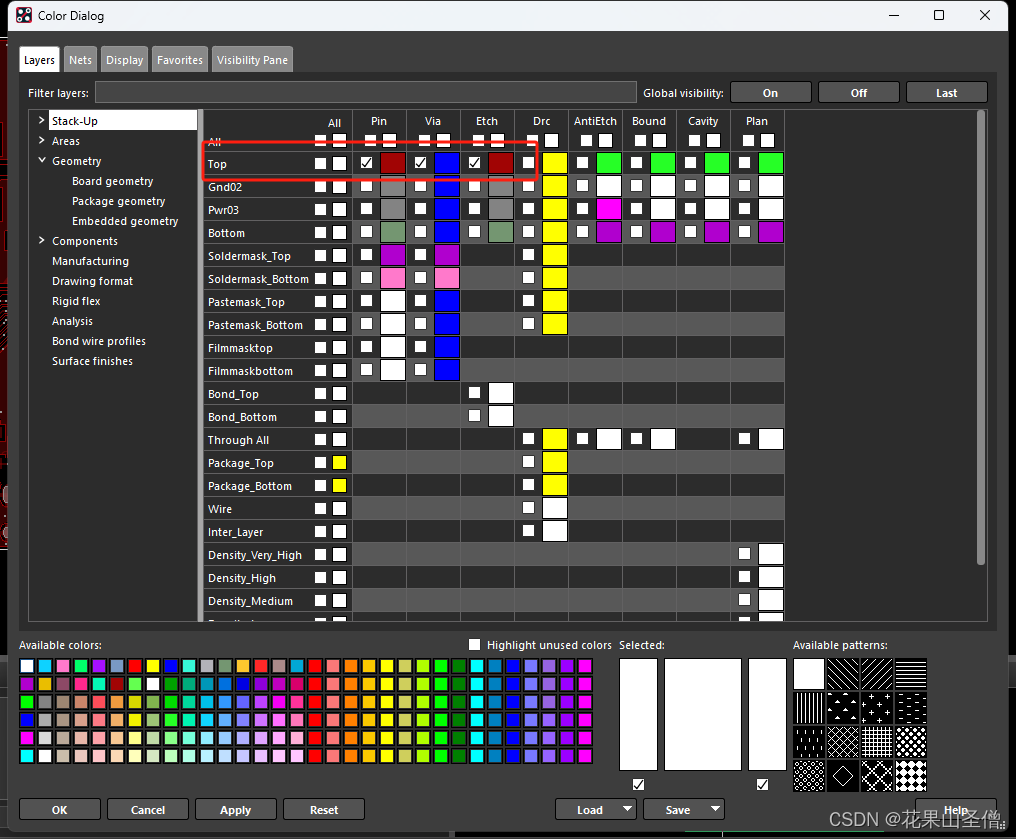

- 然后进行表层线路文件的添加

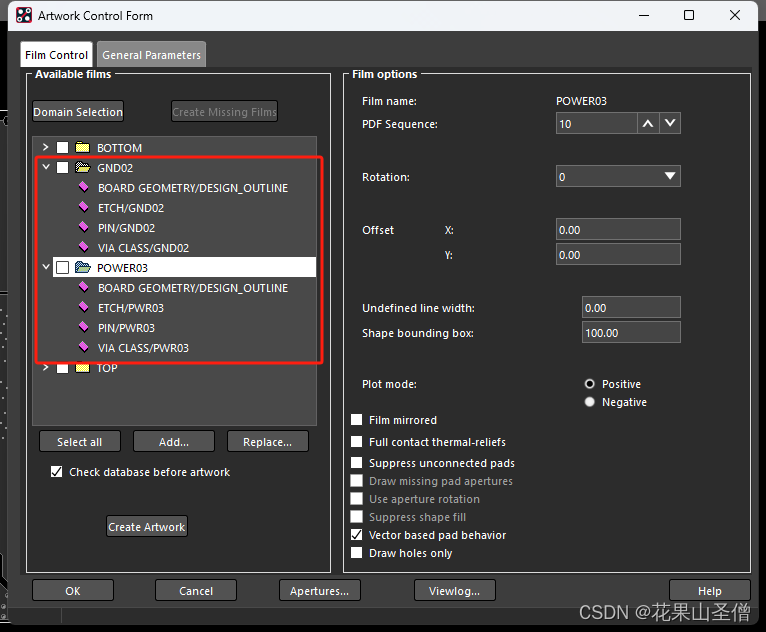

- L2层和L3层线路也是一样的步骤,这里不过多展示

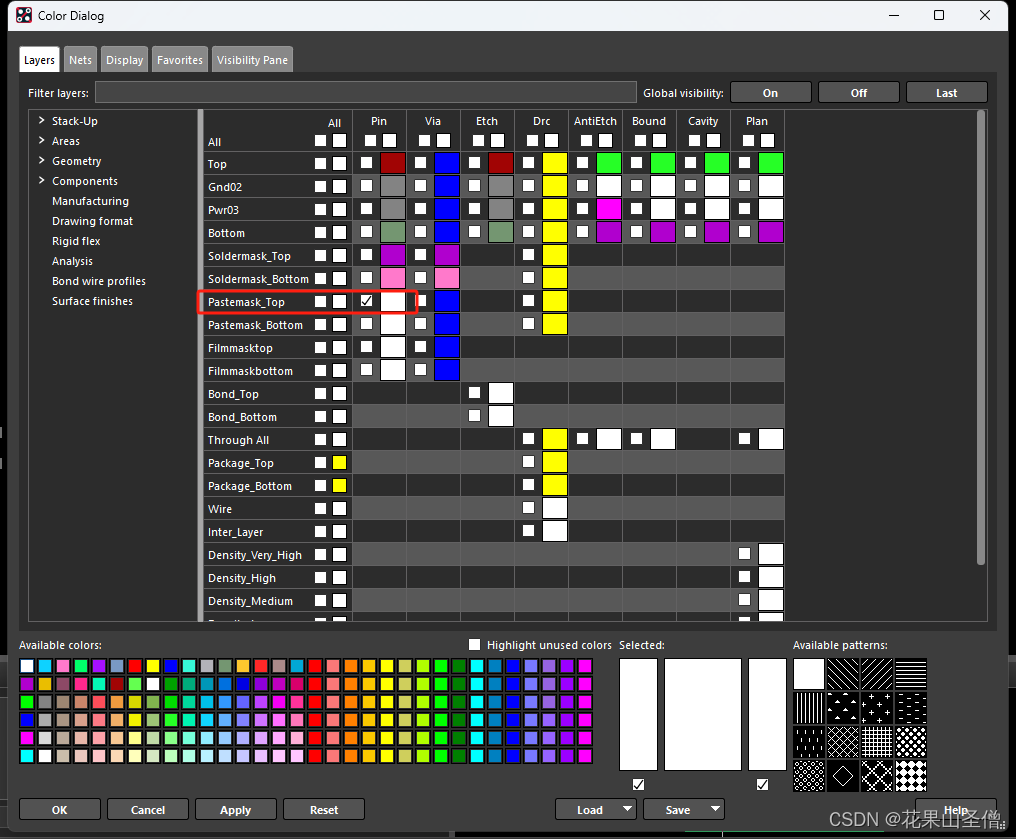

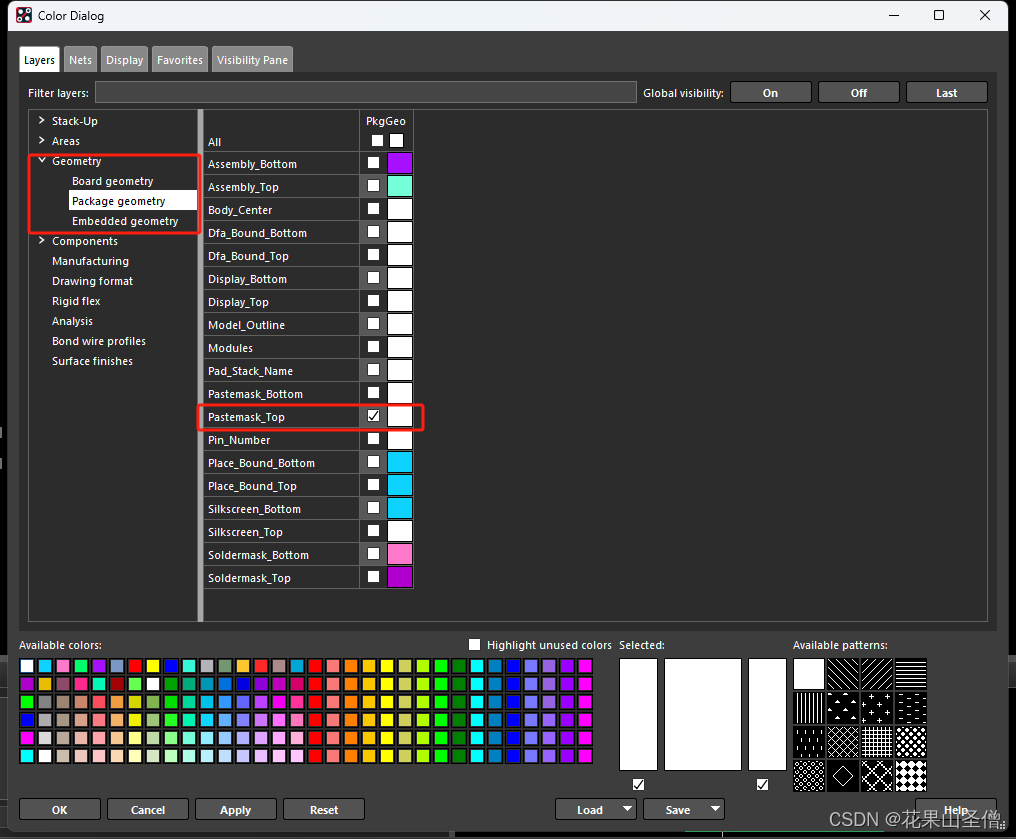

- 接下来是表层和底层的钢网文件,表层和底层是同类的层叠,这里展示表层的演示

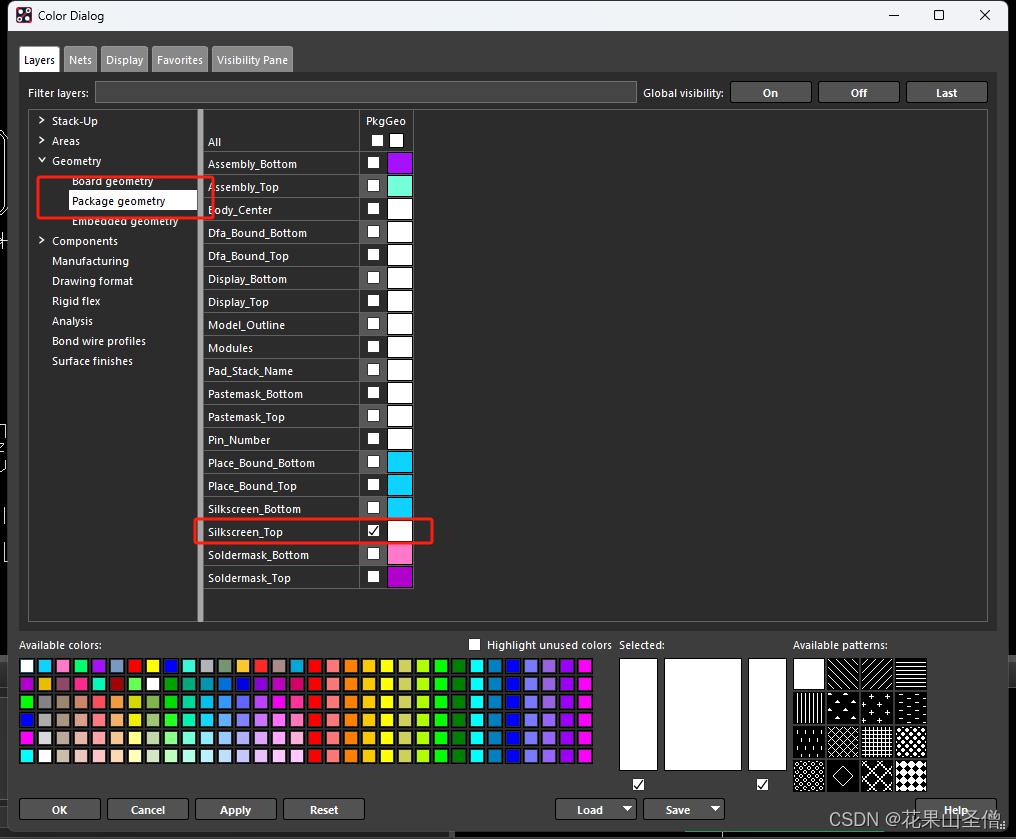

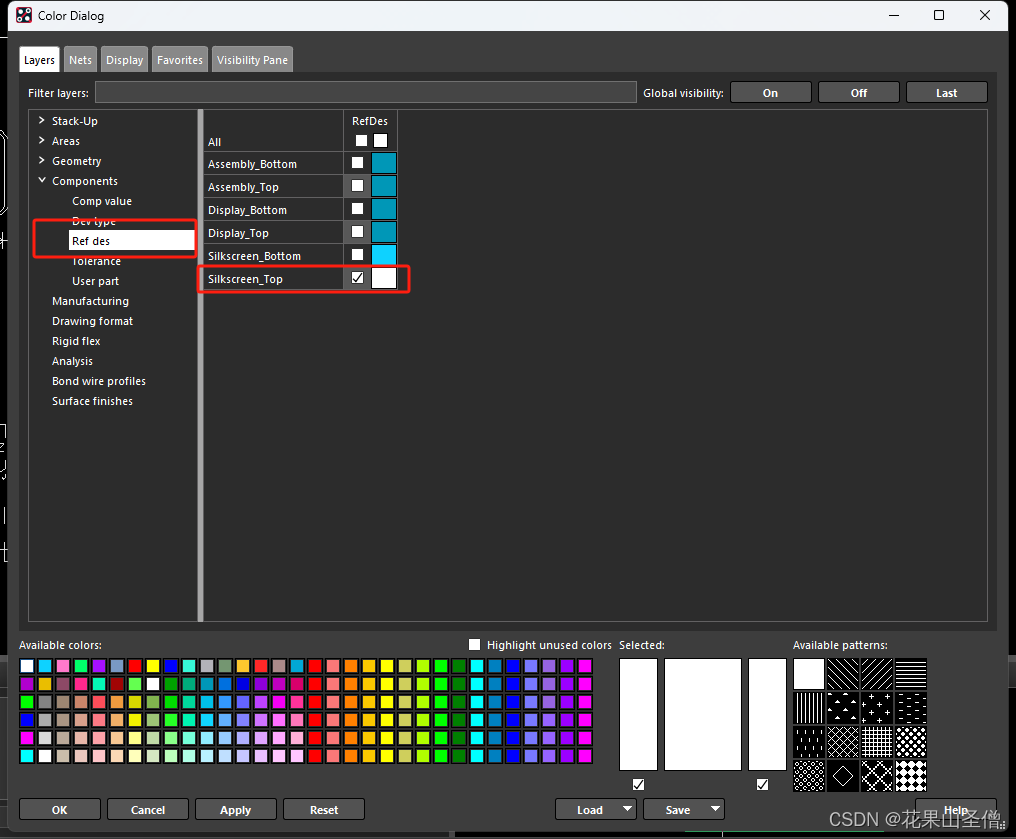

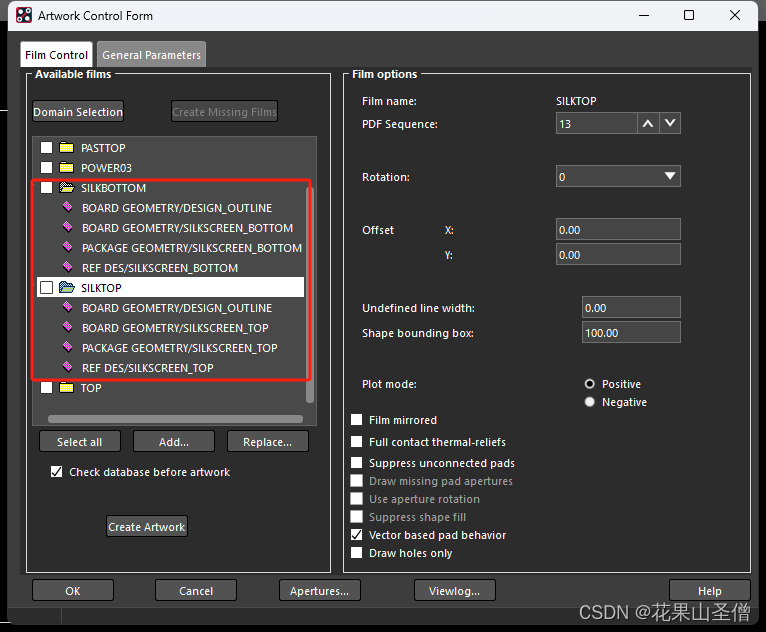

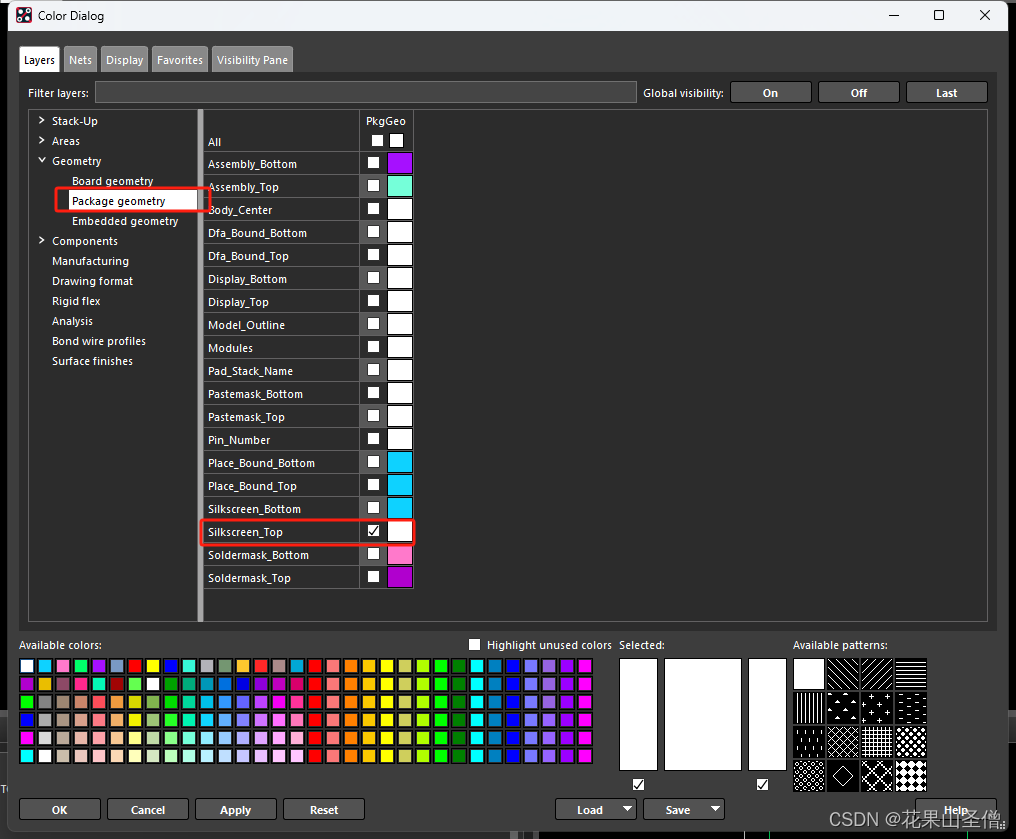

- 然后是丝印层的层叠,表层和底层种类一样,以表层展示

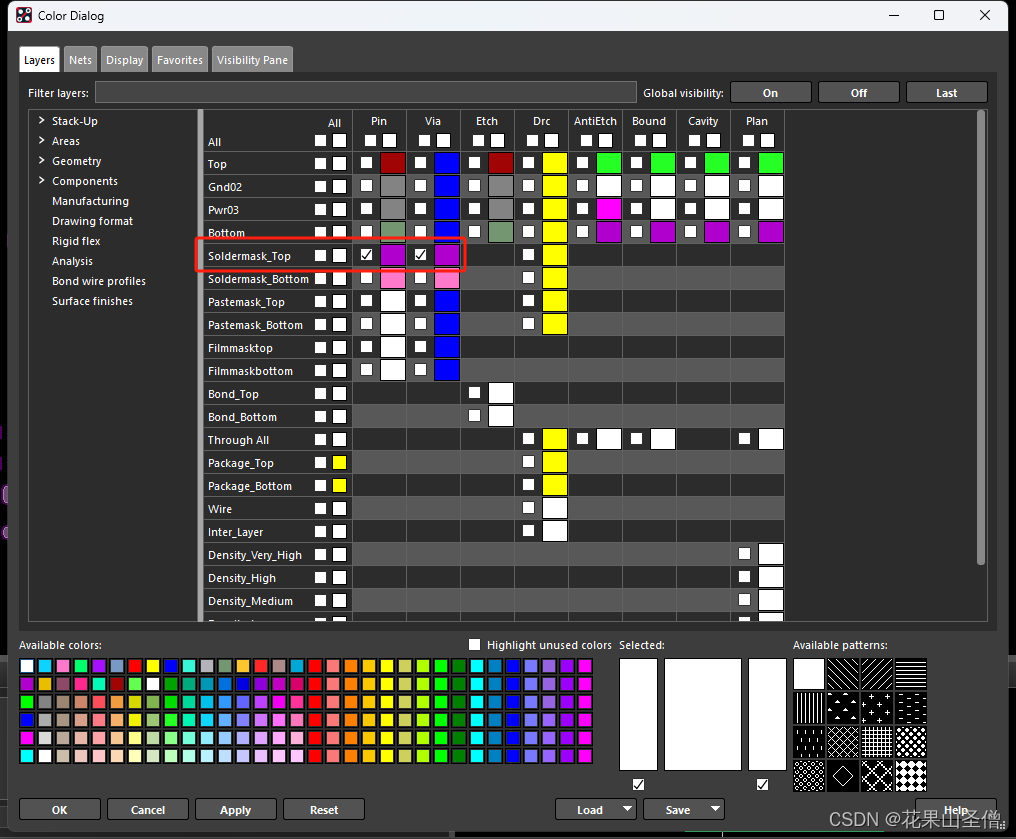

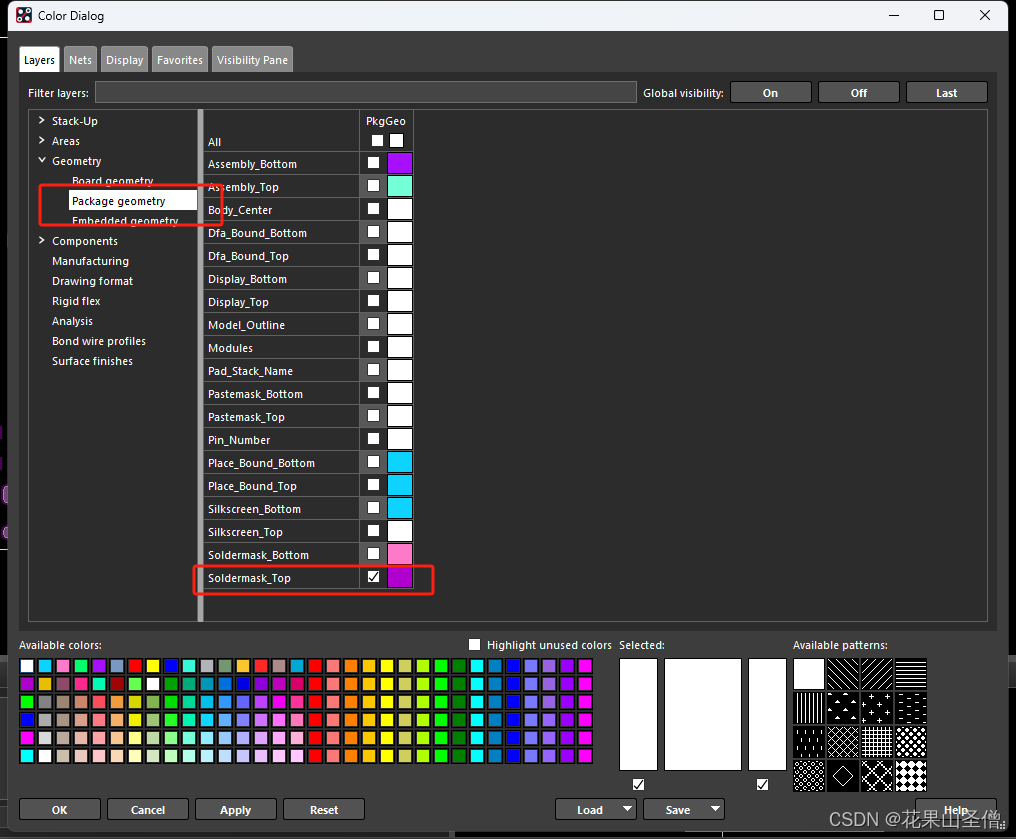

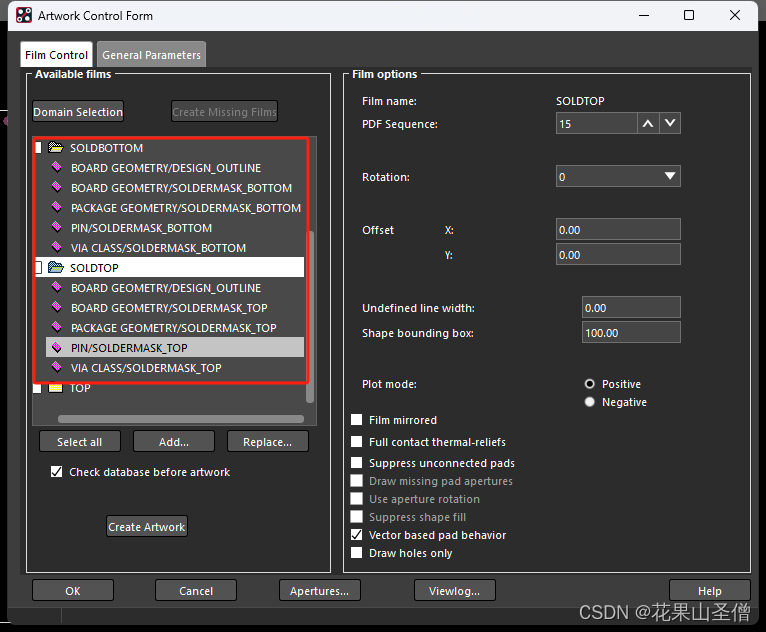

然后是阻焊层的层叠,表层和底层种类一样,以表层展示

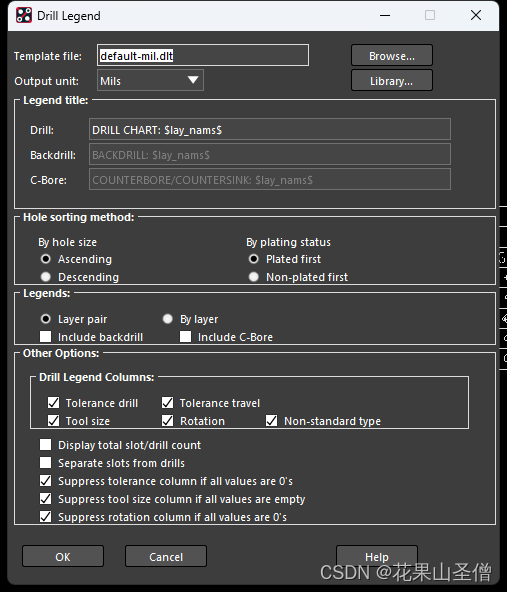

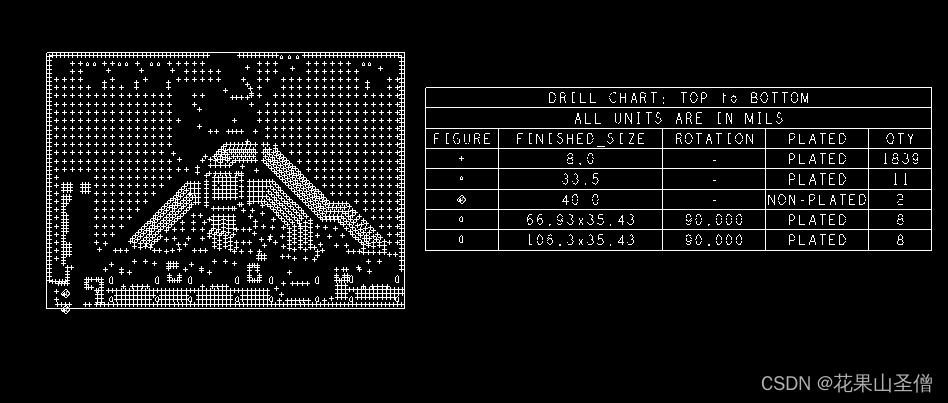

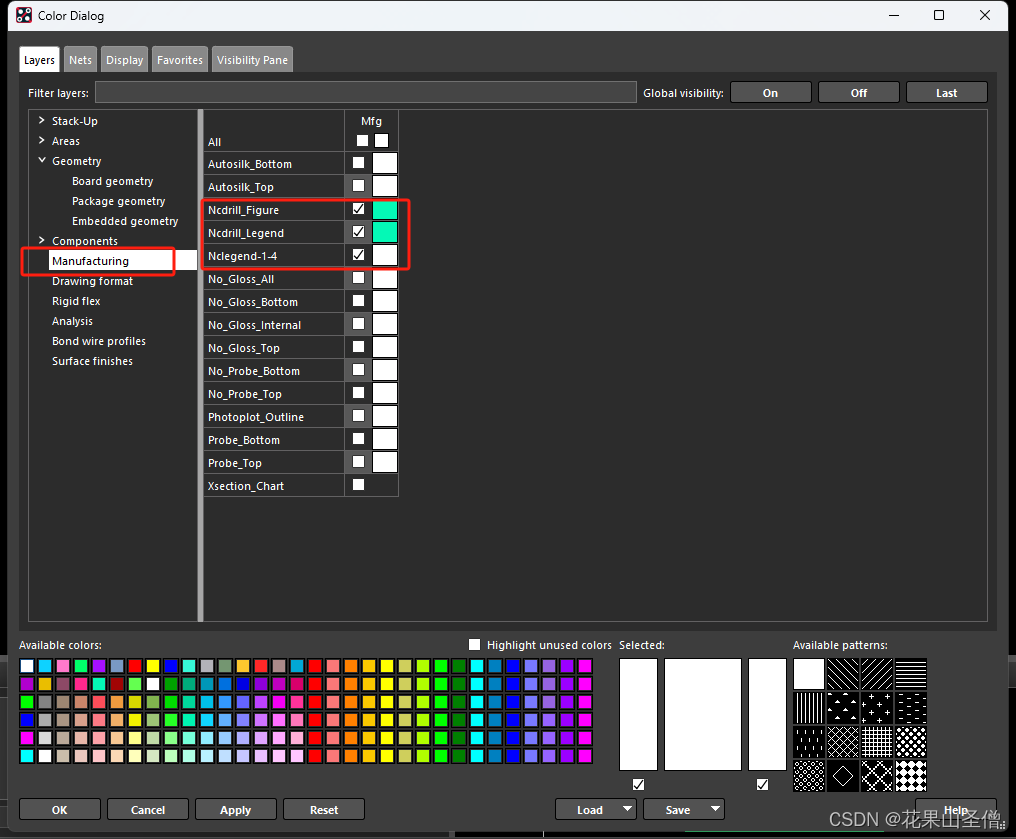

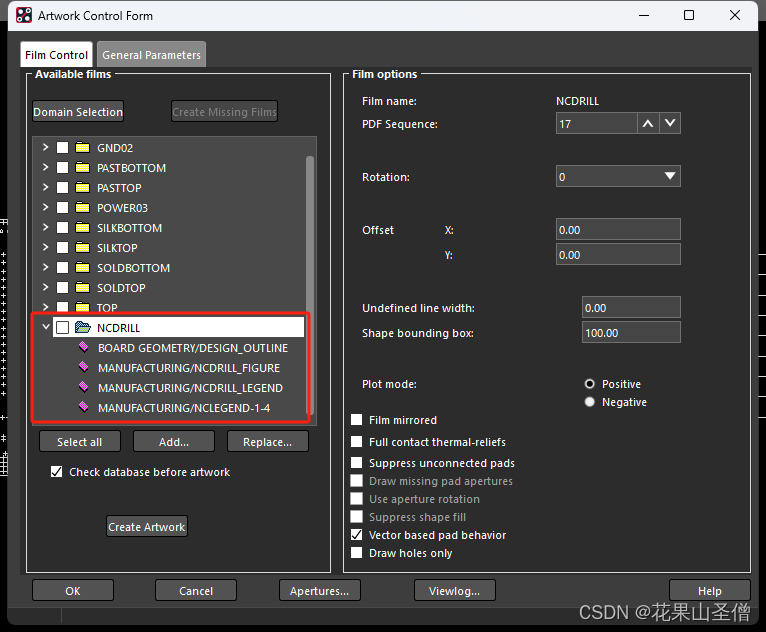

- 最后是钻孔层,这一层稍微麻烦一点,先要点击Manufacture-->NC-->Drill Legend,点击OK,放到PCB旁边,然后再去搞层叠

致此,所有层叠都设置完成

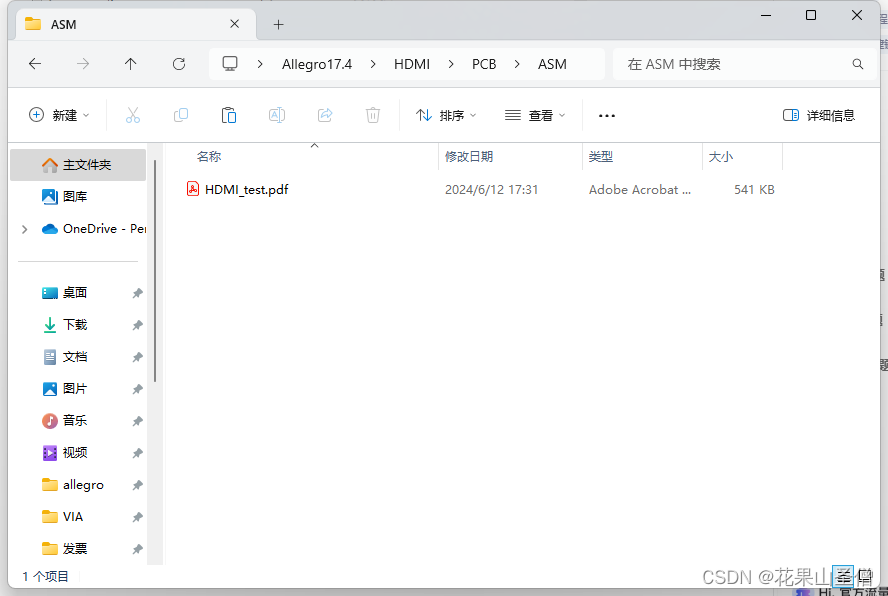

二、装配图文件设置导出

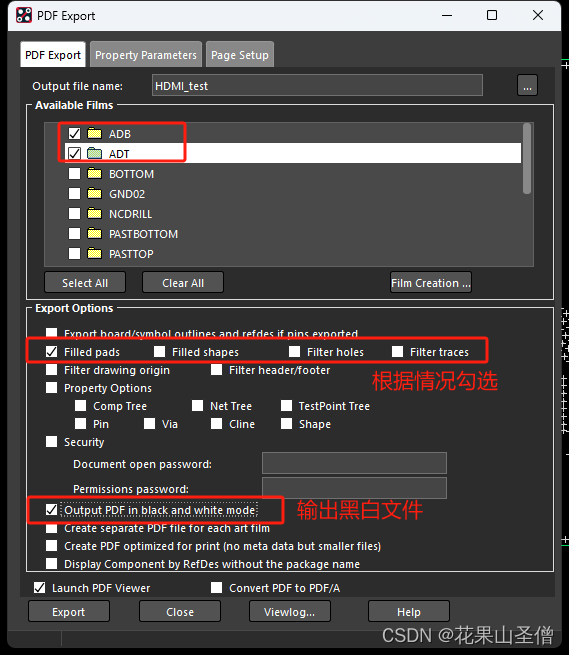

为了手工焊接,需要导出装配的PDF,方便进行手工焊接,表层和底层操作一样,以表层为例展示

点击File-->Export-->PDF...,按如图参数设置,点击Export输出,在PCB路径中,文件后缀为pdf

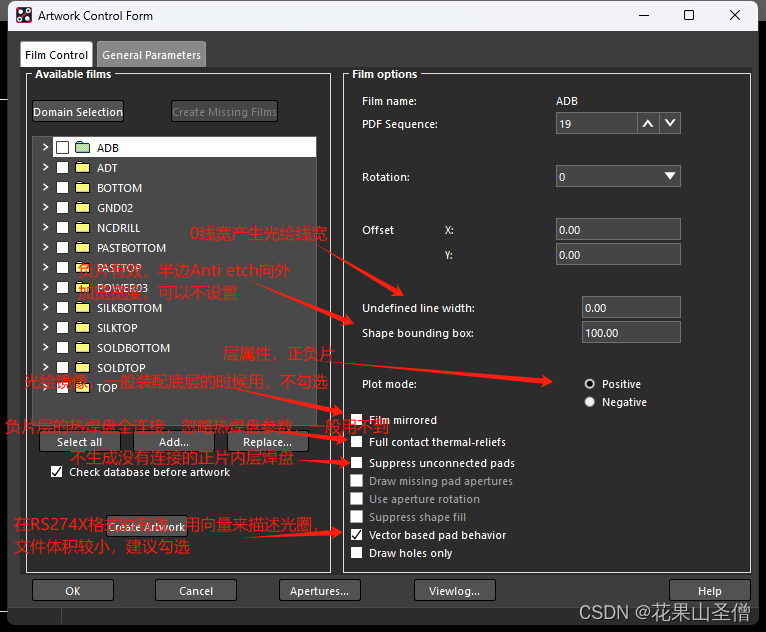

三、光绘参数设置

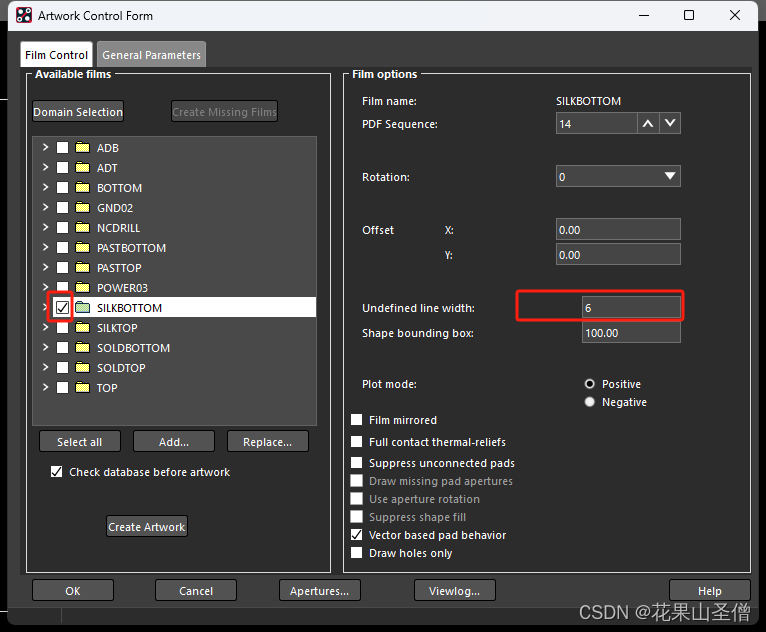

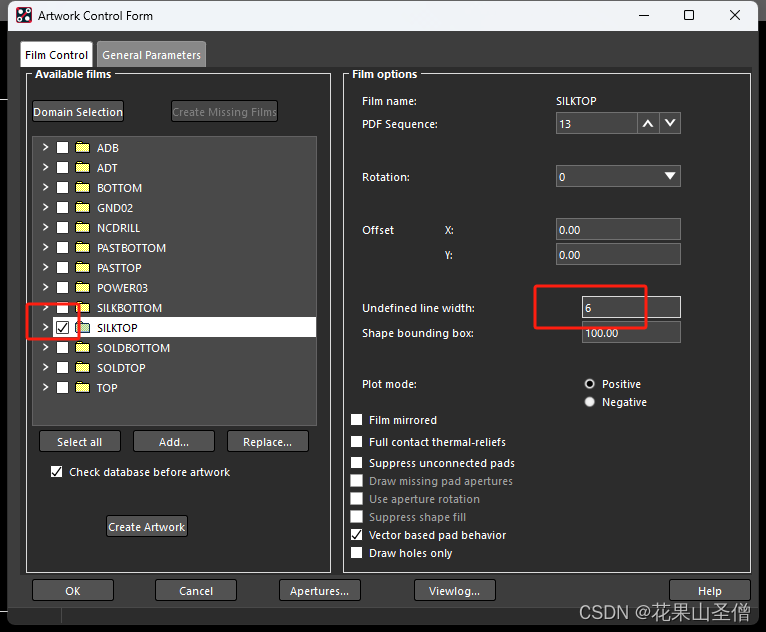

这边的参数一般保持默认即可,需要改动的是SILKTOP和SILKBOTTOM的Undefined line width,如果误操作将丝印以0线宽绘制的话,此选项会自动给你变成指定宽度

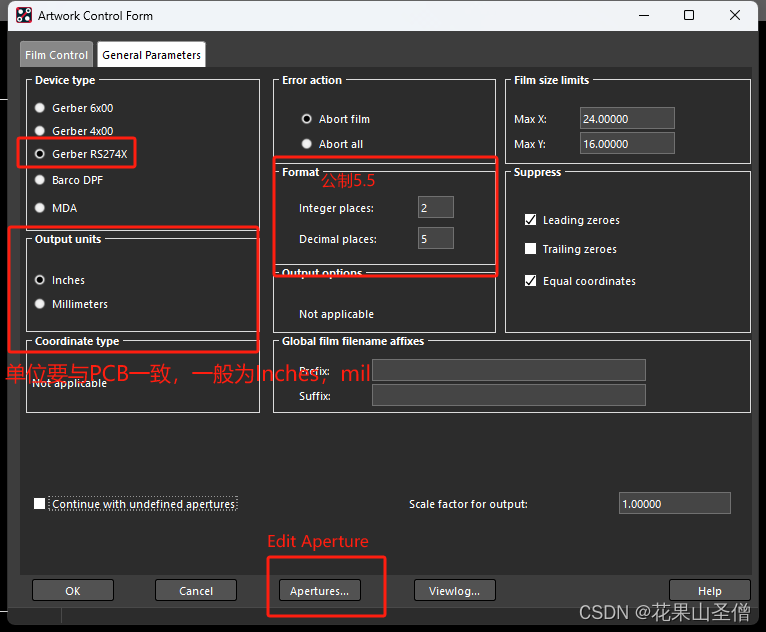

这一界面全都默认,然后Format可以都改成5,点击OK即可

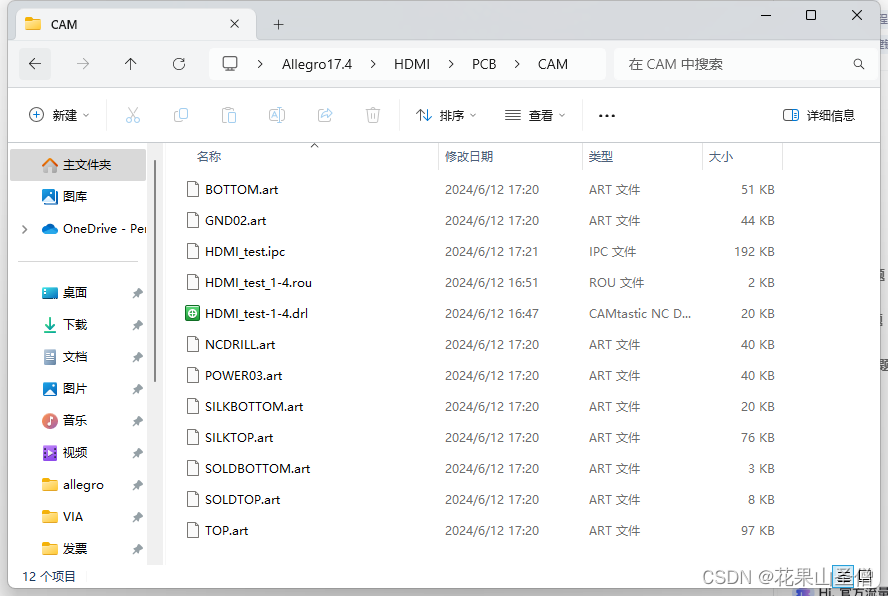

四、Gerber孔符图、钻孔表及钻孔文件输出

孔符图和钻孔表在上文已经讲过了,就是点击Manufacture-->NC-->Drill Legend,点击OK,放到PCB旁边即可,然后是钻孔文件输出

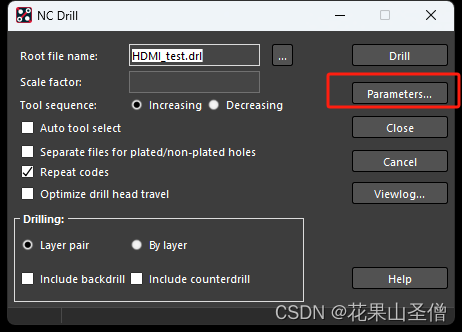

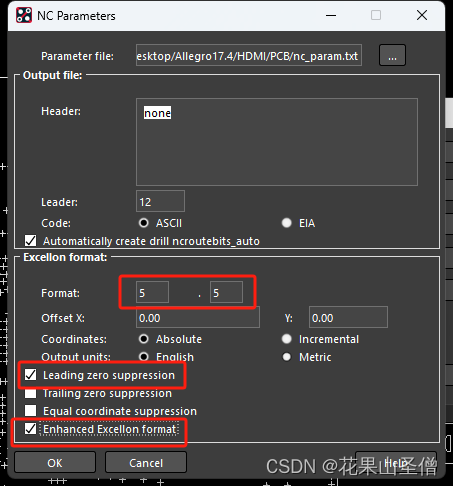

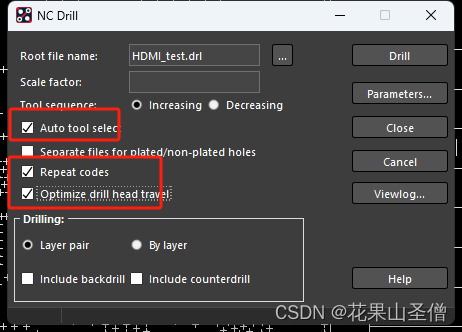

- 点击Manufacture-->NC-->NC Drill...,再点击Parameters...,按如图修改,点击OK,在外面修改勾选,点击Drill即可

文件位置一般和你PCB在同一个路径,后缀带drl的就是钻孔文件

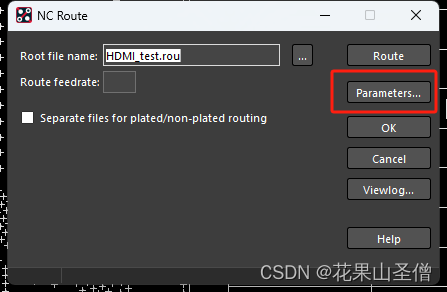

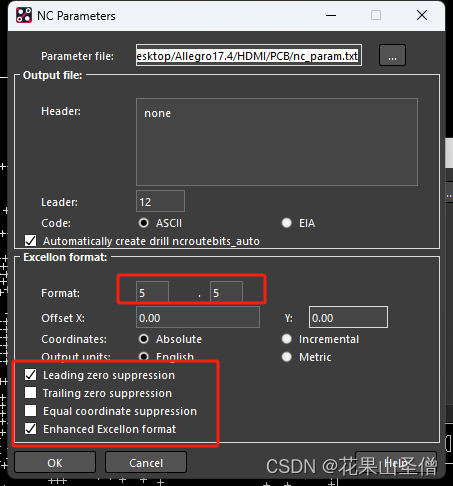

- 如果PCB有槽孔,就要生成槽孔文件同样的点击Manufacture-->NC-->NC Route...,再点击Parameters...,按如图修改,点击OK,在外面点击Route即可,后缀带rou的就是槽孔文件

五、输出Gerber文件

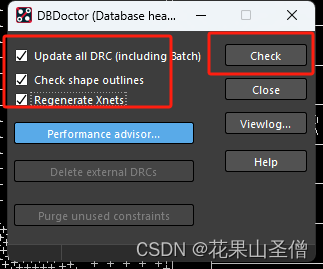

生成光绘前,先要进行DB检查,为了检验莫名其妙的错误bug,点击Tools-->Database Check...,如图全都勾选,再点击Check,在命令行显示DRC errors:0 Done DBdoctor就是没有错误

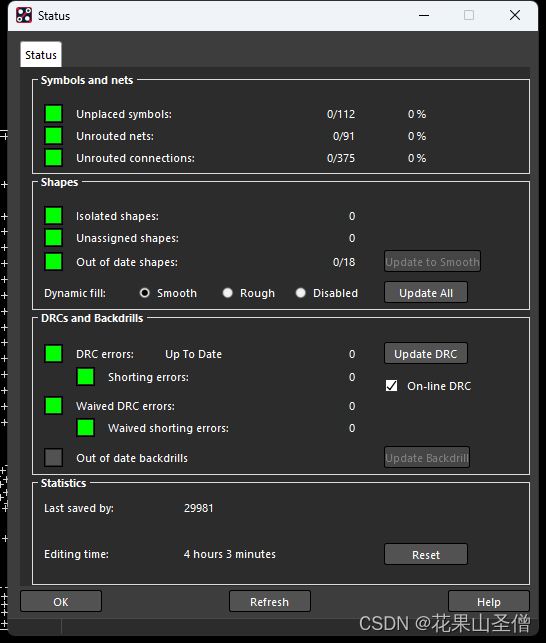

然后点击Display-->Status...,显示没有错误即可

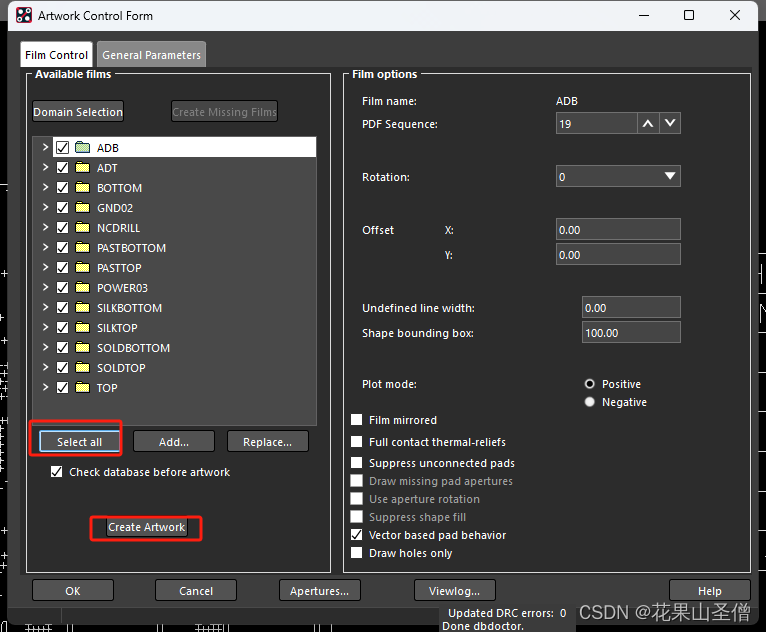

然后打开光绘层叠,选中全部,下面的Check database before artwork是在输出之前DB一下,可以勾选,然后点击Create Artwork输出光绘

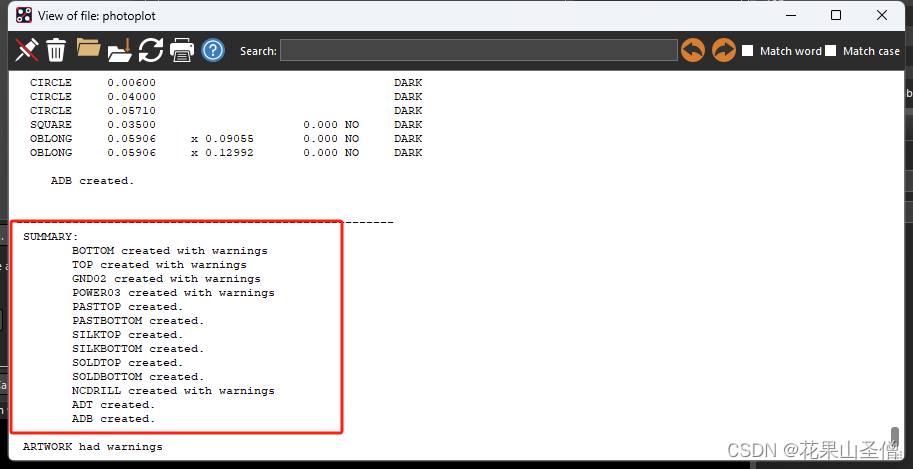

把弹出的文件拖动到最后看有没有error,警告没关系,没有error就成功了

在PCB路径下就会产生相应的光绘文件,后缀是art

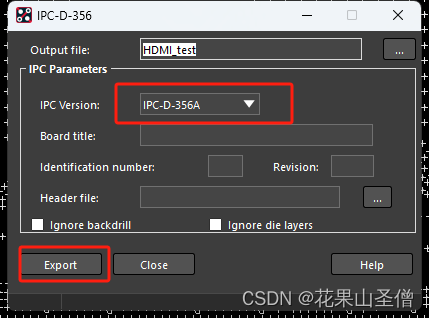

六、输出IPC网表

点击File-->Export-->IPC356...,选中IPC-D-356A,点击Export输出,还是在PCB路径中,文件后缀为ipc

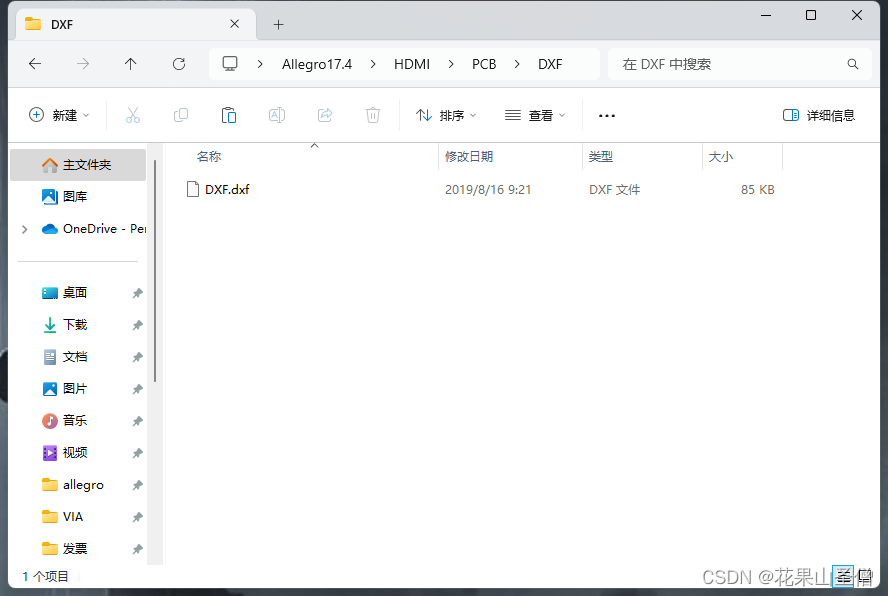

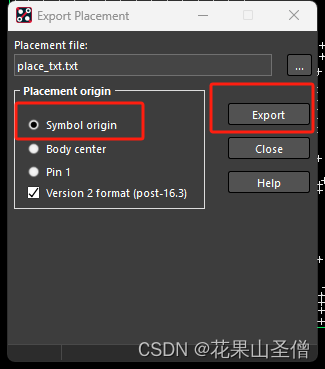

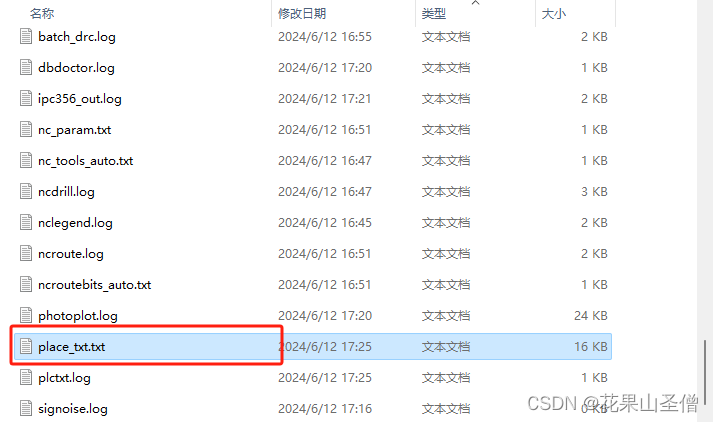

七、导出坐标文件

点击File-->Export-->Placement...,选中封装原点,点击Export输出,还是在PCB路径中,文件后缀为txt

八、文件打包