前言

这是博主自己原创的成果,如要转载或者引用,请标明出处,具体的视频讲解见我的bili视频讲解,先附链接

引出目的

- 课题项目需求做一个基于FPGA的相控扬声器

- 后面进行数字滤波器的设计与实现

- 后期FPGA算法的实现

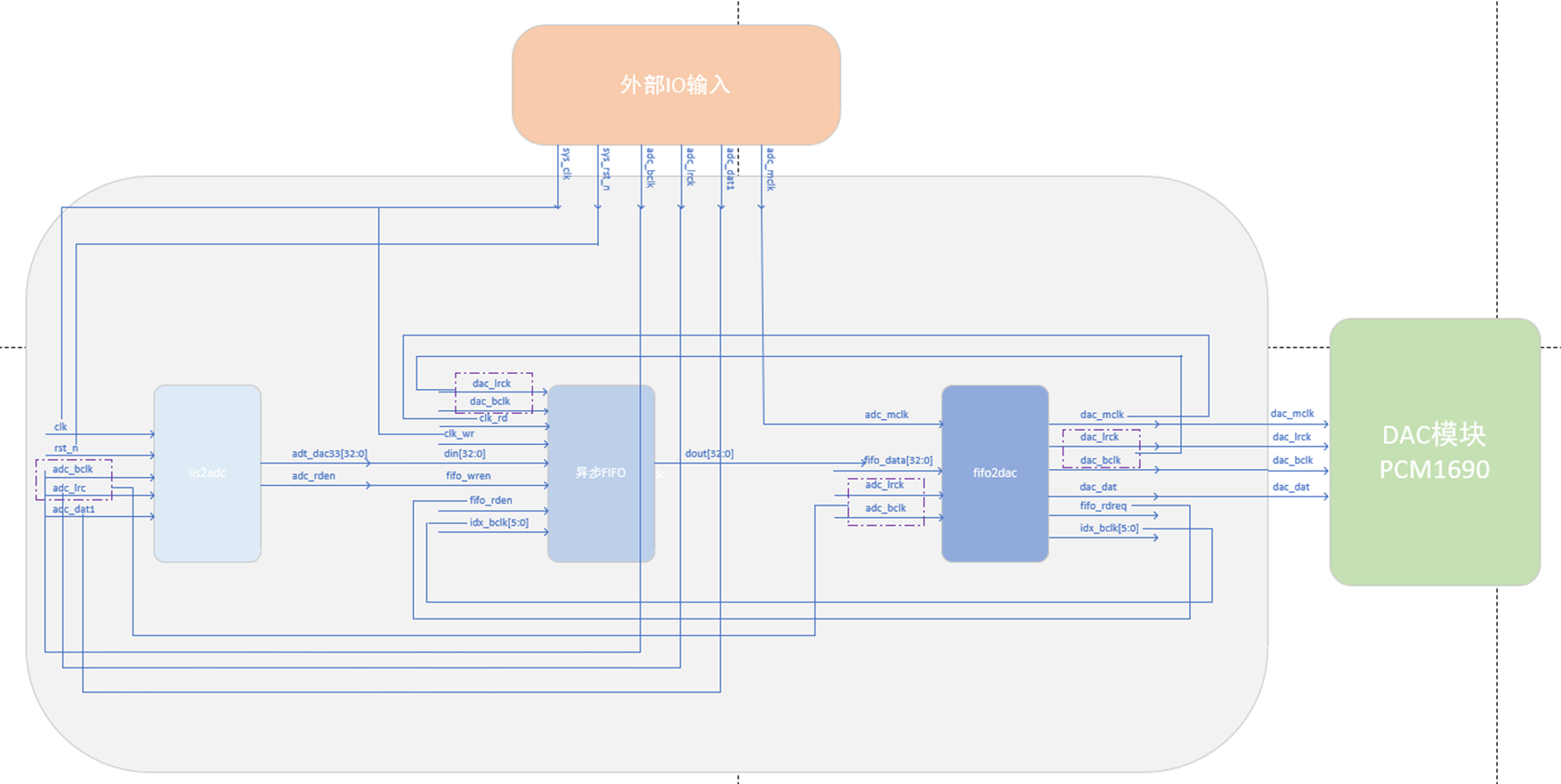

整体模块框图

驱动原理与程序设计思路

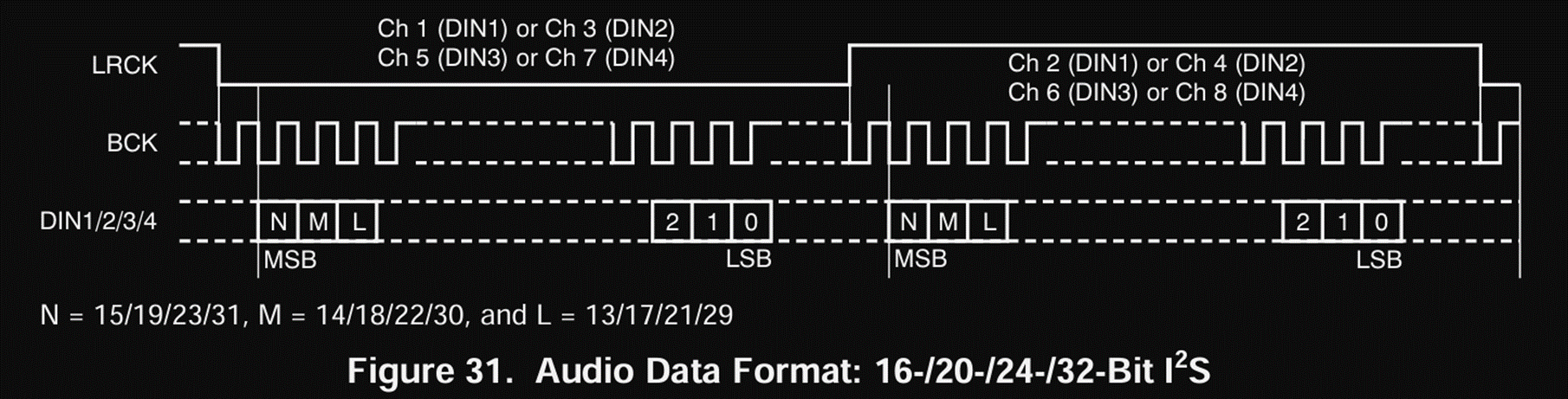

I2S时序图详解

注意三个点:

- LRCK的跳变沿总是对应着BCLK的下降沿

- DIN总在BCK的上升沿保持不变(进行数据传输),DIN总在BCK的下降沿改变数据

- 对于I2S的标准模式,第一个BIT的传输总是在LRCK跳变沿后的BCK的第二个上升沿才开始进行,这里要特别注意

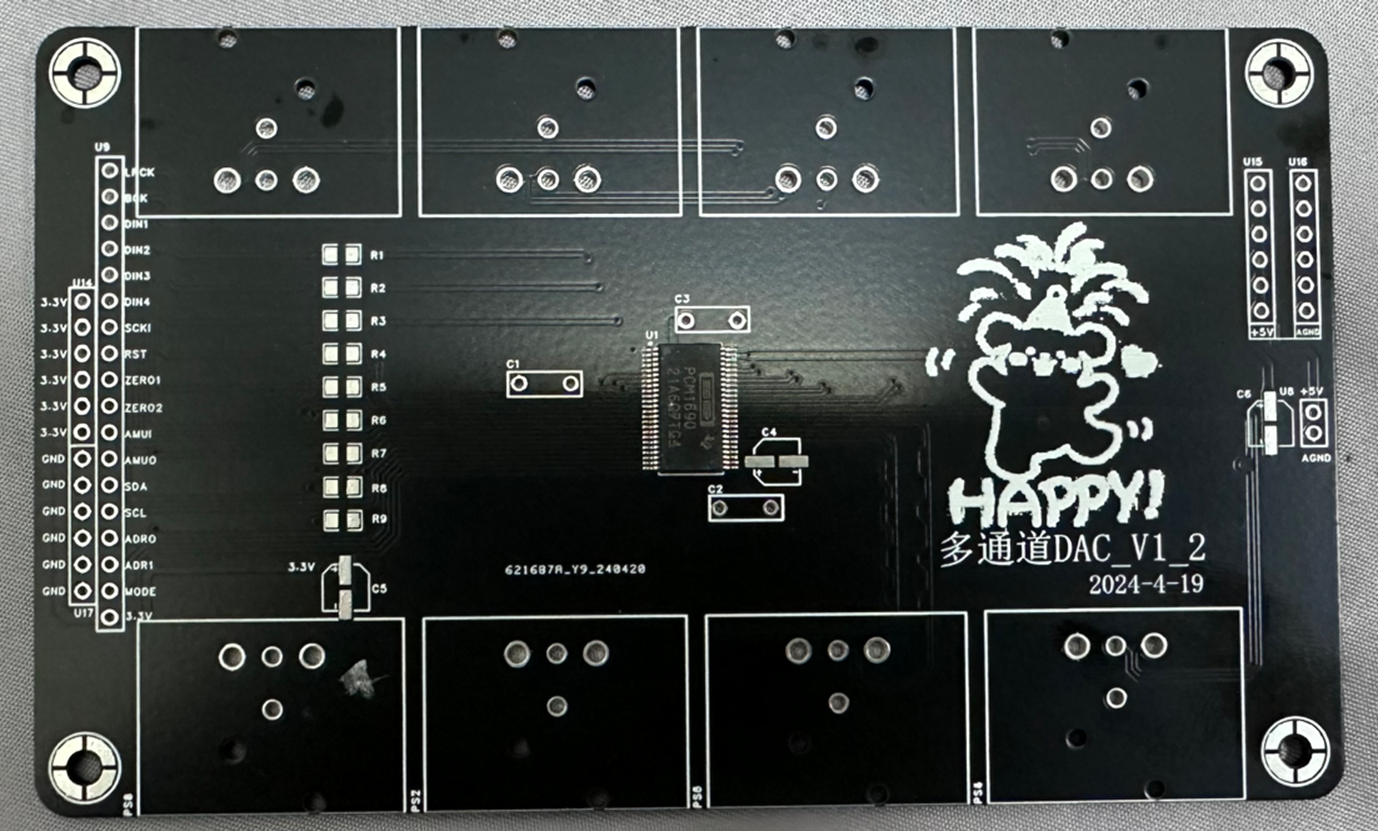

自己设计的PCM1690八通道DAC(已经测试通过)

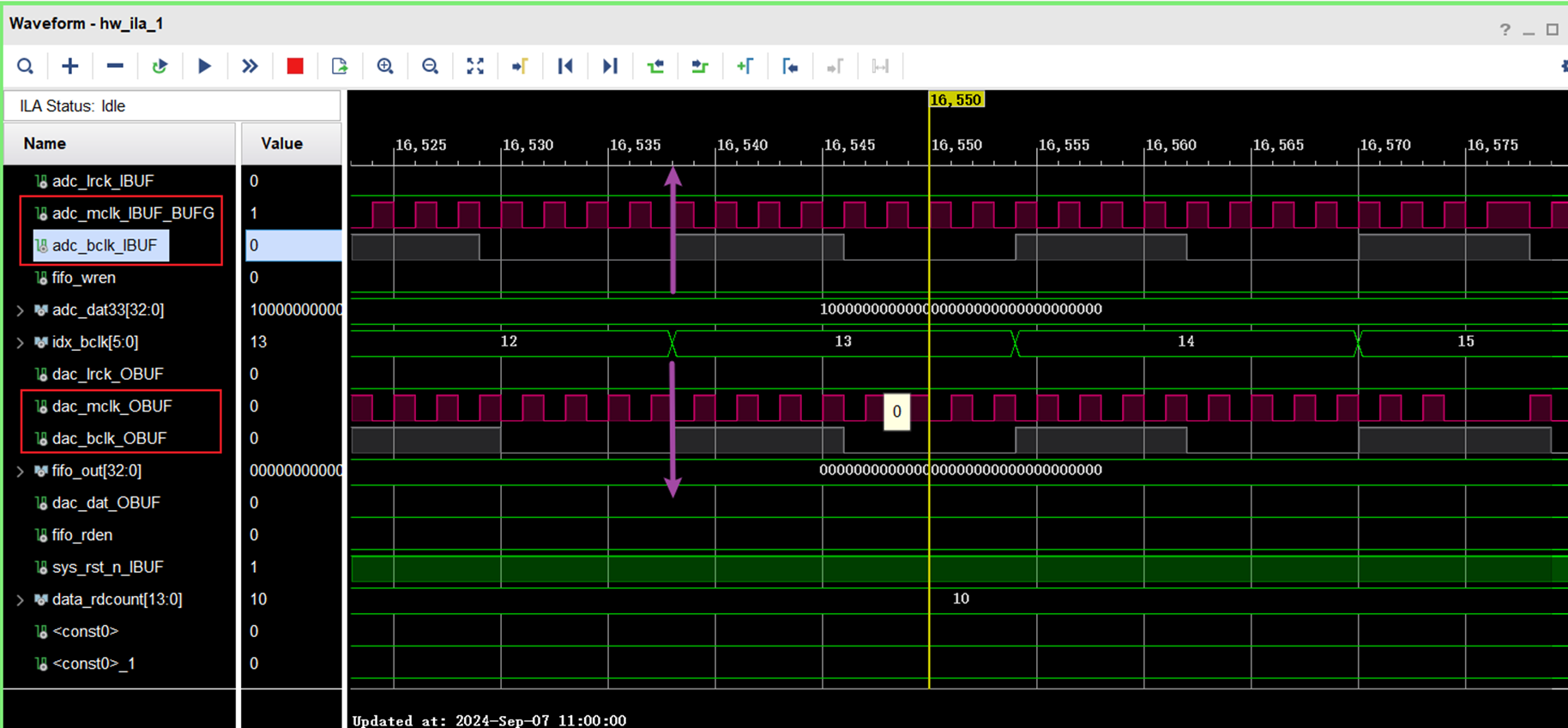

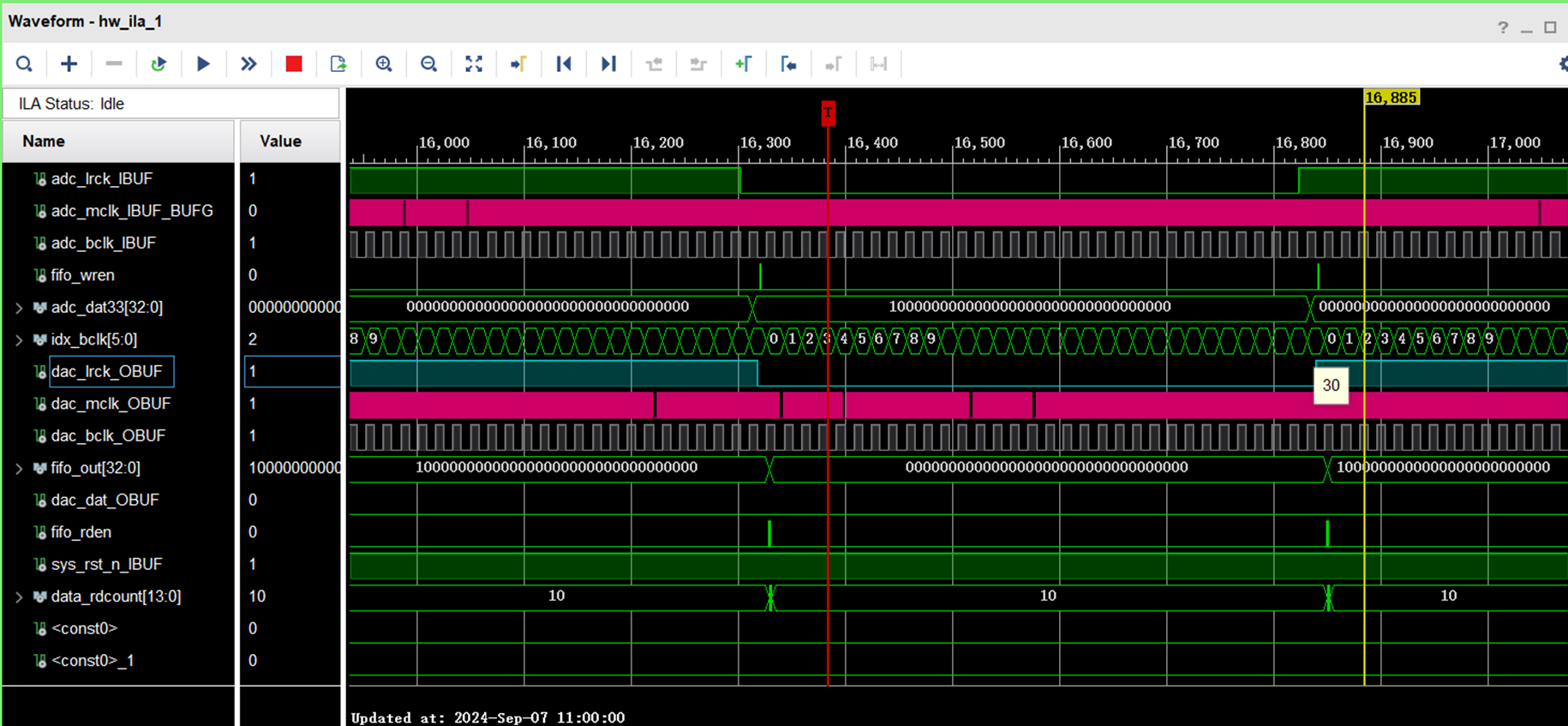

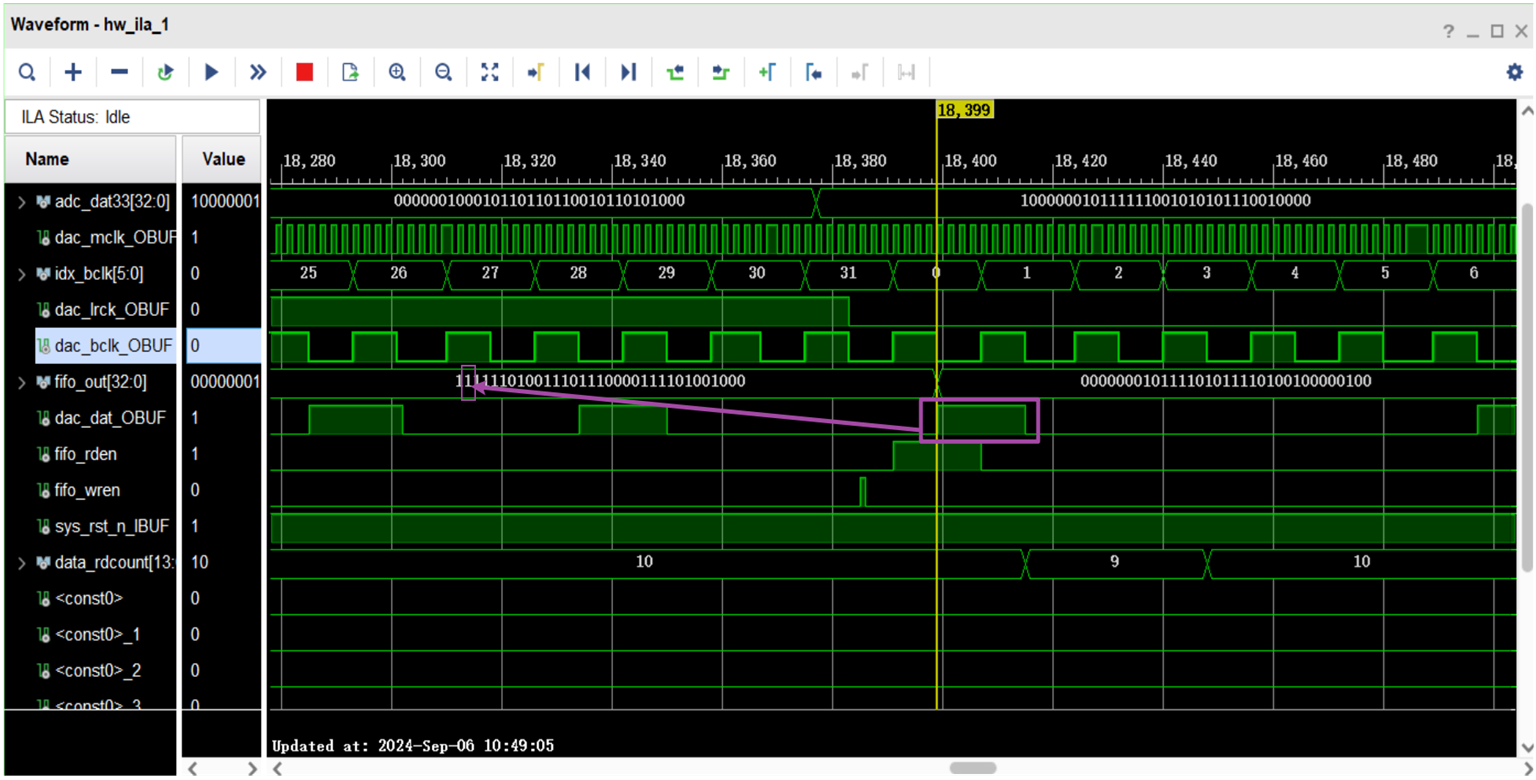

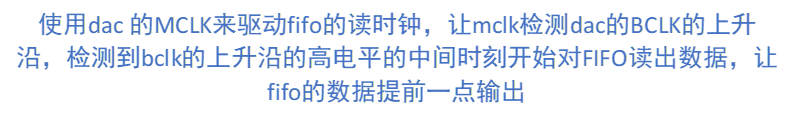

ILA信号抓取

- ADC的BCLK的跳变沿对应MCLK的上升沿

- DAC的BCLK的跳变沿对应MCLK的下降沿

- 这可能是取决于I2S的标准版本和器件的配置

多了1bit的冗余位(最高位),0代表左声道,代表右声道

调试中的BUG

- 声道最高BIT位输出错误

- 没有声明的变量编译器没有报错

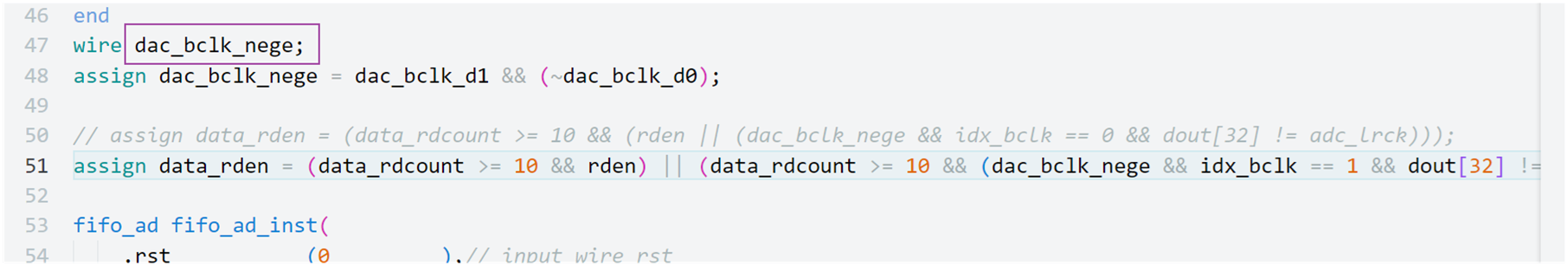

注意:这书最终修改好的程序,原来的程序是在第47行,我写的是wire dac_bclk_pose;也就是说,我没有定义dac_bclk_nege,但是程序编译正常

- 关于PCM1690的

使用5V供电 需要两条线,否则右声道有吱吱的电流声,或者给开发板使用DC12V进行供电!!