相关阅读

Design Compiler![]() https://blog.csdn.net/weixin_45791458/category_12738116.html?spm=1001.2014.3001.5482

https://blog.csdn.net/weixin_45791458/category_12738116.html?spm=1001.2014.3001.5482

简介

在使用Design Compiler时,可以对目标逻辑库进行特征分析,并创建一个称为ALIB的伪库(可以被认为是缓存),伪库中包含复杂布尔函数的实现方式(与尺寸、延迟无关),这些布尔函数是基于库中已有的、更简单的门单元实现的(纯组合逻辑)。

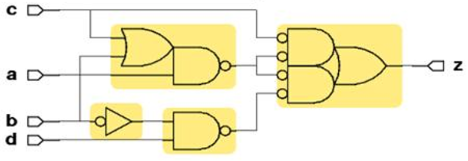

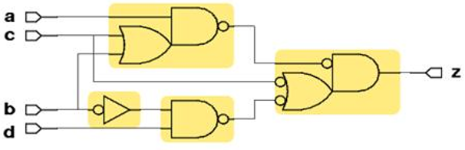

以下面的布尔函数为例,图1和图2是它在ALIB中的两种实现方式,其中黄色为逻辑库中的门单元。库特征分析将构建所有四输入以内的布尔函数,以及常用的超过四输入的布尔函数,每个布尔函数大约生成十五种实现方式。

图1 实现方式

图2 实现方式

ALIB为Design Compiler提供了更大的灵活性和更大的解空间,以探索面积与延迟之间的权衡,但需要注意的是,只有compile_ultra命令才能利用ALIB进行综合,而不能使用compile命令。

虽然使用compile_ultra命令会自动创建ALIB(如果它不存在或已过时),但由于对每个逻辑库进行特征分析可能会耗费一些时间,建议提前生成目标逻辑库的ALIB并将其存储在一个共享位置,以便多个用户可以共用该库。

生成和使用ALIB

使用compile_ultra命令或alib_analyze_libs命令会在alib_library_analysis_path变量(默认值为./,即当前工作目录)指定的目录下创建一个特定版本的子目录,并将生成的ALIB存储在该子目录中。

例如,以下命令会为名为fast.db的目标逻辑库生成fast.db.alib文件(添加了.alib后缀以建立两者之间的联系),并将其存储在目录/remote/libraries/alib/alib-**下:

dc_shell> set_app_var target_library "fast.db"

dc_shell> set_app_var link_library "* fast.db"

dc_shell> set_app_var alib_library_analysis_path "/remote/libraries/alib"

dc_shell> alib_analyze_libs // 或compile_ultra命令生成的目录结构如下所示,其中alib-51为Design Compiler Y-2006.06-SP4版本前创建的子目录,而alib-52为Design Compiler Y-2006.06-SP4版本及以后创建的子目录,因此该版本后的所有版本都可以共用ALIB。

/remote/libraries

│

├── target_libraries

│ ├── x.db

│ ├── y.db

│ └── z.db

│

└── alib

├── alib-51

│ ├── x.db.alib

│ ├── y.db.alib

│ └── z.db.alib

│

└── alib-52

├── x.db.alib

├── y.db.alib

└── z.db.alib