"硬件系统庞杂、调试周期长"

"高频模拟前端不稳定,影响采样精度"

"接收和发射链路难以同步,难以扩展更多通道"

"数据流量大,处理与存储跟不上"

这些是大部分客户在构建多通道、高频宽的射频采样链路时,面临的主要问题。

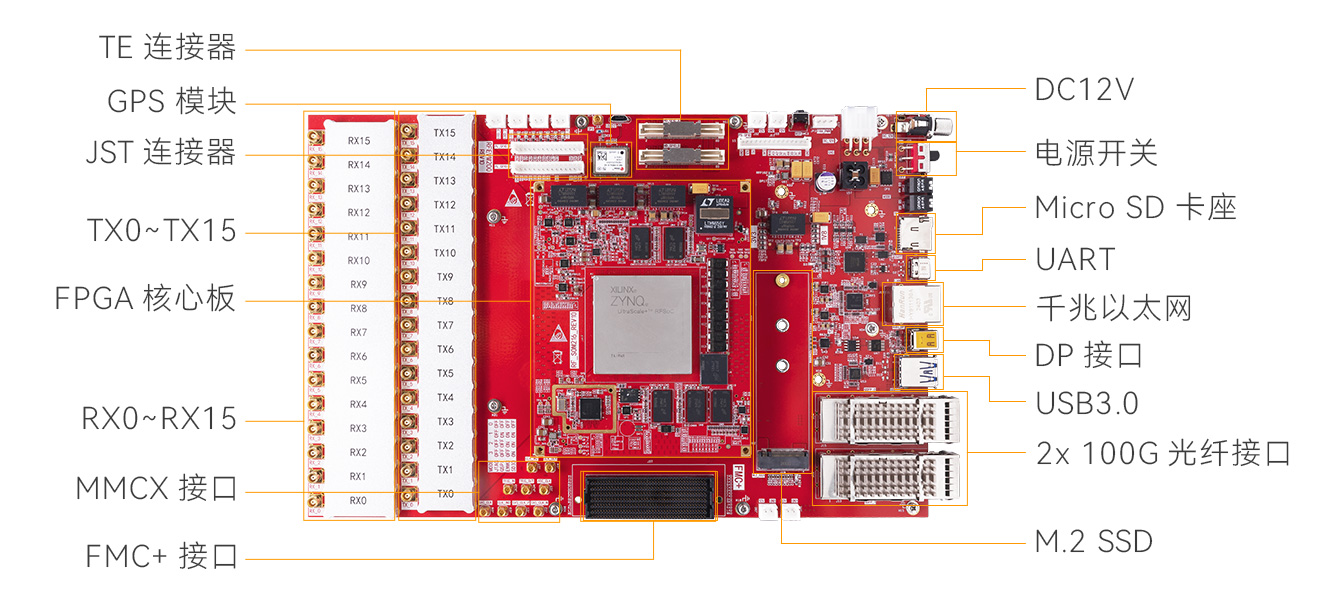

AXRF49 正是为解决这些瓶颈而来------它依托于 AMD 第三代 Zynq UltraScale+ RFSoC ZU49DR,整合了:

-

16 通道 14 位高性能 ADC/DAC

-

高速可编程逻辑(FPGA)

-

四核 ARM A53 + 双核 ARM R5 处理器

-

高性能射频模拟前端(支持 sub-6GHz 直接采样)

让您从繁琐的硬件集成中解脱出来,专注于算法和系统创新。

通信原型开发:从分立器件走向单芯片平台

传统的 Massive MIMO 或小基站原型开发通常需要多个高速 ADC/DAC 模块、FPGA 板卡与嵌入式处理器组合而成,存在体积大、延时高、功耗高、接口调试复杂等问题,导致研发周期长、系统稳定性差。

AXRF49 通过内建的 16 路 14 位 DAC(最高 9.85GSPS)与 16 路 14 位 ADC(最高 2.5GSPS),实现了 sub-6GHz 频段内的直接射频采样与发射 ,彻底省去了中频变换链路。再加上其高达930K 逻辑单元、4272 DSP 单元 的 FPGA 资源,可直接实现信道估计、波束赋形、DFFT、LDPC 解码等物理层加速逻辑。

光纤接口支持2×100G QSFP28 ,配合 5GB PL DDR4 带宽缓存与 M.2 NVMe,本地与远端处理无缝衔接,打造低延时、高并发的无线接入测试平台,适合 5G NR 和未来的 6G 空口研究。

相控阵雷达

同步、多通道、高速处理能力合一

雷达波束控制与干扰信号合成通常对多通道同步、采样精度、低相位噪声、高带宽处理 能力要求极高。而传统以多卡片堆叠方式构建阵列系统,不仅接口繁杂,同步性差,且系统集成工作量巨大。

通过 RFSoC ZU49DR 的 RF-ADC/DAC 模块,AXRF49 可同步采集/发射 16 路射频信号 ,为相控阵波束形成提供硬件基础。利用其可编程插值/抽取(1x~40x)功能,在保证高采样率的同时实现频域调制、抗混叠处理,满足雷达对不同信号体制的适配需求。

结合 FPGA 逻辑资源,可实现LFM 信号调制、脉压、MTI/MTD 处理等关键算法,借助高速光口与外部后端进行实时数据记录或识别。相比传统方案,AXRF49 将"模拟前端+数字处理+系统控制"三者融合于单板,有效缩短系统搭建周期,并降低干扰路径复杂度。

医疗/工业检测新模式

高速数据采集与边缘AI融合处理

在高端超声、光学成像、射线检测等场景中,既需要高采样精度和实时性,又希望将更多智能前处理下沉至边缘端。

AXRF49 通过 RFSoC 将高速模拟采集链路(ADC)与 AI 运算能力有机结合,16 路 14 位 ADC 可覆盖多探头传感器阵列 ,用户可基于强大的 FPGA 资源,灵活部署降噪、滤波、特征提取、智能压缩等算法,在 ARM Cortex-A53 与 R5 核心上进行深度模型推理或控制逻辑处理。

数据可通过NVMe SSD 或 USB3.0 实时落盘,或经高速光纤/以太网上传至边缘服务器,满足工业质检与远程医疗对实时性与数据完整性的双重需求。AXRF49 支持在本地 FPGA 内部署预处理逻辑 ,真正实现**"边采集、边处理"**的架构升级,顺应"采集即智能"的行业趋势。

从多通道射频采集到边缘智能预处理,再到高速数据外联,AXRF49 让原型验证不再受制于平台碎片化。它能帮助您缩短研发路径,助力您的方案更快落地、更稳健走向工程化。