在RoCE v2协议中,RoCE v2队列是数据传输的最底层控制机制,其由工作队列(WQ)和完成队列(CQ)共同组成。其中工作队列采用双向通道设计,包含用于存储即将发送数据的发送队列(SQ)和用于存储已接收到的数据的接收队列(RQ),二者共同组成了端到端的数据传输管道(Pipeline)每一个SQ与RQ绑定起来称为队列对(QP),每个队列对中包含有若干个工作队列元素(WQE)和一些其他元素如本地接收队列指针、本地发送队列指针、远程接收队列指针、远程发送队列指针等。同样的,每一个CQ中也存在着若干完成队列元素(CQE)。这两种元素共同作用,管理数据传输过程并确保数据传输的顺利进行。

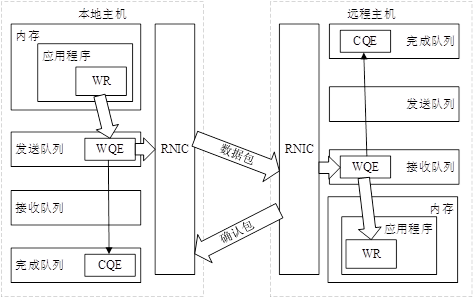

前面提到的五种操作中,只有RECEIVE操作会被添加到接收队列。SEND/RECEIVE操作的完整流程,如图1所示,首先由应用程序创建一个工作请求(WR),并将其提交到相应的工作队列。接着,工作队列会随机生成一个工作队列元素(WQE),该元素包括数据发送缓冲区的起始地址、数据长度、操作类型等相关信息,用于后续的传输操作。在该WQE被网卡操作结束后,网卡将生成一个CQE并放入与工作队列(SQ)对应的完成队列中。对于接收端:接收端网卡同样生成一个WR,其中包含数据接收相关参数,在完整接收数据包之后,将数据放入指定内存位置,并生成一个CQE放入与工作队列(RQ)对应的完成队列中。

图1 SEND/RECEIVE操作流程图 而对于READ、WRITE、ATOMIC这三种单边操作,接收端并不感知这一数据传输过程,故而只消耗发送端QP中的WR,并不消耗接收端即远程主机QP中的WR(有立即数的RDMA Write(RDMA Write with immediate)操作不在此范围内)。

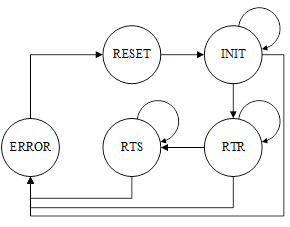

RoCE v2作为RoCE v2协议通信的重要机制,通常有五种队列工作状态,分别为:重置(RESET)状态、初始化(INIT)状态、接受就绪(Ready to Receive,RTR)状态、发送就绪(Ready to Send,RTS)状态及错误(ERROR)状态,其不同状态间的切换由RoCE v2队列状态机控制,RoCE v2队列状态机的状态转移图如图2所示

图2 RoCE v2队列状态转移图RESET状态:当队列处于RESET状态时,表示该QP已经创建但尚未完成初始化,在此状态下,QP既不能接收也不能发送任何数据请求,待初始化完成后会转至INIT状态。

INIT状态:队列处于INIT状态时,表示该QP已完成初始化,能够接收和发送请求。然而,在此状态下,队列只能接收Connect请求或发送Accept请求。

RTR状态:队列对处于RTR状态标识该队列对已经准备好接收Send请求(即进行Receive操作)和Read请求。

RTS状态:队列对处于RTS状态标识该队列对已准备好接收及发送任何RDMA请求,包括READ、WRITE、SEND、RECEIVE等。

ERROR状态:队列对处于ERROE状态标识该队列对已经发生错误,不再被使用,也不再接收或发送任何请求。该状态的产生原因可能为发送队列用尽、接收队列用尽、缓冲区不可读写等。

相关视频感兴趣者,请搜B站用户名: 专注与守望

或链接: