The RISC-V ecosystem is witnessing remarkable growth, driven by increasing industry adoption and a thriving open-source community. As companies and developers seek customizable computing solutions, RISC-V has become a top choice. Providing a scalable and cost-effective ISA foundation, RISC-V enables high-performance and security-enhanced implementations, making it ideal for next-generation digital infrastructure.

RISC-V's modular ISA and growing ecosystem support a wide range of configurations, making it highly adaptable across applications. Designers have options to integrate extensions such as vector processing, floating-point, atomic operations, and compressed instructions. Furthermore, its scalability spans from single-core to multi-core architectures and can incorporate optimizations like out-of-order execution to enhance performance. To achieve an optimal balance of performance, power efficiency, and scalability, selecting the right RISC-V microarchitecture and system integration strategy is crucial.

For entry-level RISC-V development , single-core open-source implementations are well-suited for small to medium capacity FPGA-based platforms. Among them, Xilinx VU9P-based solutions, such as the VCU118 development board, have been widely adopted by engineers for their balanced capabilities and accessibility. The S2C Prodigy S7-9P Logic System takes this foundation even further. Built on the same powerful VU9P FPGA with 14M ASIC gates, it enhances usability, expandability, and cost-efficiency. With seamless integration of daughter cards and an advanced toolchain , the S7-9P offers an ideal fit forsmall to medium-scale RISC-V designs, empowering developers to accelerate their innovation with confidence.

Media-Ready Prototyping: MIPI and HDMI for Real-World Applications

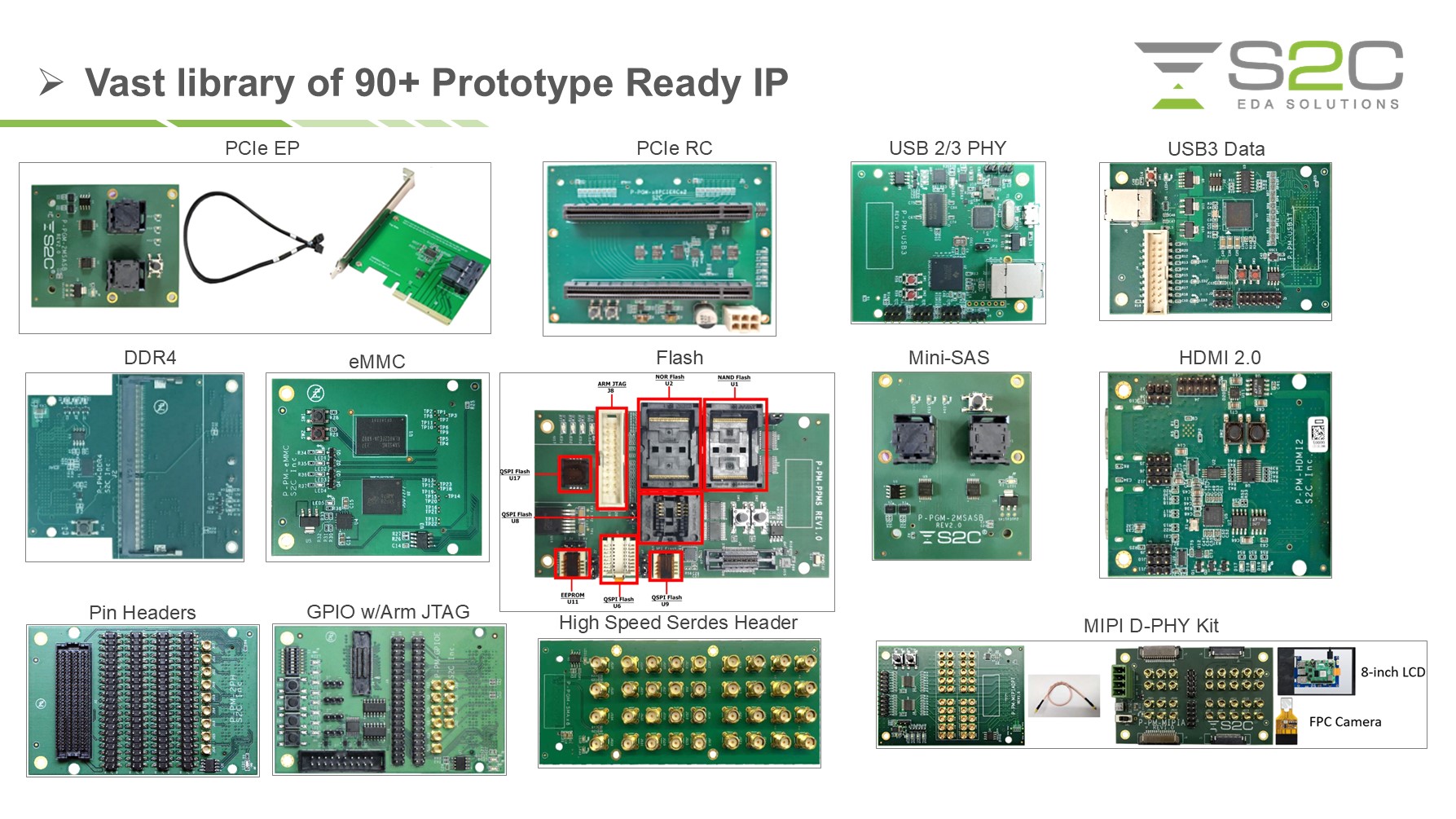

As multimedia processing becomes increasingly integral to RISC-V applications, the demand for high-speed data handling and versatile prototyping tools has never been greater. The S2C Prototyping systems meet this need with support for MIPI and HDMI via optional external daughter cards, making it an ideal choice for smart displays, AR/VR systems, and AI-powered cameras. For example, if you're developing a RISC-V-based smart camera, a complete prototyping environment from capturing images via MIPI D-PHY to display outputs through HDMI can be deployed with ease. Its flexible expansion options allow developers to experiment with various configurations, refine their designs, and push the boundaries of RISC-V media applications.

High-Speed Connectivity: QSFP28 Ethernet for Next-Gen Networking

With networking requirements becoming more demanding, high-speed connectivity is crucial for RISC-V-based applications. The S7-9P rises to this challenge with built-in QSFP28 Ethernet support, enabling 100G networking applications. This makes it an optimal choice for developing and testing prototyping RISC-V-based networking solutions, including routers, switches, and edge AI processing units.

Need More Scalability?

While the S7-9P is an excellent choice for entry-level to mid-range RISC-V prototyping, more complex designs may require greater capacity. For high-end verification and large-scale projects, S2C also offers advanced solutions like the VU440 (30M ASIC gates), VU19P (49M ASIC gates), and VP1902 (100M ASIC gates), providing the scalability needed for RISC-V subsystems, multi-core, AI, and data-intensive applications.

Special Offer: Save 25% on the Prodigy S7-9P Bundle

For a limited time, get the Prodigy S7-9P bundle ---which includes a free Vivado license (valued at 5,000+)** ---for just **14,995 , a 25% savings ! Visit S7-9P for information or Contact our team to find the perfect fit for your project.