在FPGA设计过程中,合理的引脚分配是确保硬件功能正确实现的关键步骤之一。Quartus II 提供了通过 TCL(Tool Command Language)脚本自动化引脚分配的功能,这不仅可以大大提高设计效率,还能够确保引脚分配的精确性和可重复性。本文将详细介绍如何在 Quartus II 中使用 TCL 文件进行引脚一键分配,提高设计流程的自动化程度。

1 导出tcl文件

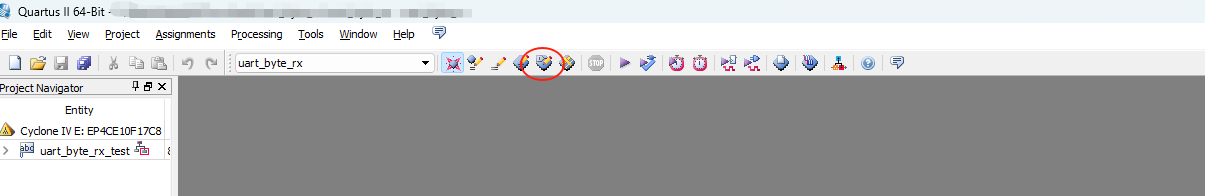

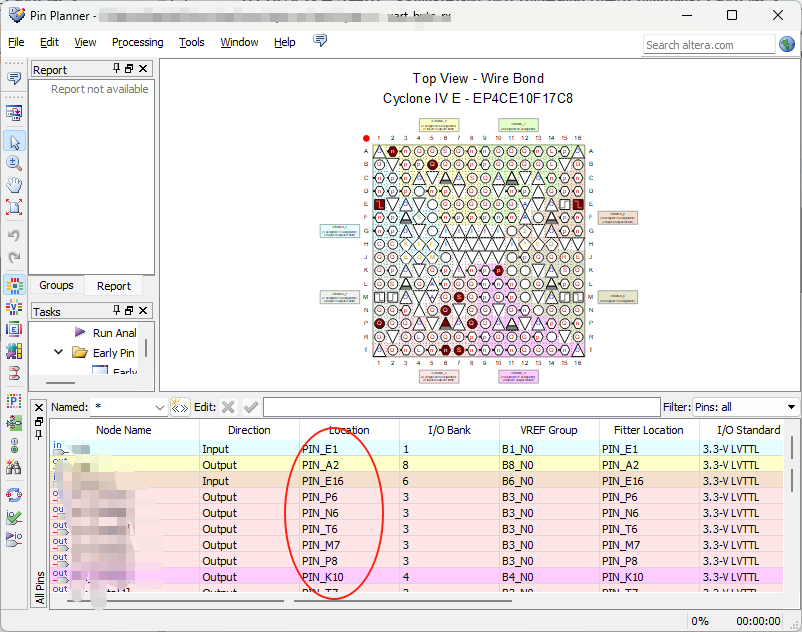

1.1 查看要导出的引脚

如下图所示,导出的引脚为下图所示的引脚:

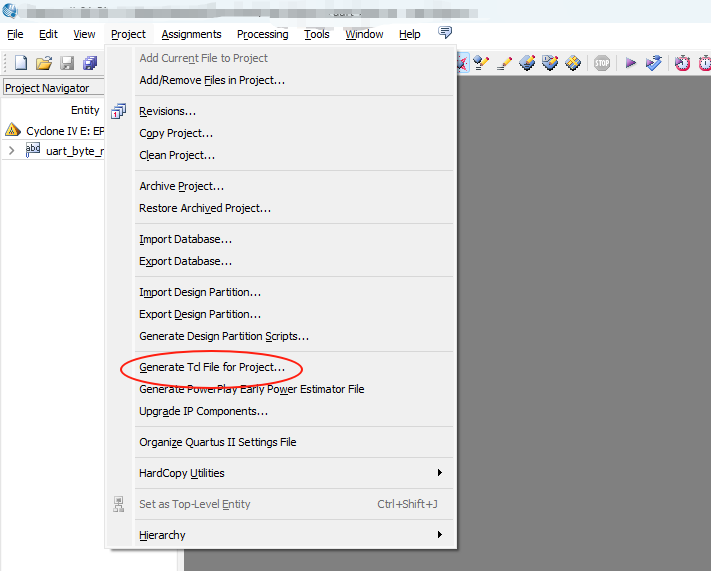

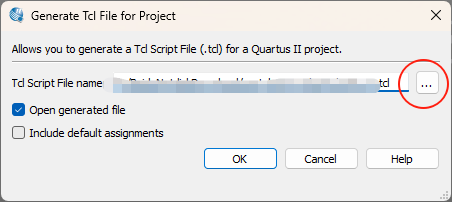

1.2 导出tcl文件步骤

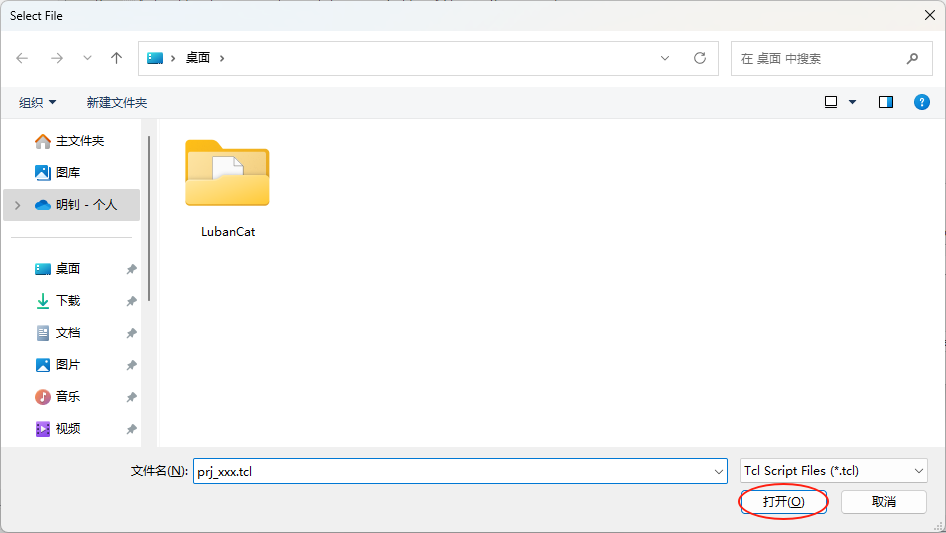

这里选择tcl保存位置:

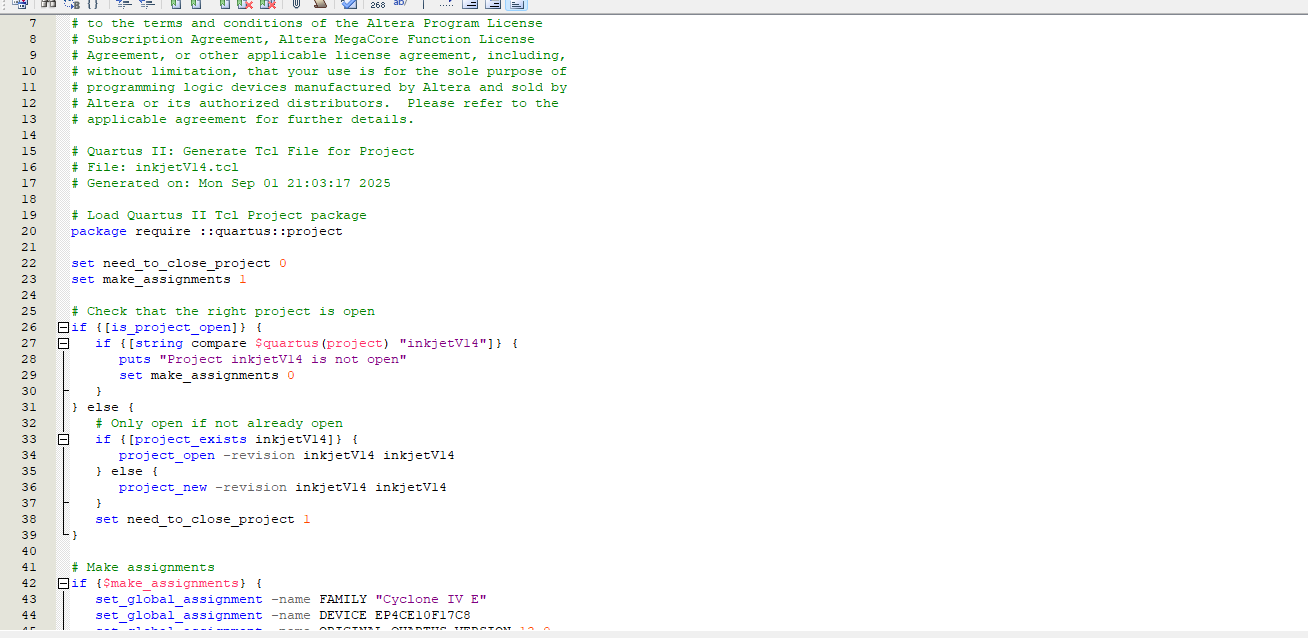

导出成功应该是这样的:

其实我们只需要自己需要的配置文件就可以了,比如只取set_location_assignment和set_instance_assignment:

tcl

set_location_assignment PIN_P3 -to EnPrint

set_location_assignment PIN_L7 -to PowerOn

set_location_assignment PIN_E1 -to in_clk

set_location_assignment PIN_M16 -to in_rst

set_location_assignment PIN_D3 -to inkjet_A1

set_location_assignment PIN_D1 -to inkjet_A2

set_location_assignment PIN_F5 -to inkjet_A3

set_location_assignment PIN_G2 -to inkjet_A4

set_location_assignment PIN_F3 -to inkjet_A5

set_location_assignment PIN_J6 -to inkjet_A6

set_location_assignment PIN_L4 -to inkjet_A7

set_location_assignment PIN_C2 -to inkjet_CE

set_location_assignment PIN_D5 -to inkjet_CK

set_location_assignment PIN_J1 -to inkjet_D1

set_location_assignment PIN_K1 -to inkjet_D2

set_location_assignment PIN_L1 -to inkjet_D3

set_location_assignment PIN_P2 -to inkjet_D4

set_location_assignment PIN_K2 -to inkjet_S1

set_location_assignment PIN_L2 -to inkjet_S2

set_location_assignment PIN_N2 -to inkjet_S3

set_location_assignment PIN_R1 -to inkjet_S4

set_location_assignment PIN_C3 -to inkjet_SH

set_location_assignment PIN_G1 -to inkjet_VL

set_location_assignment PIN_G5 -to inkjet_VPC

set_location_assignment PIN_K6 -to inkjet_VPK

set_instance_assignment -name IO_STANDARD "3.3-V LVTTL" -to EnPrint

set_instance_assignment -name IO_STANDARD "3.3-V LVTTL" -to PowerOn

set_instance_assignment -name IO_STANDARD "3.3-V LVTTL" -to in_clk

set_instance_assignment -name IO_STANDARD "3.3-V LVTTL" -to in_rst

set_instance_assignment -name IO_STANDARD "3.3-V LVTTL" -to inkjet_A1

set_instance_assignment -name IO_STANDARD "3.3-V LVTTL" -to inkjet_A2

set_instance_assignment -name IO_STANDARD "3.3-V LVTTL" -to inkjet_A3

set_instance_assignment -name IO_STANDARD "3.3-V LVTTL" -to inkjet_A4

set_instance_assignment -name IO_STANDARD "3.3-V LVTTL" -to inkjet_A5

set_instance_assignment -name IO_STANDARD "3.3-V LVTTL" -to inkjet_A6

set_instance_assignment -name IO_STANDARD "3.3-V LVTTL" -to inkjet_A7

set_instance_assignment -name IO_STANDARD "3.3-V LVTTL" -to inkjet_CE

set_instance_assignment -name IO_STANDARD "3.3-V LVTTL" -to inkjet_CK

set_instance_assignment -name IO_STANDARD "3.3-V LVTTL" -to inkjet_D1

set_instance_assignment -name IO_STANDARD "3.3-V LVTTL" -to inkjet_D2

set_instance_assignment -name IO_STANDARD "3.3-V LVTTL" -to inkjet_D3

set_instance_assignment -name IO_STANDARD "3.3-V LVTTL" -to inkjet_D4

set_instance_assignment -name IO_STANDARD "3.3-V LVTTL" -to inkjet_S1

set_instance_assignment -name IO_STANDARD "3.3-V LVTTL" -to inkjet_S2

set_instance_assignment -name IO_STANDARD "3.3-V LVTTL" -to inkjet_S3

set_instance_assignment -name IO_STANDARD "3.3-V LVTTL" -to inkjet_S4

set_instance_assignment -name IO_STANDARD "3.3-V LVTTL" -to inkjet_SH

set_instance_assignment -name IO_STANDARD "3.3-V LVTTL" -to inkjet_VL

set_instance_assignment -name IO_STANDARD "3.3-V LVTTL" -to inkjet_VPC

set_instance_assignment -name IO_STANDARD "3.3-V LVTTL" -to inkjet_VPK

set_instance_assignment -name IO_STANDARD "3.3-V LVTTL" -to temp_clk1.3 tcl语法介绍

-

set_location_assignment

功能:该命令用于将特定的逻辑元素(如FPGA中的输入/输出引脚、存储器块等)分配到特定的物理位置(引脚、块)上。

语法:set_location_assignment location -to instance

location: 指定要分配的物理位置(例如,具体的引脚编号)。

instance: 指定要进行位置分配的设计实例或信号。用途:通常用于在FPGA设计中强制特定的模块或引脚占用特定的硬件位置,确保信号的正确路由和时序要求。通过合理的引脚分配,可以减少信号延迟和电路拥塞。

-

set_instance_assignment

功能:该命令用于设置特定实例的属性或约束,可能包括配置信息、实现方式或特定的制造工艺选择。

语法:set_instance_assignment property value -to instance

property: 指定要设置的属性,例如速度等级、功耗模式等。

value: 给定属性的值,例如可以是"FAST"或"SLOW"等。

instance: 指定要更改属性的设计实例。

2 导入tcl文件

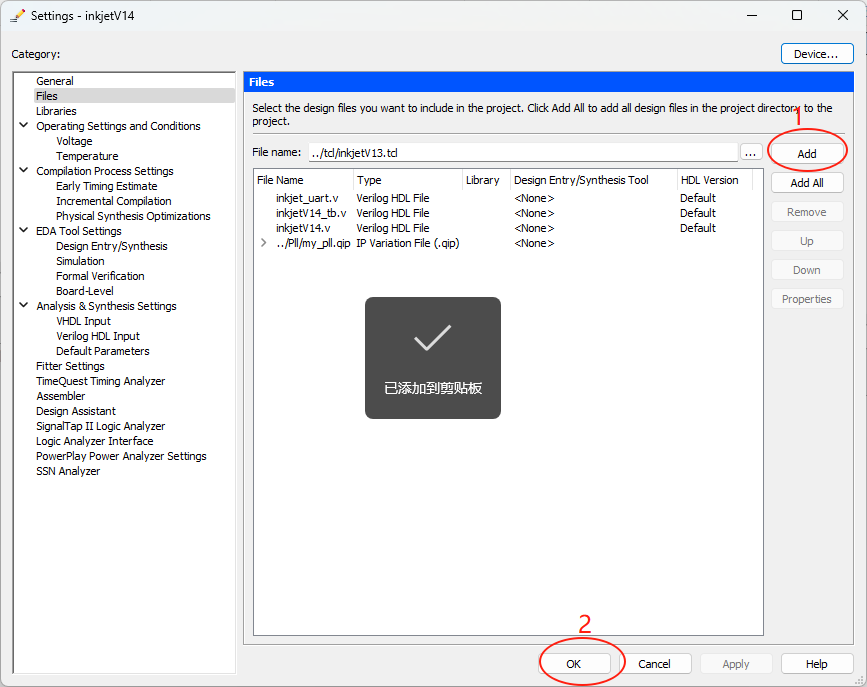

2.1 将tcl文件添加到项目里

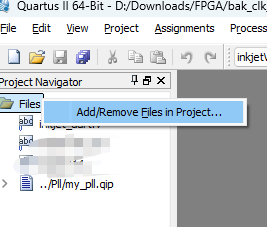

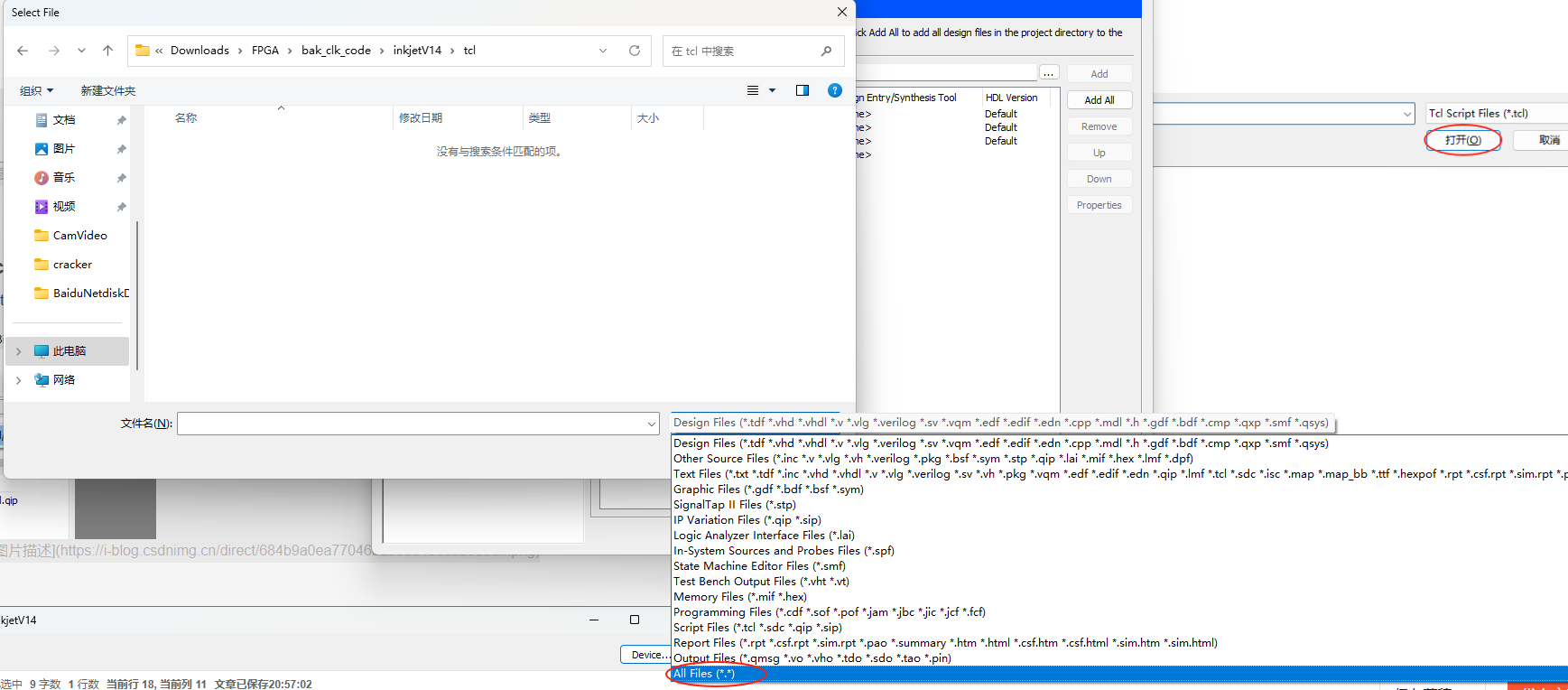

这里右键添加tcl文件到项目里面

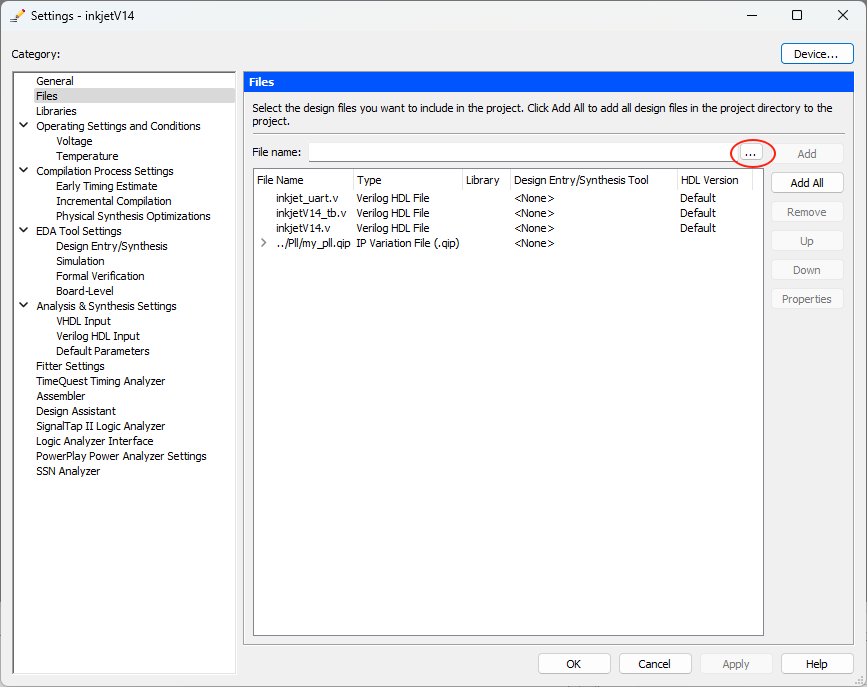

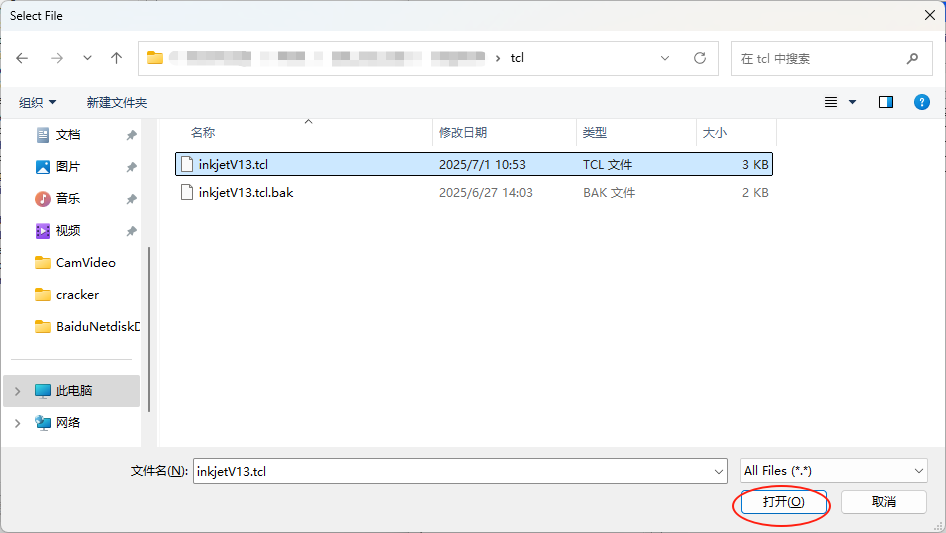

这里选择tcl所在位置

这里一定要选add,不然添加不进去。

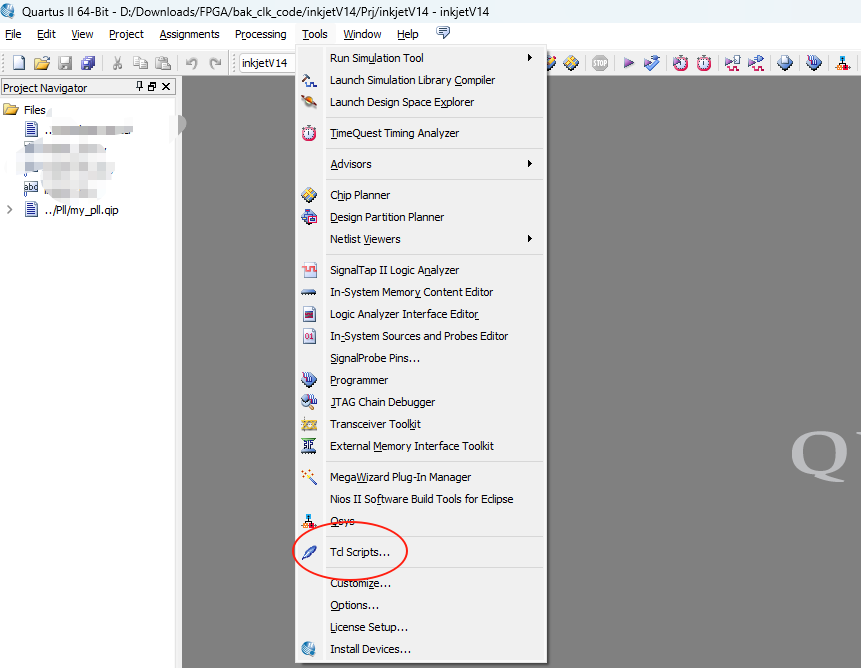

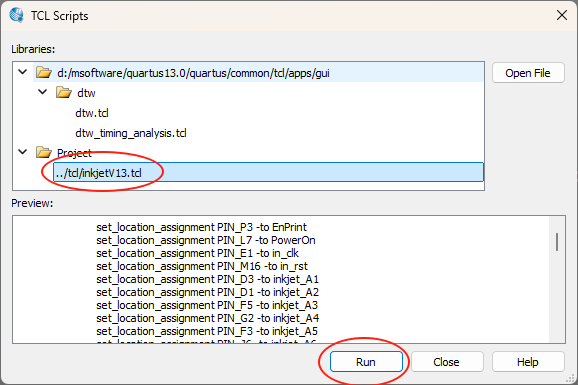

2.2 运行tcl文件

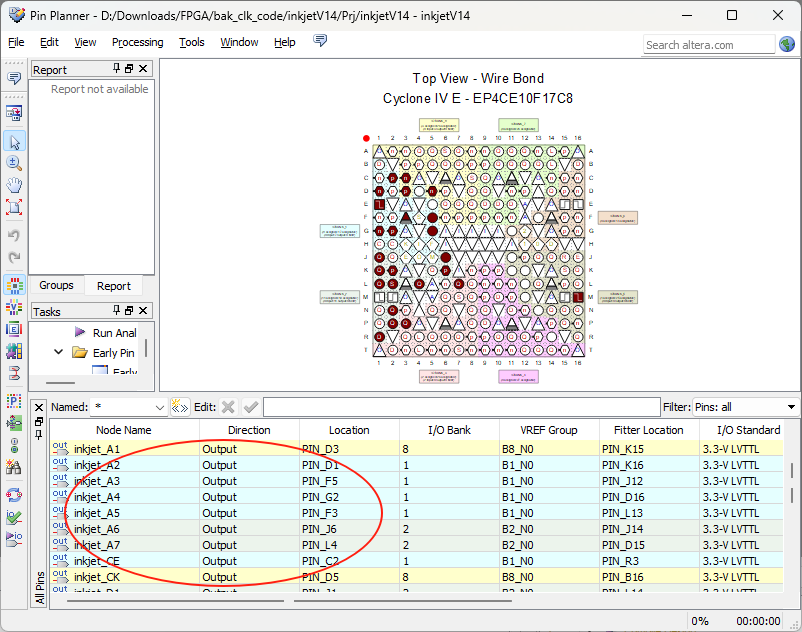

这里就表示已经将tcl文件设置完成,可以直接查看:

总结

在FPGA设计过程中,合理的引脚分配至关重要,它确保了硬件功能的正确实现。使用TCL脚本进行引脚分配不仅节省了手动配置的时间,还减少了人为错误的风险,使得设计流程更加流畅。通过设置具体的引脚位置和实例属性,可以快速实现符合设计需求的配置。组合set_location_assignment和set_instance_assignment等命令,我可以有条不紊地管理引脚和实例,确保逻辑与物理的有效匹配。