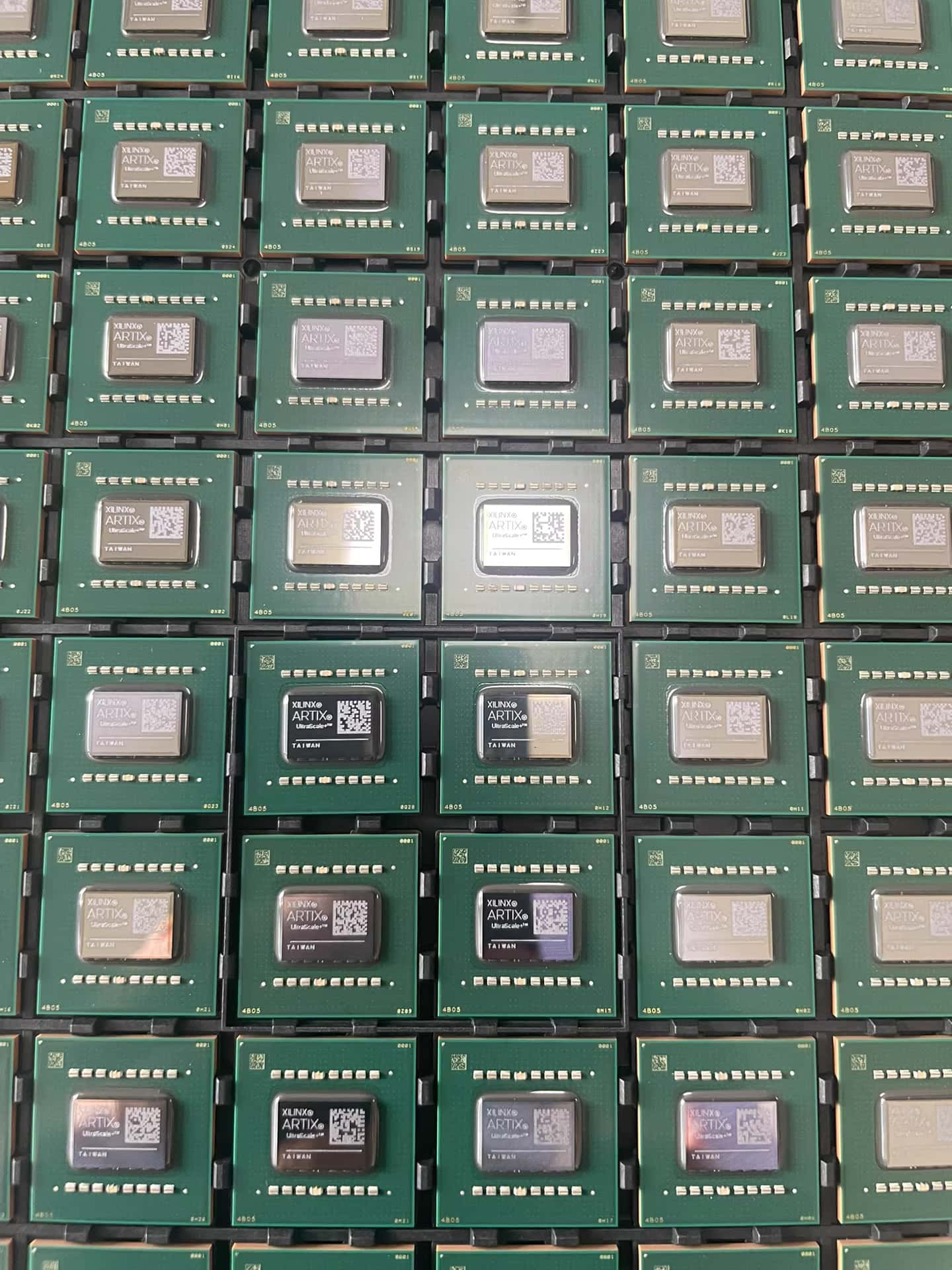

XCAU10P-2SBVB484I 属于 赛灵思 Xilinx 的 Artix UltraScale+ 系列 FPGA。料号中 "10P" 表示该器件在系列中的容量/等级,后缀 "-2" 为速度等级,封装代码 SBVB484 指示 484-ball BGA 类封装变体,末尾 "I" 表示工业温度等级。该系列采用 UltraScale+/16nm 级别的架构设计,目标在于用尽可能低的功耗提供较高的 DSP 与 I/O 带宽,适合机器视觉、低功耗网络设备、4K 视频接口和边缘计算等场景。

XCAU10P 的器件级资源体现为大量的自适应逻辑模块(ALM/LE)和块型片上 RAM,以及面向信号处理的 DSP 切片。常见产品表显示该器件的逻辑规模约 96,250 个逻辑单元(LE)/约 5,500 个 ALM ,片上嵌入式存储大约 3.5 Mbit,这些资源使其能够承载中等到较大规模的并行算子、FIFO/缓存与 DSP 数据通路。器件内部的 ALM 可将 LUT 用作分布式 RAM 或移位寄存器,以提升灵活性与资源利用率。

SBVB484 封装(484-ball BGA)通常能提供约 200 左右的用户 I/O 引脚 (因封装和引脚分配不同而异,某些变体在文档中列出 204 个 I/O 等近似值),器件需要多电源域管理(包含 VCCINT、VCCAUX、VCCO 各 bank、BRAM/VREF 等),典型核心供电约 0.85 V 量级(示例范围约 0.825--0.876 V,根据速率档与器件修订略有差异),工作结温适配工业级窗口(例如 -40°C 到 +100°C TJ)。

该器件在家族层面支持若干高速串行收发器(transceiver),目标变体通常集成 12 条左右的收发通道 ,单通道速率规格在产品表中常见到 可支持到 12.5 Gb/s 等级(具体上限受封装、速度等级与 PCS/PMA 配置影响)。器件内部还包含多路时钟管理单元(MMCM/PLL 或等效模块)用于相位/频率合成与低抖动时钟分配,设计高速链路时需提供合适的参考时钟源、串扰/差分阻抗控制以及均衡/预失真设置以保证链路稳定。

赛灵思 Xilinx 的 Artix UltraScale+ 系列其他型号选型:

XCAU10P-2UBVA368I XCAU10P-1UBVA368I

XCAU10P-1FFVB676E XCAU10P-L1SBVB484I

XCAU15P-2FFVB676I XCAU10P-1FFVB676I

XCAU25P-2FFVB676E XCAU25P-1SFVB784I

XCAU10P-2FFVB676I XCAU15P-1SBVB484E

XCAU15P-2SBVB484I XCAU10P-1UBVA368E

XCAU10P-1SBVB484I XCAU20P-2FFVB676I

XCAU25P-2SFVB784I XCAU20P-2SFVB784I

XCAU10P-2SBVB484I XCAU20P-1SFVB784E

XCAU15P-1FFVB676E XCAU20P-1FFVB676E

XCAU10P-2FFVB676E XCAU20P-2FFVB676E

XCAU15P-2SBVB484E XCAU15P-1SBVB484I

XCAU25P-2FFVB676 XCAU10P-L1UBVA368I

XCAU25P-L1FFVB676I XCAU10P-2UBVA368E

XCAU25P-1FFVB676E XCAU15P-1UBVA368E

XCAU25P-2FFVB676I XCAU25P-1SFVB784E

XCAU25P-1FFVB676I XCAU7P-2SBVC484I

XCAU10P-L1FFVB676I XCAU20P-1SFVB784I

XCAU15P-2FFVB676E XCAU20P-2SFVB784E

XCAU15P-1FFVB676I XCAU20P-L1FFVB676I

XCAU15P-L1FFVB676I XCAU20P-L1SFVB784I

XCAU10P-1SBVB484E XCAU25P-L1SFVB784I

XCAU10P-2SBVB484E XCAU25P-2SFVB784E

XCAU20P-1FFVB676I XCAU15P-1UBVA368I