目录

[一、ICG 是什么?](#一、ICG 是什么?)

[二、ICG 的工作原理](#二、ICG 的工作原理)

[ICG 的做法是:](#ICG 的做法是:)

[三、ICG 的电路结构(为什么不用 AND)](#三、ICG 的电路结构(为什么不用 AND))

[四、ICG 和 RTL 写法的关系](#四、ICG 和 RTL 写法的关系)

[五、ICG 在 Design Compiler 中如何使用](#五、ICG 在 Design Compiler 中如何使用)

[1. 启用 ICG 插入逻辑](#1. 启用 ICG 插入逻辑)

[2. 设置插入条件](#2. 设置插入条件)

[3. 编译时允许插入 gating](#3. 编译时允许插入 gating)

[六、PrimeTime 中的 ICG 时序分析](#六、PrimeTime 中的 ICG 时序分析)

[1. gating enable → clock gating cell enable pin](#1. gating enable → clock gating cell enable pin)

[2. gated_clk → 寄存器 clk pin](#2. gated_clk → 寄存器 clk pin)

[3. glitch check(可选)](#3. glitch check(可选))

一、ICG 是什么?

ICG,全称 Integrated Clock Gating Cell,中文叫"集成时钟门控单元"。

它的作用就是:

用一个专门的逻辑单元,在 时钟信号(clk)传播到寄存器之前进行"选择"或"屏蔽" ,从而在不需要时钟切换的周期里,阻止不必要的时钟信号传播,降低功耗。

二、ICG 的工作原理

最基本的时钟 gating 思想就是下面这个逻辑:

gclk = clk & en;就是说:

-

当 enable(en)为 1,时钟 clk 正常传入 → gated_clk = clk

-

当 en 为 0,时钟 clk 被屏蔽 → gated_clk = 0,不再切换

ICG 是专门用来节省时钟功耗的逻辑。

比如下面的例子:

reg q;

always @(posedge clk)

if (en)

q <= d;意思是:只有在 en 为 1 的时候,才存数据

但这里写的是 if (en),时钟其实还是每次都在来,功耗没减少。

ICG 的做法是:

让时钟在 en == 0 时完全不进来,用一个门控逻辑把时钟挡住:

clk ──┬──▶ AND ──▶ gated_clk ──▶ FF

│

en等价于:"en 不开门,时钟进不来,FF 就不切换,也就不耗电。"

这样,寄存器不会在不需要的时候被触发,可以极大地节省动态功耗(尤其是在时钟功耗占比很高的芯片中,节能效果显著)。

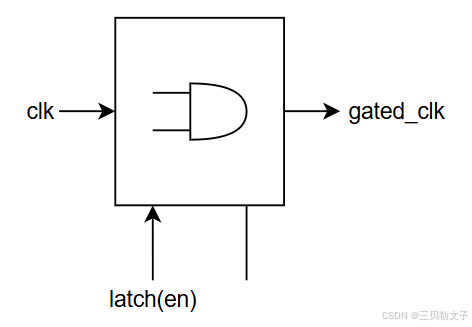

三、ICG 的电路结构(为什么不用 AND)

虽然 gclk = clk & en 是直觉的写法,但电路上绝不能直接使用 AND 门做 gating!

原因:

-

当

en是组合信号或变化过快,会导致时钟线上产生 glitch(毛刺) -

时钟毛刺会误触发 flip-flop,导致功能错误,非常危险

正确做法:使用 专门的 ICG 单元(一般是 standard cell 库中提供)

通用结构:

module ICG (

input wire clk,

input wire en, // clock enable

output wire gclk // gated clock

);电路内部(大多数 ICG 用 latch + AND):

-

en 先经过 latch 保持稳定(避免 glitch)

-

latch 的输出再控制 AND 门

这个结构可以保证en 的变化不会立即影响 clk,从而避免毛刺。

四、ICG 和 RTL 写法的关系

在你的 RTL 中,只要你写出如下结构:

always @(posedge clk)

if (en)

q <= d;Design Compiler 会尝试识别 en 是 clock gating candidate,然后把时钟 gating 出去,变成:

wire gated_clk = ICG(clk, en);

always @(posedge gated_clk)

q <= d;但请注意:不是所有 if (en) 都能做 clock gating。必须满足以下条件:

ICG 插入的条件

-

en是稳态(寄存器输出)或信号稳定 -

en与多个寄存器共用(有 fanout) -

时序允许 insert gating delay

-

工具启用了 gating(DC 默认可控制)

五、ICG 在 Design Compiler 中如何使用

在 Synopsys Design Compiler 中,你可以通过如下指令控制 ICG 插入:

1. 启用 ICG 插入逻辑

set_clock_gating_style -positive_edge -sequential latch -control_point before说明:

-

-sequential latch:使用 latch 结构来控制 gating enable -

-control_point before:在寄存器前控制时钟

2. 设置插入条件

set_clock_gating_check -clock_gating_hold_check enable确保插入 ICG 的地方能满足 hold check(DC 会自动计算)

3. 编译时允许插入 gating

compile_ultra -gate_clock或在 compile 中加上:

set_app_var power_cg_auto_insert true六、PrimeTime 中的 ICG 时序分析

当你插入了 ICG,PrimeTime 会自动识别 gating cell,并做以下几个路径分析:

1. gating enable → clock gating cell enable pin

要确保 en 足够早地达到 gating cell,防止 gating cell 还没打开时钟就来了。

2. gated_clk → 寄存器 clk pin

要分析 gated 时钟经过 gating cell 后的 delay + skew

3. glitch check(可选)

用

check_clock_gating检查 gating cell 的 glitch 可能性

七、真实项目使用举例

你写的 RTL:

module example (

input clk,

input en,

input [7:0] d,

output reg [7:0] q

);

always @(posedge clk)

if (en)

q <= d;

endmodule设计目标:功耗低

综合脚本设置:

set_clock_gating_style -positive_edge -sequential latch

set_clock_gating_check -clock_gating_hold_check enable

compile_ultra -gate_clock综合后结果:

-

DC 识别了 en 是 gating 控制信号

-

插入了一个 gating cell(如 ICG_X1)

-

原始的 8 个 FF 用 gated clk 驱动

-

如果你启用了 multi-bit FF,还会把 q[7:0] 合并成一个 8-bit FF

八、常见问题与误区

| 问题/误区 | 说明与解决 |

|---|---|

en 是组合逻辑 |

可能导致 glitch,不能用于 gating |

| 用 AND/OR 代替 gating | 不能保证无 glitch,设计不安全 |

| gating 造成 hold 问题 | 使用 set_clock_gating_check 验证 |

| ICG fanout 太大 | 要手动 balance,防止 skew 大 |

| 多级 ICG(ICG → ICG) | 一般不建议,多级容易造成调试困难 |

总结一句话

ICG 是在时钟进入寄存器之前"加开关",只有当使能信号有效的时候才让时钟进去,从而避免时钟功耗白白浪费,是 RTL → GATE 低功耗设计的必备武器。