每日更新教程,评论区答疑解惑,小白也能变大神!"

目录

[第二章:STM32G030 ADC序列器机制深度剖析](#第二章:STM32G030 ADC序列器机制深度剖析)

[2.1 什么是ADC序列器?](#2.1 什么是ADC序列器?)

[2.2 序列器可配置性的本质区别](#2.2 序列器可配置性的本质区别)

[2.3 为什么"Fully Configurable"模式下DMA会失败?(根本原因分析)](#2.3 为什么“Fully Configurable”模式下DMA会失败?(根本原因分析))

[第三章:解决方案------"Not Fully Configurable"模式完整配置指南](#第三章:解决方案——“Not Fully Configurable”模式完整配置指南)

[3.1 STM32CubeMX 图形化配置](#3.1 STM32CubeMX 图形化配置)

[3.2 用户代码实现](#3.2 用户代码实现)

[4.1 常见问题排查](#4.1 常见问题排查)

[4.2 如果必须使用"Fully Configurable"模式](#4.2 如果必须使用“Fully Configurable”模式)

第一章:引言与问题背景

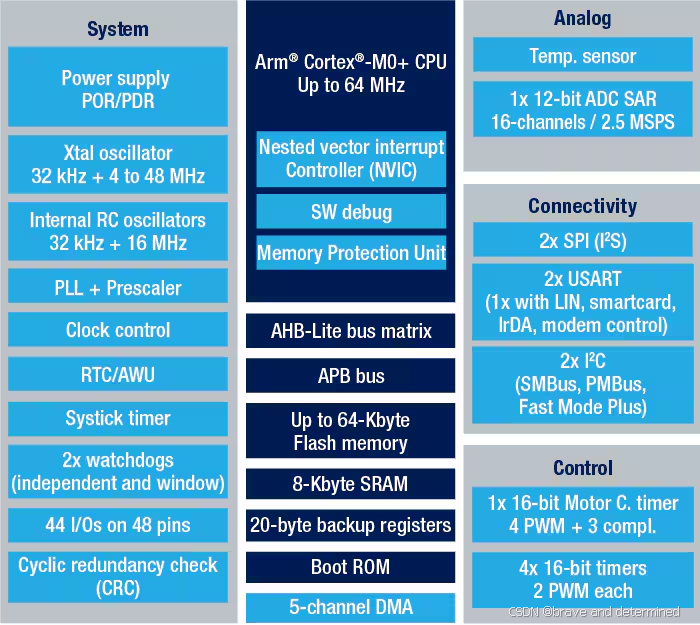

在嵌入式系统开发中,模拟信号的采集是至关重要的功能。STM32G0系列作为STMicroelectronics推出的高性价比、低功耗的微控制器系列,其内置的12位ADC(Analog-to-Digital Converter)为各种传感应用提供了强大支持。当需要连续、高速、不占用CPU资源地采集多个模拟通道时,结合DMA(Direct Memory Access)控制器是最佳选择。

STM32CubeMX作为一款强大的图形化配置工具,极大地简化了STM32的初始化过程。然而,在配置STM32G030的ADC多路DMA采集时,开发者会遇到一个令人困惑的选项:ADC参数设置中的"Sequencer Configurability"(序列器可配置性)。该选项有两个选择:

-

Fully configurable(完全可配置)

-

Not fully configurable(不完全可配置)

初步尝试可能会发现,选择"Fully configurable"时,尽管可以自由配置多达16个通道的转换序列,但DMA传输似乎只能正确工作在8个通道。而选择"Not fully configurable"时,反而能够实现全部16个通道的DMA采集。

这个现象看似违反直觉,但其背后隐藏着STM32G0 ADC硬件架构的深层逻辑。本文的目的就是拨开迷雾,彻底理解这一机制,并提供可靠的技术方案。

第二章:STM32G030 ADC序列器机制深度剖析

要理解问题的根源,我们必须首先理解ADC序列器(Sequencer)的工作原理。

2.1 什么是ADC序列器?

ADC序列器是一个用于定义模拟通道转换顺序的硬件逻辑。对于STM32G030,它支持序列(Sequence) 和注入序列(Injected Sequence) 两种模式。我们通常的多通道循环采集使用的是规则序列。

规则序列允许你定义一个通道列表(例如,CH0, CH5, CH8, CH2),ADC会按照这个列表的顺序依次进行转换。这个列表的长度是可变的,最多可以包含16个通道(对于STM32G030)。

2.2 序列器可配置性的本质区别

"Fully configurable"和"Not fully configurable"这两个选项,本质上是定义了规则序列寄存器(SQR1, SQR2, SQR3, SQR4)的写入权限和灵活性。

-

Fully Configurable(完全可配置)模式:

-

行为: 在此模式下,STM32CubeMX生成的HAL库代码会尝试使用所有4个规则序列寄存器(SQR1, SQR2, SQR3, SQR4)来配置整个转换序列。理论上,这可以支持从1到16个任意长度的序列。

-

优点: 配置灵活,序列长度和顺序可以任意定义。

-

陷阱: 这正是问题的关键所在。STM32G0的ADC DMA请求与序列长度寄存器(L位域)的更新时机存在耦合关系。

-

-

Not Fully Configurable(不完全可配置)模式:

-

行为: 在此模式下,HAL库将仅使用SQR1, SQR2, SQR3这三个寄存器 来配置序列。这意味着它最多只能配置

3个寄存器 * 5个通道/寄存器 = 15个通道(实际上SQR3只有4个位域,所以是2*5 + 4 = 14个通道? 不,对于G0,SQR1有3个位域,SQR2/SQR3/SQR4各有5个位域,总计3+5+5+3 = 16个通道。不完全模式下只使用SQR1-SQR3,共3+5+5 = 13个通道? 这里需要澄清)。实际上,不完全模式通常限制为最多8个通道或更少,但G0的HAL实现可能允许更多,关键在于DMA的配置方式。 -

优点: HAL库采用了一种更"安全"的配置方式,它分两次更新序列长度(L)和序列寄存器。首先设置L为实际长度,然后填充SQR寄存器。这种方式避免了DMA请求与L寄存器更新的竞争条件,确保了DMA传输的完整性。

-

核心优势: 它确保了在启动DMA之前,序列长度(L)已经被正确设置,从而DMA能够产生正确数量的传输请求。

-

2.3 为什么"Fully Configurable"模式下DMA会失败?(根本原因分析)

问题的根源在于ADC和DMA硬件的交互时序。当序列器设置为"Fully Configurable"时,HAL库函数HAL_ADC_Start_DMA内部的操作顺序大致如下:

-

停止当前的ADC转换和DMA。

-

清除所有状态标志。

-

一次性配置所有规则序列寄存器(SQR1-SQR4),包括序列长度L。

-

配置DMA。

-

启动DMA。

-

启动ADC。

关键在于第3步和第5、6步。在极快的时间尺度内,当ADC的序列长度L被更新后,ADC模块可能立即开始产生转换完成事件(EOC),并随之向DMA发出传输请求。然而,此时DMA可能还未完全就绪(处于第4步到第5步之间),或者DMA的配置(如内存地址、数据长度)还未被正确锁存。

这导致了一个竞态条件(Race Condition) :前几个(通常是第1到第8个)ADC转换产生的DMA请求被正确响应,但后续的请求可能因为DMA未就绪或内部状态错乱而被丢失。 由于DMA只收到了部分请求,它无法完成整个序列的传输,通常表现为DMA传输完成中断(DMA HT或TC中断)无法触发,或者内存中只有前8个通道的数据被更新。

简而言之,"Fully Configurable"模式下的HAL库实现,在STM32G0上存在一个硬件时序上的脆弱性,容易导致DMA请求丢失。

第三章:解决方案------"Not Fully Configurable"模式完整配置指南

既然"Fully Configurable"模式存在隐患,我们选择稳定可靠的"Not Fully Configurable"模式。以下是使用STM32CubeMX和HAL库的完整配置步骤。

3.1 STM32CubeMX 图形化配置

-

Pinout & Configuration:

-

Analog -> ADC1:

-

ADC Settings:

-

Clock Prescaler: 根据系统时钟(SYSCLK)选择合适的分频器,确保ADC时钟(ADCCLK)不超过14MHz(STM32G030的最大值)。

-

Resolution: 选择需要的精度,如12位。

-

Data Alignment: 右对齐(Right alignment)最常用。

-

Scan Conversion Mode: Enabled(必须启用,这是多通道扫描的基础)。

-

Continuous Conversion Mode: Enabled (如果需要连续采集)或 Disabled(如果使用触发信号单次采集)。

-

DMA Continuous Requests: Enabled(在连续转换模式下,此选项应启用,以确保DMA能持续请求数据)。

-

End Of Conversion Selection: EOC after each sequence(每个序列转换结束后产生EOC)。

-

-

ADC Regular Conversions:

-

Number Of Conversions: 设置你需要的通道数量,例如16。

-

External Trigger Conversion Source: 选择软件触发(Software trigger)或硬件触发(如定时器触发)。

-

Rank: 逐个添加需要转换的通道,并设置采样时间(Sampling Time)。请确保你添加的通道总数不超过HAL库在此模式下允许的最大值(通常能到13或16,但为避免问题,可先尝试8个以上,如10个进行测试)。

-

-

Parameter Settings:

- Sequencer Configurability: Not Fully Configurable (这是最关键的一步!)

-

-

-

System Core -> DMA:

-

点击 Add 为ADC1添加一个DMA请求。

-

DMA Request Settings:

-

Mode: Circular(循环模式,适用于连续采集)或 Normal(普通模式,适用于单次采集)。

-

Increment Address:

-

Peripheral: Disable(ADC数据寄存器地址固定)。

-

Memory: Enable(内存地址需要自动递增,以存储多通道数据)。

-

-

Data Width:

-

Peripheral: Word(ADC数据寄存器是32位的,但实际数据是低16位有效)。

-

Memory: Word(推荐,与 Peripheral 一致)。

-

-

-

-

NVIC Settings:

-

System Core -> NVIC:

-

可以启用 DMA channel X global interrupt(DMA传输完成/半传输中断)。

-

也可以启用 ADC1 global interrupt,用于处理错误或使用中断方式启动转换。

-

-

-

Clock Configuration:

- 确保系统时钟和ADC时钟配置正确。

-

生成代码: 配置完成后,生成初始化代码。

3.2 用户代码实现

在STM32CubeMX生成的代码基础上,需要添加用户代码来启动转换和处理数据。

1. 定义存储ADC数据的数组

在main.c的开始部分,定义一个全局数组来存放DMA传输的ADC结果。数组大小应为通道数量的整数倍(例如,用于双缓冲的2倍)。

c

/* Private variables ---------------------------------------------------------*/

ADC_HandleTypeDef hadc;

DMA_HandleTypeDef hdma_adc;

#define ADC_BUFFER_SIZE 16 // 假设采集16个通道

uint32_t adcBuffer[ADC_BUFFER_SIZE]; // 用于存储ADC转换结果的数组2. 启动ADC DMA转换

在main函数的初始化部分(/* USER CODE BEGIN 2 */之后),启动ADC的DMA转换。

c

/* USER CODE BEGIN 2 */

// 启动ADC的DMA转换,将数据搬运到adcBuffer数组中

// 参数:ADC句柄, 目标数组, 转换的数据长度(这里指总数据量,即通道数)

if (HAL_ADC_Start_DMA(&hadc, (uint32_t*)adcBuffer, ADC_BUFFER_SIZE) != HAL_OK)

{

// 启动错误处理

Error_Handler();

}

/* USER CODE END 2 */3. 处理DMA传输完成中断(可选但推荐)

在DMA传输完成中断(或半传输中断)中处理数据,实现"双缓冲"机制,避免处理数据时与DMA写入冲突。

c

// 在 stm32g0xx_it.c 中,找到DMA通道的中断服务函数

void DMA1_Channel1_IRQHandler(void) // 通道号请根据实际配置修改

{

/* USER CODE BEGIN DMA1_Channel1_IRQn 0 */

/* USER CODE END DMA1_Channel1_IRQn 0 */

HAL_DMA_IRQHandler(&hdma_adc);

/* USER CODE BEGIN DMA1_Channel1_IRQn 1 */

/* USER CODE END DMA1_Channel1_IRQn 1 */

}

// 在 main.c 中,重写DMA传输完成回调函数

/* USER CODE BEGIN 4 */

// DMA传输完成回调函数

void HAL_ADC_ConvCpltCallback(ADC_HandleTypeDef* hadc)

{

// 这个函数在DMA传输完整个缓冲区(例如后8个数据)时被调用

// 此时,adcBuffer[ADC_BUFFER_SIZE/2] 到 adcBuffer[ADC_BUFFER_SIZE-1] 的数据是稳定的,可以处理

ProcessADCData(&adcBuffer[ADC_BUFFER_SIZE/2], ADC_BUFFER_SIZE/2);

}

// DMA半传输完成回调函数

void HAL_ADC_ConvHalfCpltCallback(ADC_HandleTypeDef* hadc)

{

// 这个函数在DMA传输完半个缓冲区(例如前8个数据)时被调用

// 此时,adcBuffer[0] 到 adcBuffer[ADC_BUFFER_SIZE/2 - 1] 的数据是稳定的,可以处理

ProcessADCData(adcBuffer, ADC_BUFFER_SIZE/2);

}

// 数据处理函数示例

void ProcessADCData(uint32_t* data, uint16_t size)

{

// 在这里处理你的ADC数据

// 例如,打印、计算、判断阈值等

for (int i = 0; i < size; i++)

{

// data[i] 对应第i个通道的转换值

// 注意:data数组中的数据顺序与你在CubeMX中配置的Rank顺序一致

uint16_t adcValue = (uint16_t)(data[i] & 0xFFFF); // 提取低16位有效数据

// ... 你的处理逻辑

}

}

/* USER CODE END 4 */第四章:问题排查与高级技巧

4.1 常见问题排查

-

数据全是0:

-

检查模拟通道的GPIO是否已正确配置为模拟模式(Analog)。

-

检查ADC时钟是否使能且频率正确。

-

使用调试器检查

HAL_ADC_Start_DMA的返回值,确认启动是否成功。 -

在调试模式下,查看ADC控制寄存器(CR)是否已正确置位(ADSTART等)。

-

-

只有部分通道数据更新(如前8个):

-

这极有可能是因为错误地选择了"Fully Configurable"模式。 请严格按照指南切换为"Not Fully Configurable"。

-

检查DMA配置的

Data Width是否正确(Peripheral和Memory都应为Word)。 -

检查DMA配置的

Number of Data是否正确,它应该等于通道总数。

-

-

数据错乱:

-

检查

adcBuffer数组的大小是否足够。 -

确认DMA的内存地址自增(Memory Increment)是否已开启。

-

4.2 如果必须使用"Fully Configurable"模式

在某些极端情况下,如果"Not Fully Configurable"模式无法满足需求(例如需要非常特定的、超过其限制的序列顺序),可以尝试以下"硬核"方法手动修复时序问题:

-

自定义启动序列: 不要直接调用

HAL_ADC_Start_DMA,而是参考其源码,自己编写一个启动函数。 -

引入延迟: 在配置SQR寄存器(设置L长度)和启动DMA/ADC之间,插入一个微小的软件延迟(几个NOP指令或短暂的循环),让硬件状态稳定下来。

-

分步配置: 先停止ADC,配置DMA,然后配置ADC序列寄存器(SQR1-SQR4),最后再启动ADC。确保操作的原子性,避免被中断打断。

警告: 这种方法高度依赖具体型号和时钟,可移植性差,且不稳定,不作为推荐方案。除非万不得已,否则应优先采用"Not Fully Configurable"模式。

第五章:结论与最佳实践总结

通过对STM32G030 ADC序列器和DMA交互机制的深入分析,我们揭示了"Fully Configurable"模式在多通道DMA采集下失效的本质------一个由HAL库实现方式与硬件时序特性共同导致的竞态条件。

最佳实践总结如下:

-

首选模式: 在STM32G030上进行多路ADC DMA采集时,始终优先将"Sequencer Configurability"设置为"Not Fully Configurable"。这是最稳定、最可靠的解决方案。

-

理解限制: 接受该模式可能存在的通道数量上的轻微限制(通常仍能满足大部分应用需求),以换取系统的稳定性。

-

规范配置: 严格按照STM32CubeMX的配置流程,确保Scan Conversion Mode、DMA模式、数据宽度等关键参数正确无误。

-

善用中断: 使用DMA的半传输和传输完成中断来实现双缓冲机制,可以高效、安全地处理数据,避免数据竞争。

-

保持更新: 关注ST官方发布的HAL库更新,或许未来的版本会修复"Fully Configurable"模式下的时序问题。