《FPGA基础知识》系列导航

本专栏专为FPGA新手打造的Xilinx平台入门指南。旨在手把手带你走通从代码、仿真、约束到生成比特流并烧录的全过程。

本篇是该系列的第二十篇内容

上一篇:FPGA基础知识(十九):Xilinx Block Memory IP核(4)--True Dual Port RAM 详解-CSDN博客

下一篇:关注我,第一时间获取更新!!

大家好,今天我们来分享block Memory Generate的最后一个知识点:ROM,说起ROM,主要是为了将我们提前写好的数据文件,作为源数据,导入FPGA,作为后续使用的。

这个ROM我之前的使用场景是用来存储 仿真好的移相器的参数用作相控阵雷达的俯仰角控制的,ROM最重要的是.coe文件的文件格式。

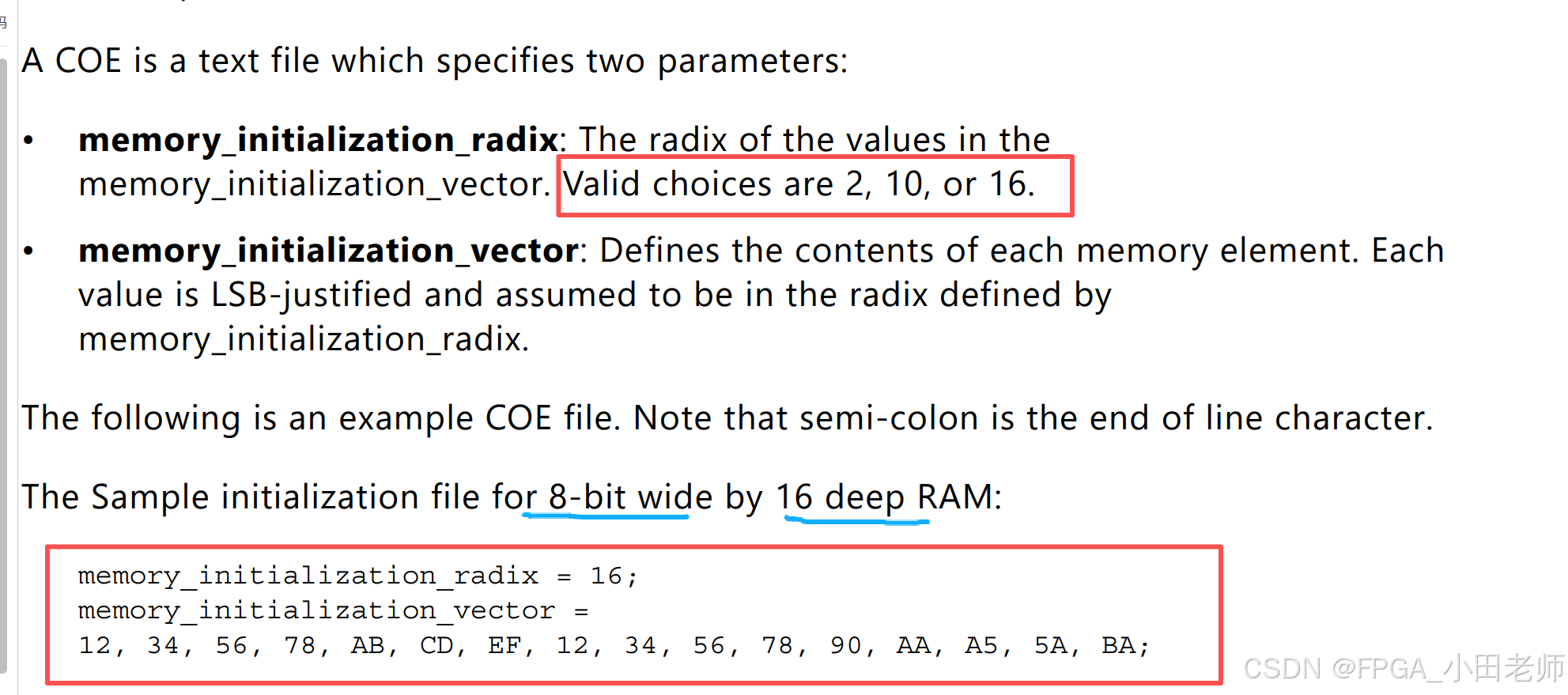

1 手册说明

手册里面给出的格式说明如下:

通过radix配置是2(二进制),10(十进制),16(十六进制)

通过vector配置数据

如果这里没有理解,没有关系哈,大家跟着我的思路试一下

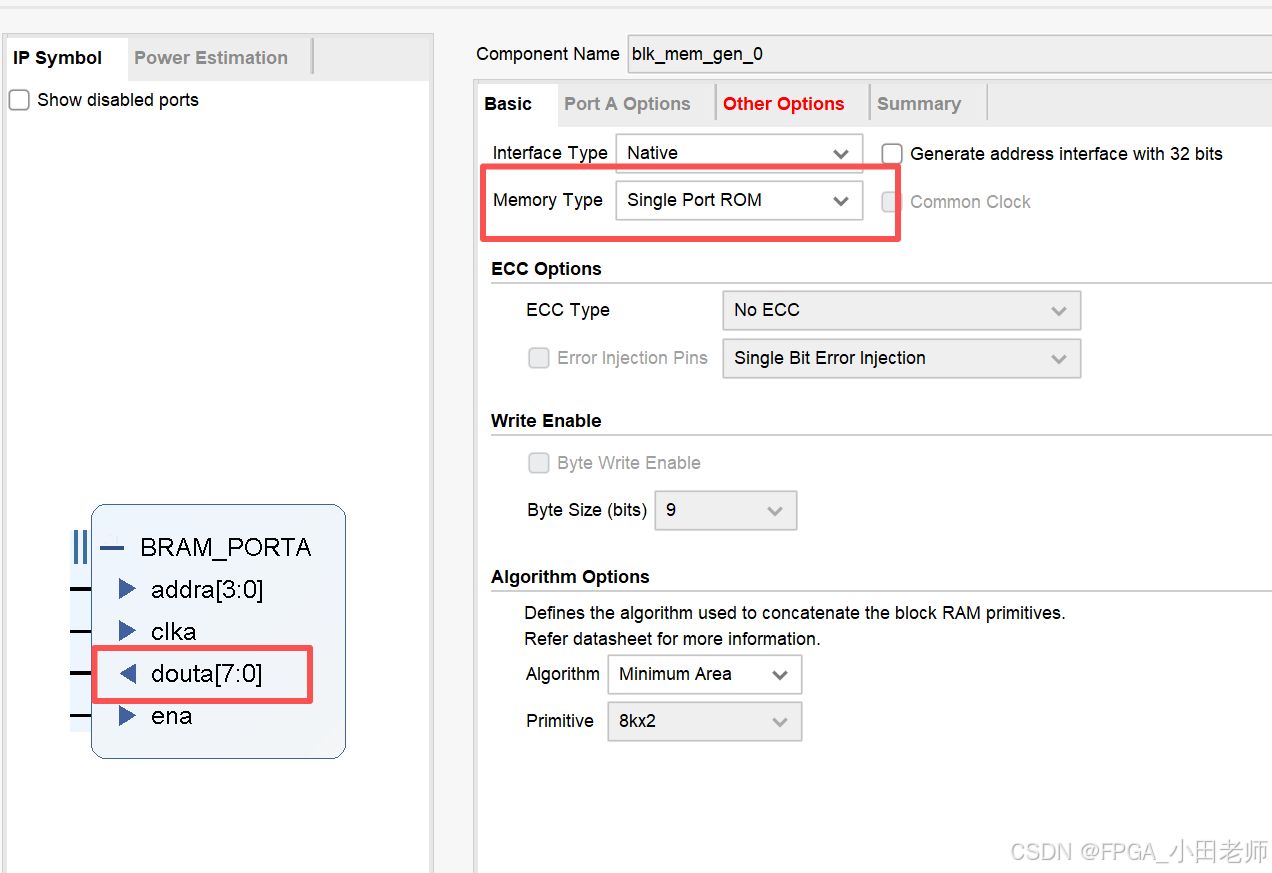

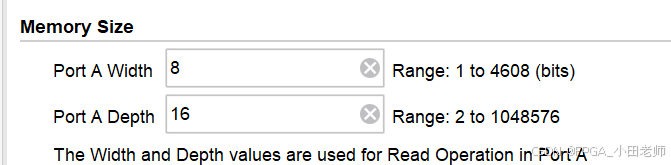

2 IP核配置

为了方便说明,我这里选择了单端口的ROM,数据宽度8bit,深度16bit,深度会直接决定地址addr的宽度哈

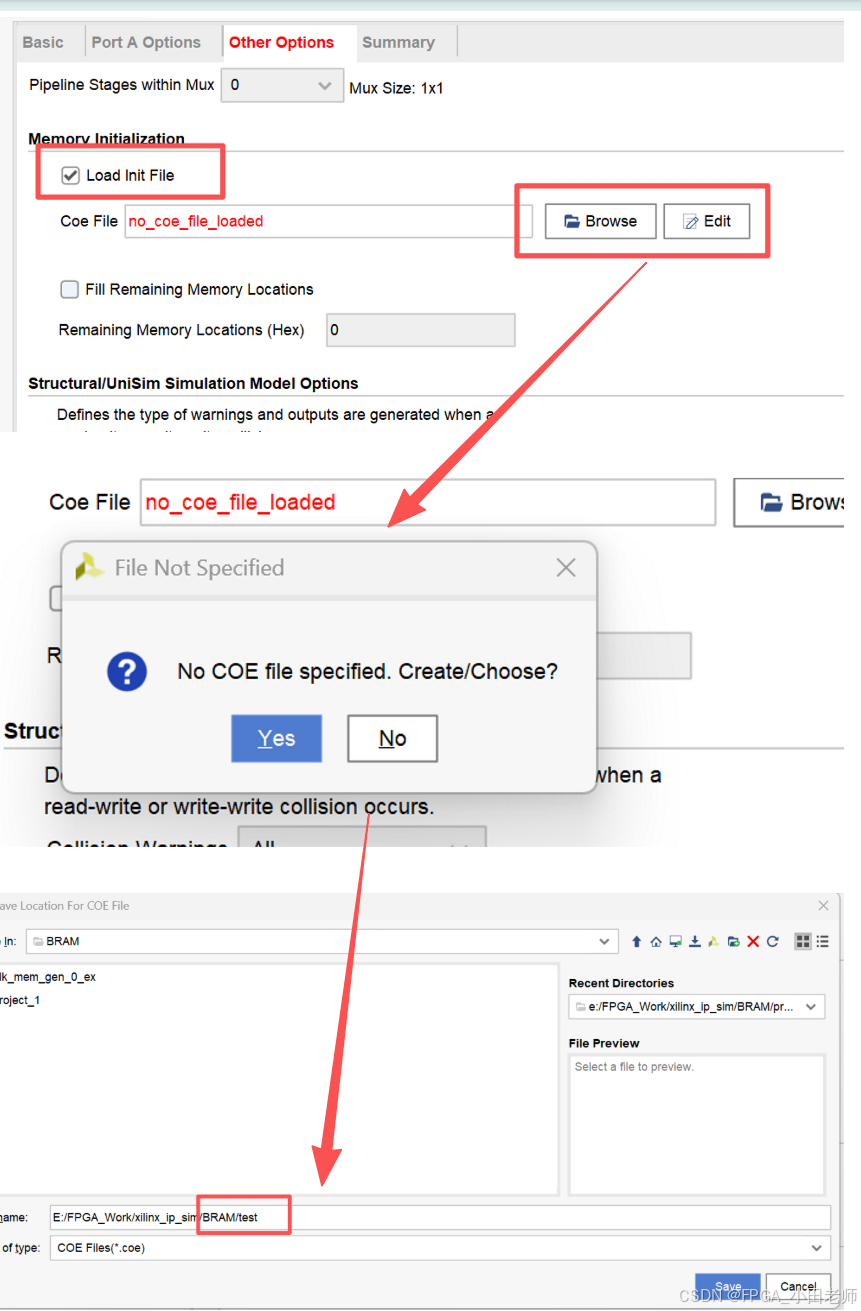

这里,我们勾选load init file,即导入初始化文件,如果我们已经有准备好的coe文件,点击Browse选择你的文件路径即可,但如果没有就点击Edit直接编辑就可以

我这里现在没有文件,我就给大家现场编辑了,点击Edit,按照上面的步骤新建一个test.coe的文件,点击save

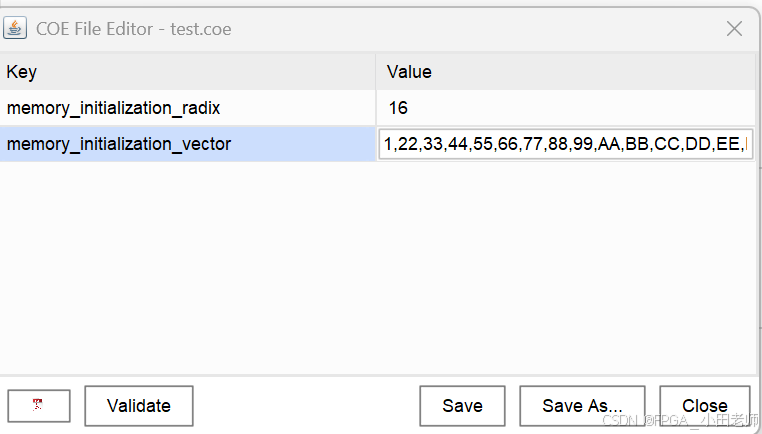

会打开这样一个界面,大家可以在这里填自己的数据,我这个是刚才写的 上面的radix即选择你是 二进制 十进制 还是 十六进制,我这里是 16进制的 我就给了16

下面的vetor写的就是你的数据列表,我暂时按照我的配置8bit位宽16深度给了16个8bit的数据

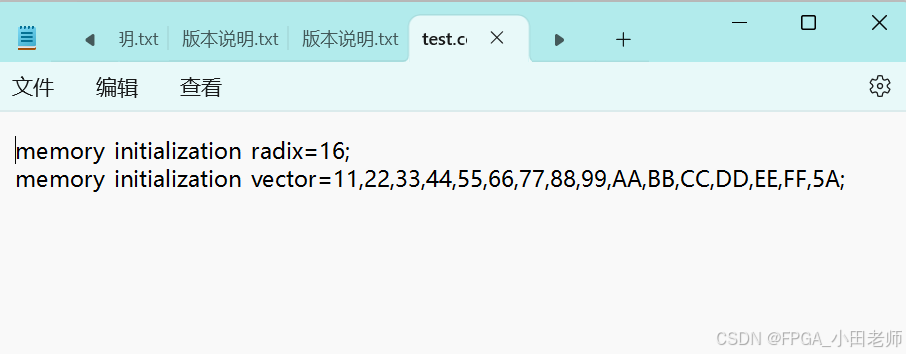

他其实就会生成一个这样的文件

3 仿真

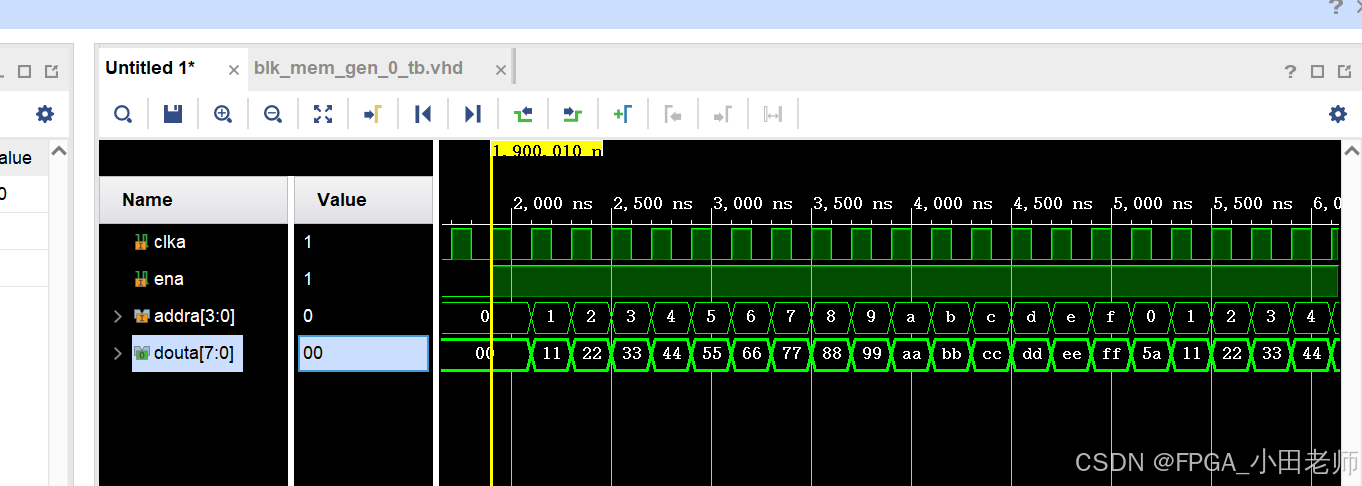

我们配置好之后,可以仿真看看,如下

这是从ROM中读出的数据,与我刚才的写入是一致的

那关于ROM的使用方法就这些,大家可以试试,如果大家有现成的数据,可以按照FPGA的coe文件格式整理好,一般数据量大的时候,自己手动整理比较麻烦,我们就可以借助Matlab等工具进行数据整理。