(以下内容全部出自上述课程)

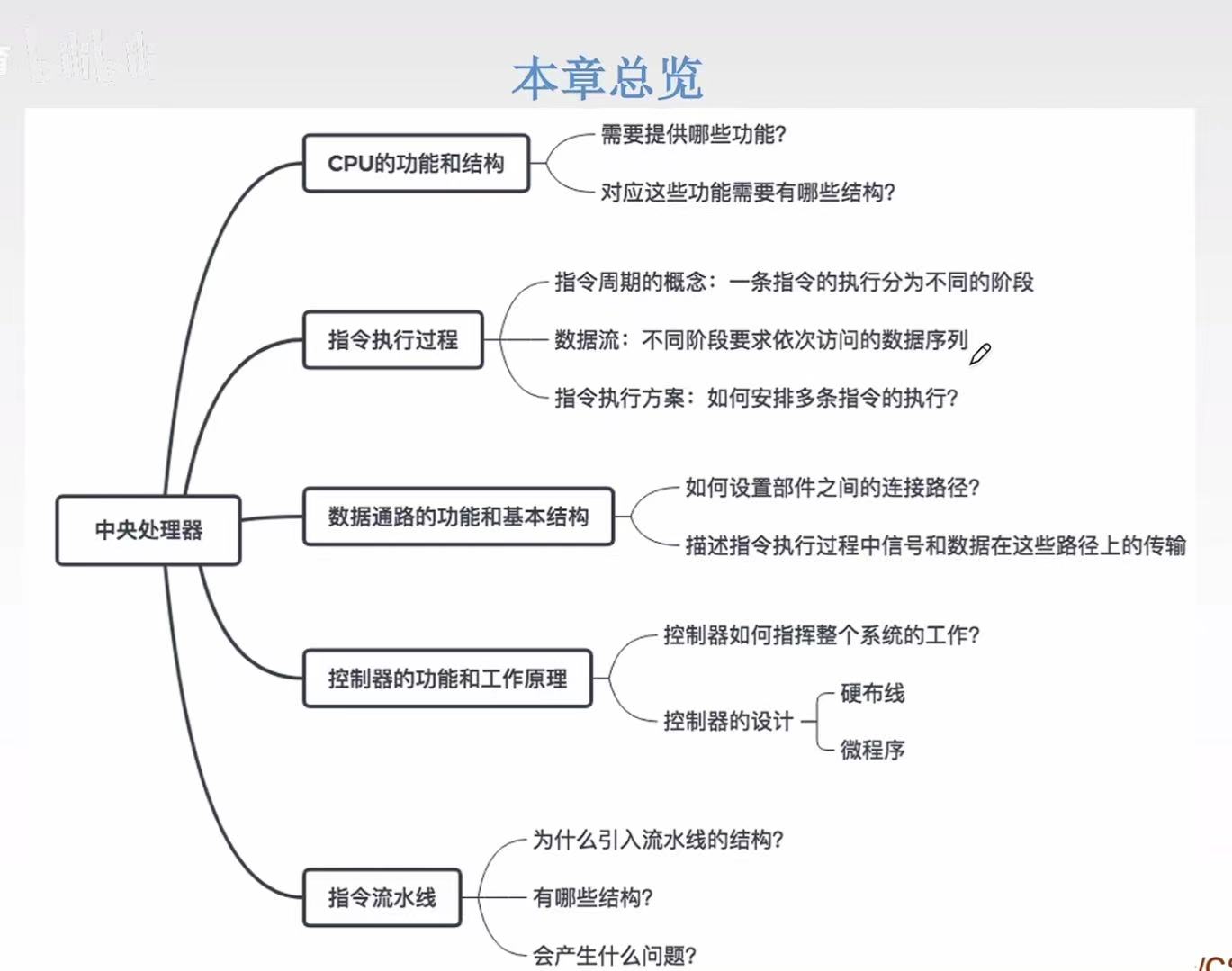

目录

- 大前提:任何数据都需要先通过寄存器再执行操作

- 指令执行过程

-

- [1. 指令周期](#1. 指令周期)

- [2. 指令周期流程](#2. 指令周期流程)

- [3. 指令周期的数据流](#3. 指令周期的数据流)

-

- [3.1 取指周期](#3.1 取指周期)

- [3.2 间址周期](#3.2 间址周期)

- [3.3 执行周期](#3.3 执行周期)

- [3.4 中断周期](#3.4 中断周期)

- [4. 指令执行方案](#4. 指令执行方案)

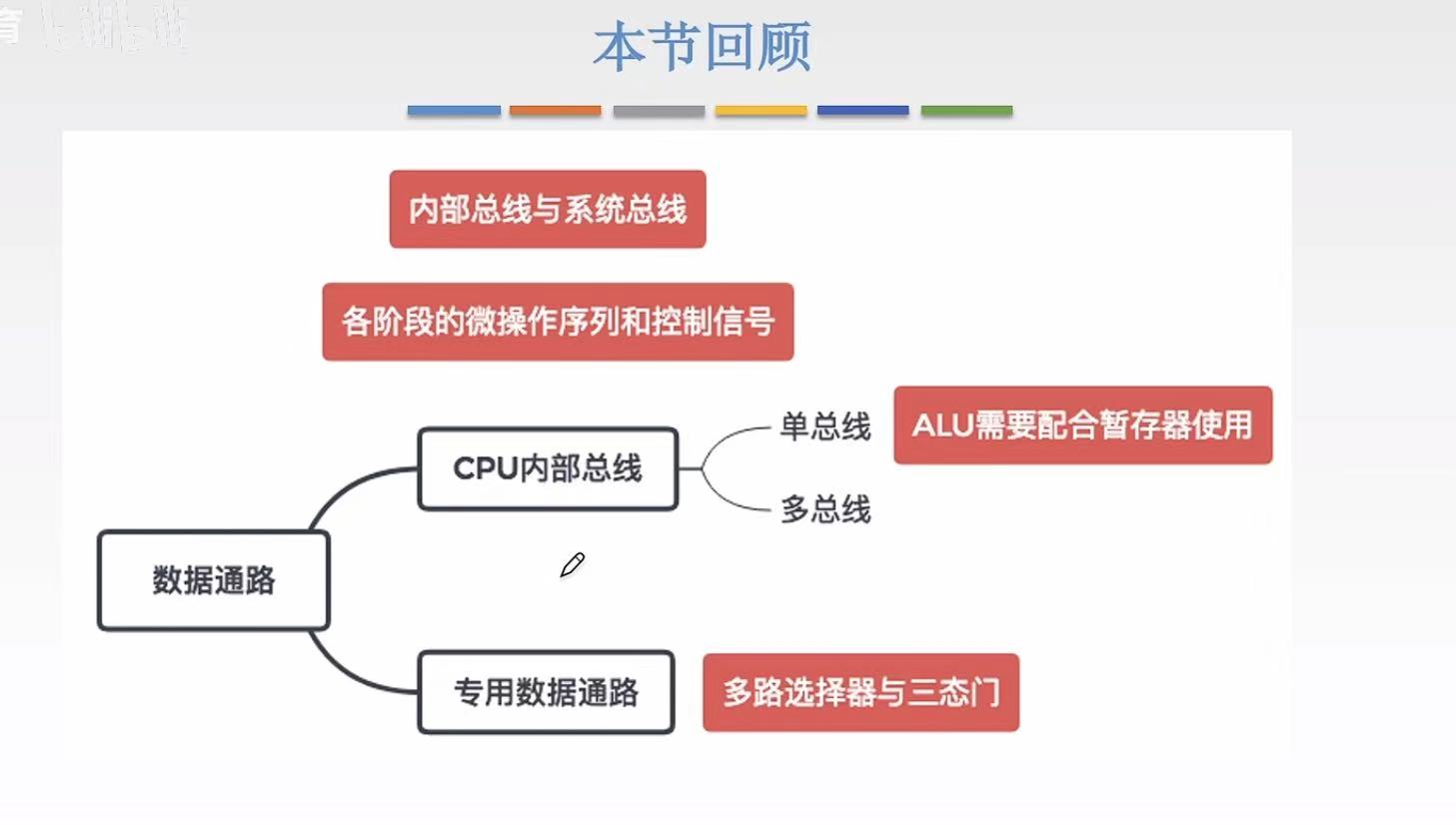

- 数据通路-单总线结构

-

- [1. 指令周期的数据流](#1. 指令周期的数据流)

- [2. 数据通路](#2. 数据通路)

- [3. 单总线方式](#3. 单总线方式)

- [4. 例题](#4. 例题)

- [5. 小结](#5. 小结)

- 数据通路-专用通路结构

-

- [1. 专用数据通路方式](#1. 专用数据通路方式)

- [2. 例题](#2. 例题)

- [3. 小结](#3. 小结)

- 硬布线控制器

-

- [1. 硬布线控制器](#1. 硬布线控制器)

- [2. 设计(了解)](#2. 设计(了解))

-

- [2.1 分析每个阶段的微操作序列](#2.1 分析每个阶段的微操作序列)

- [2.2 安排微操作时序的原则](#2.2 安排微操作时序的原则)

- [2.3 组合逻辑设计](#2.3 组合逻辑设计)

- [2.4 微操作信号综合](#2.4 微操作信号综合)

- [2.5 画出逻辑图](#2.5 画出逻辑图)

- [3. 小结](#3. 小结)

大前提:任何数据都需要先通过寄存器再执行操作

指令执行过程

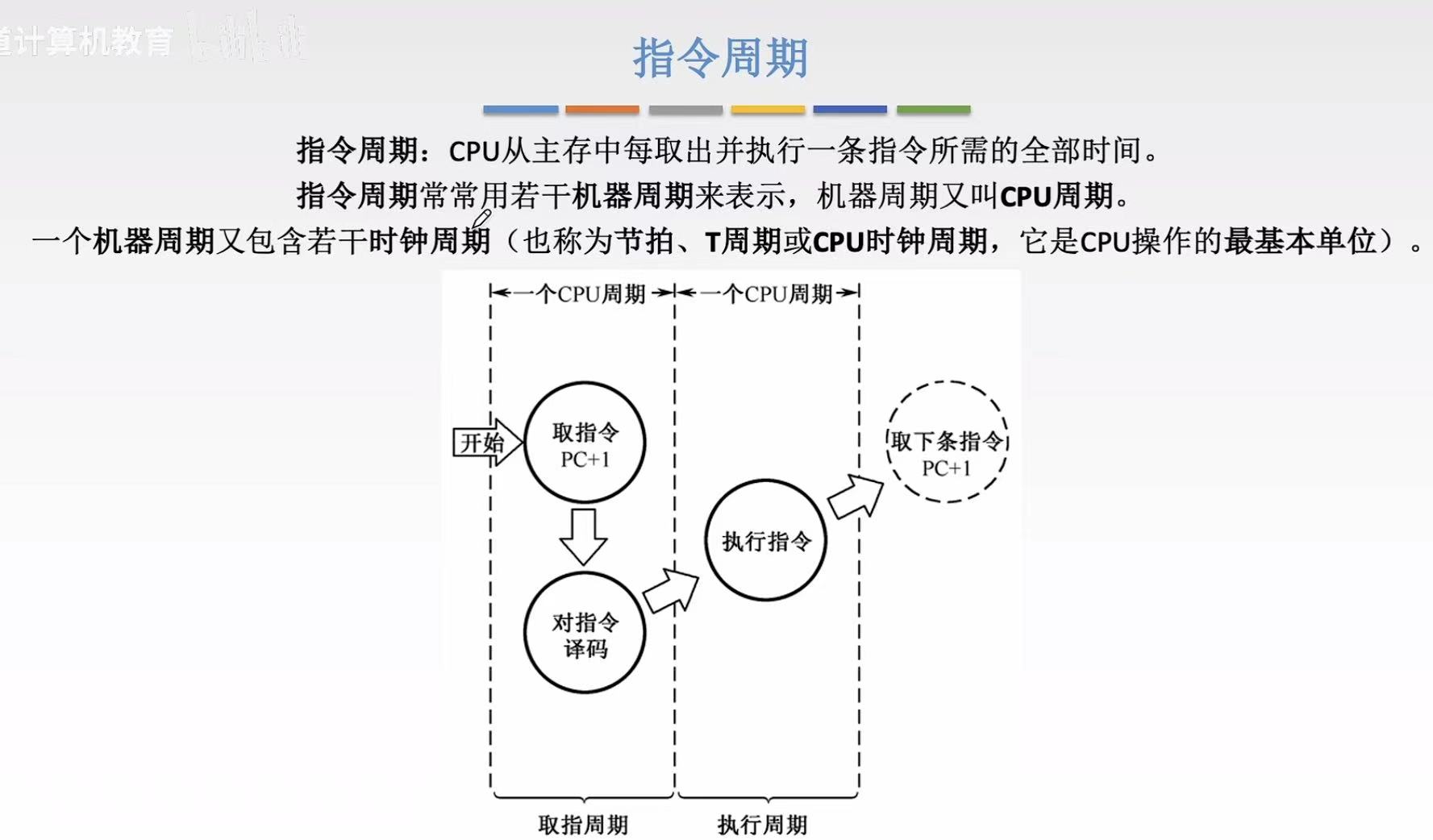

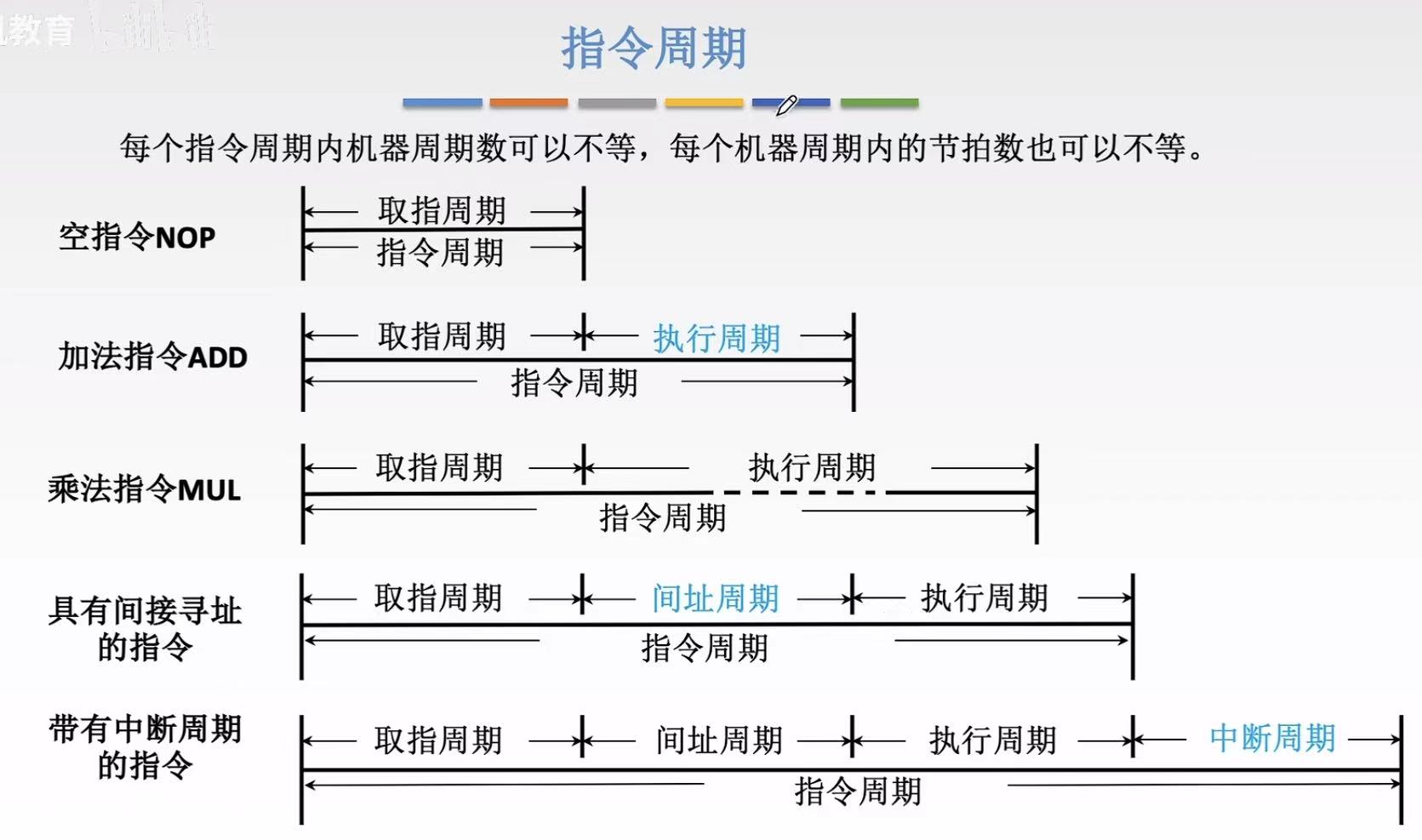

1. 指令周期

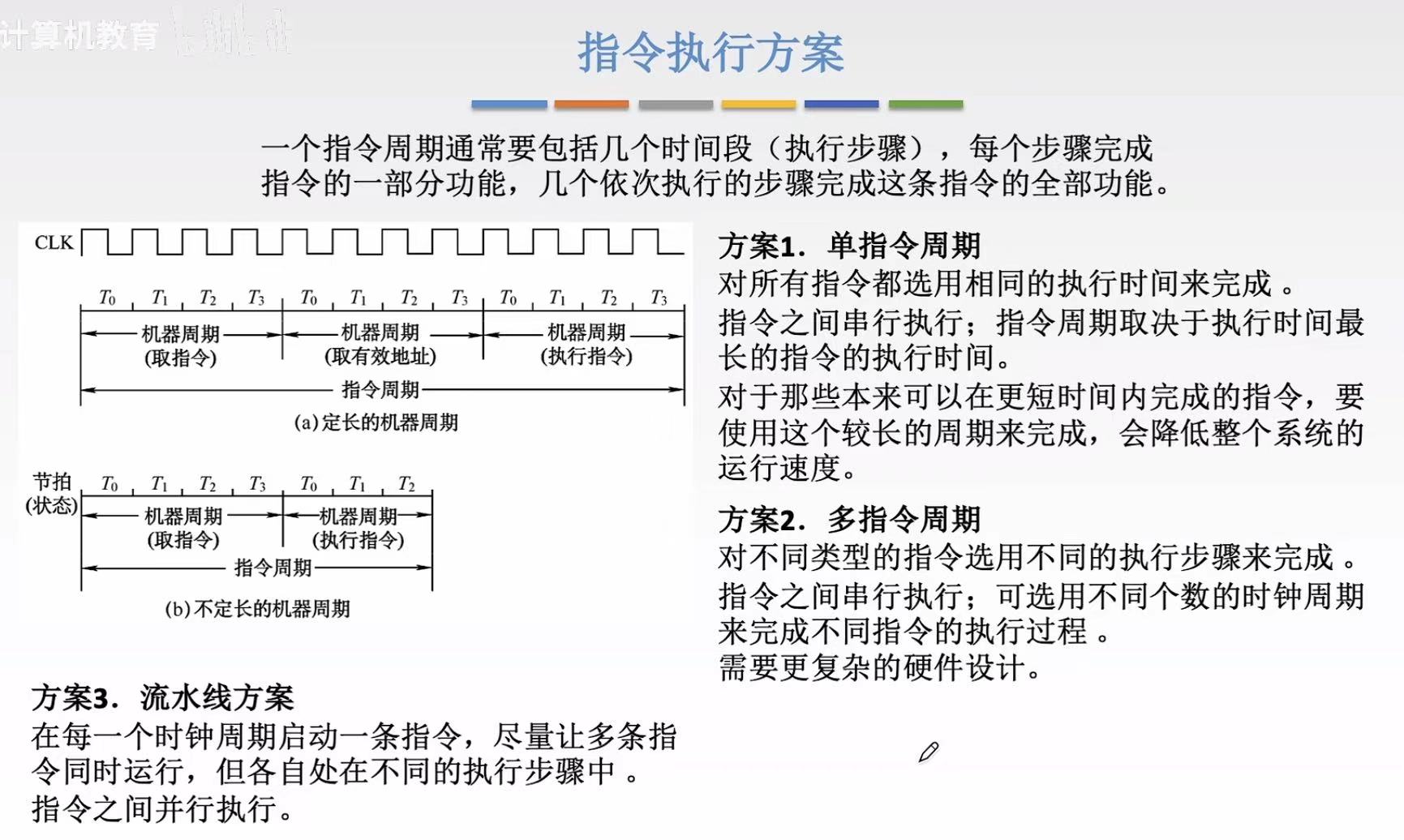

从小到大:时钟周期-->机器周期(CPU)周期-->指令周期

- 取指周期:取指令-->PC+1-->对指令译码

- 执行周期:执行指令

- 指令周期=取指周期+执行周期

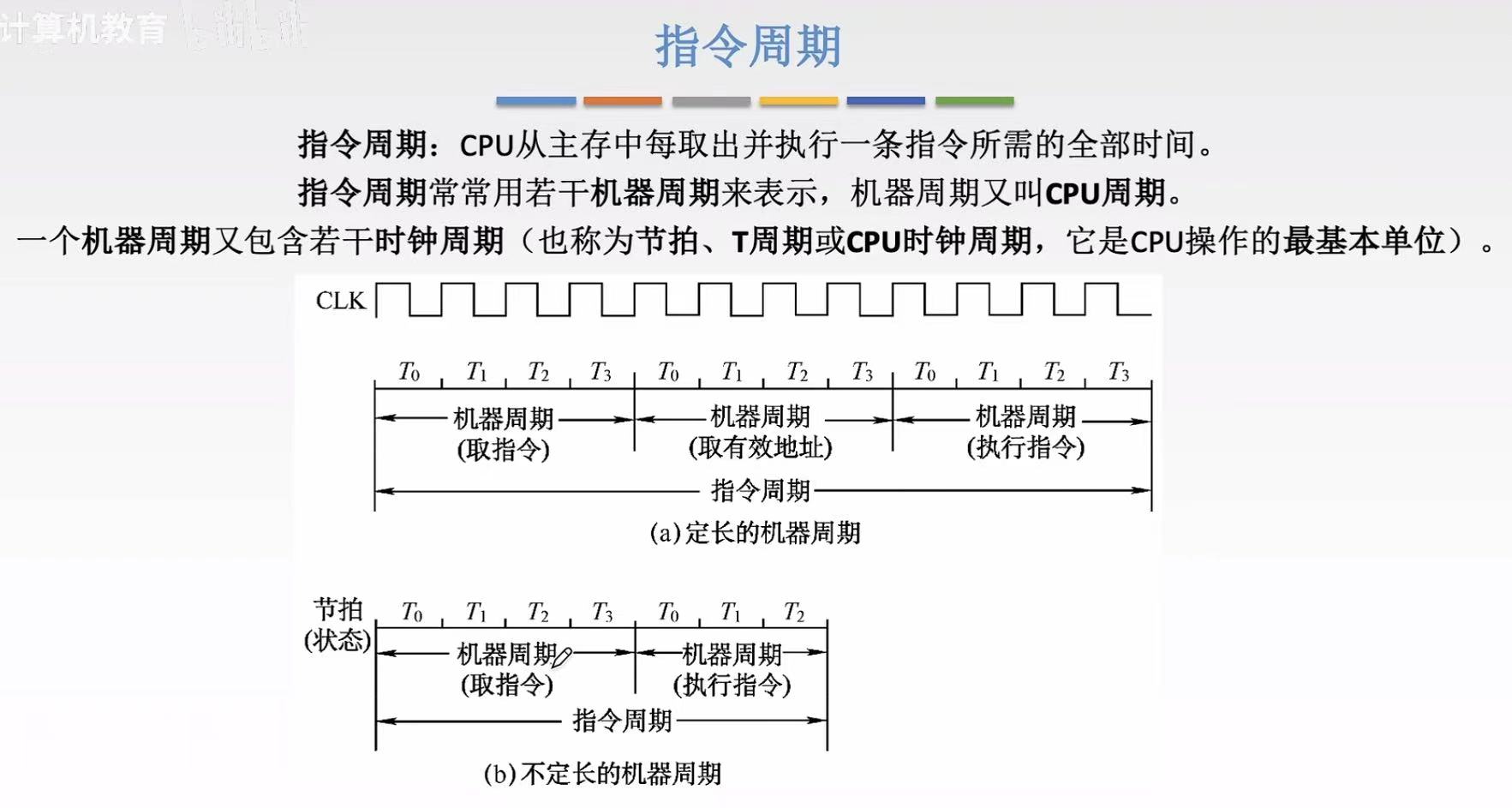

- CLK 是英文 "Clock" 的缩写,表示计算机或数字电路中的时钟信号。

- 每个时钟周期被划分为若干个阶段(如 T₀, T₁, T₂, T₃),这些阶段称为节拍(Beat)。

- 定长的机器周期:三个机器周期都是四个节拍。

- 不定长 的机器周期:机器周期不都相同。

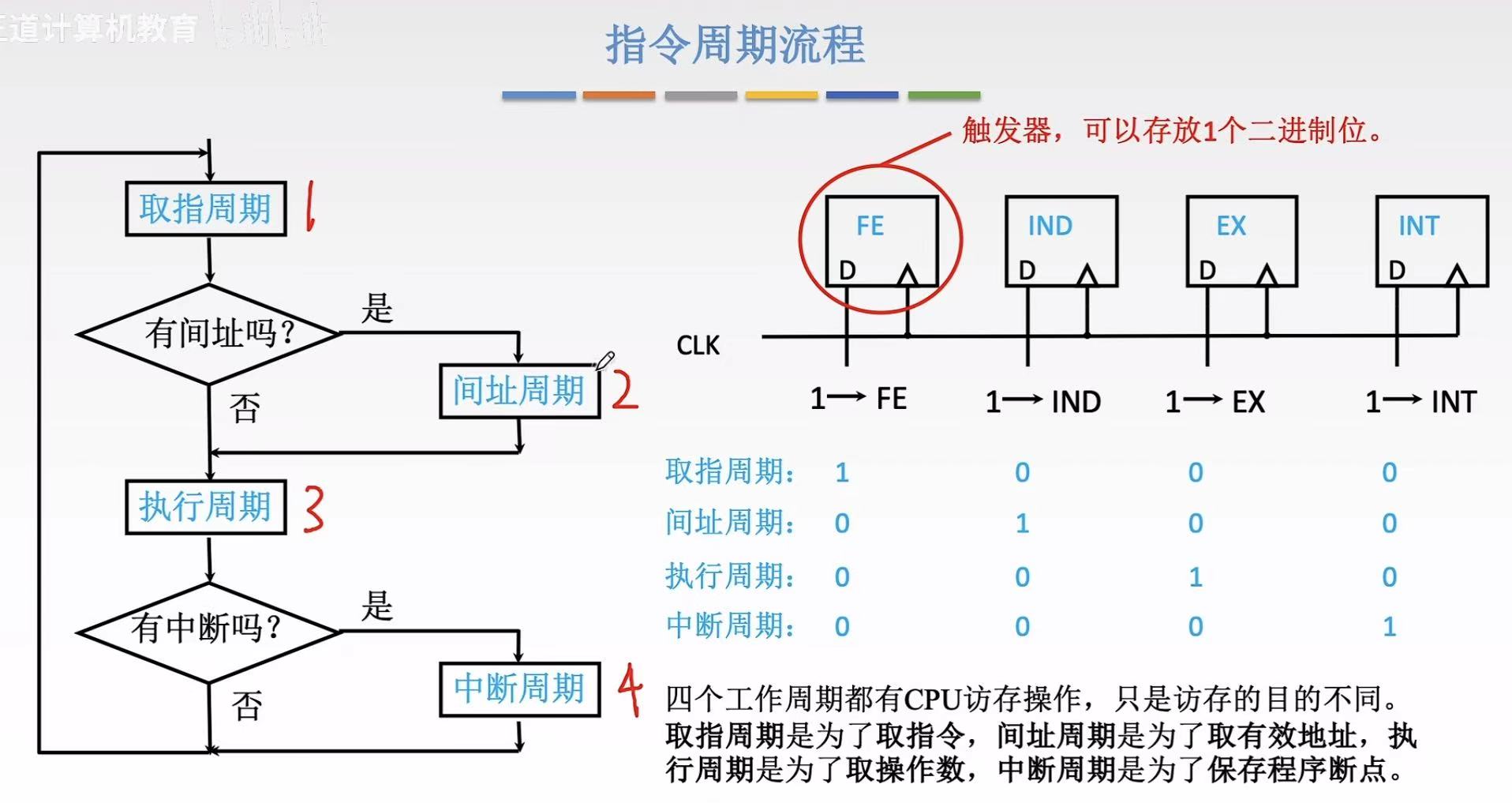

2. 指令周期流程

触发器:

- FE:Fetch 取指令(从内存中取出下一条指令)

- IND:Indirect Addressing 或 Decode 地址间接寻址 / 指令译码

- EX:Execute 执行指令(如算术运算、逻辑操作)

- INT :Interrupt 或 Write Back 中断处理 / 写回结果

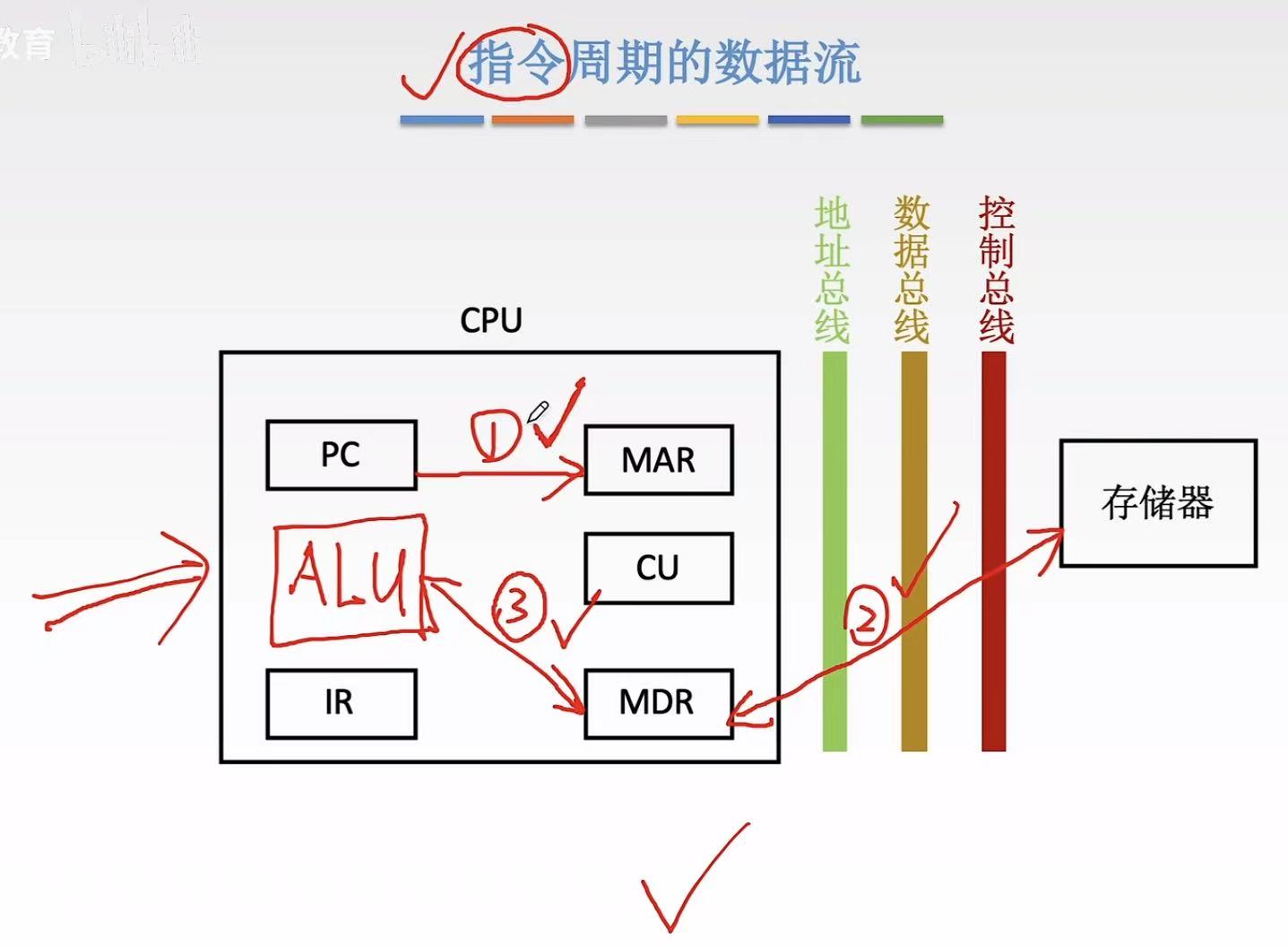

3. 指令周期的数据流

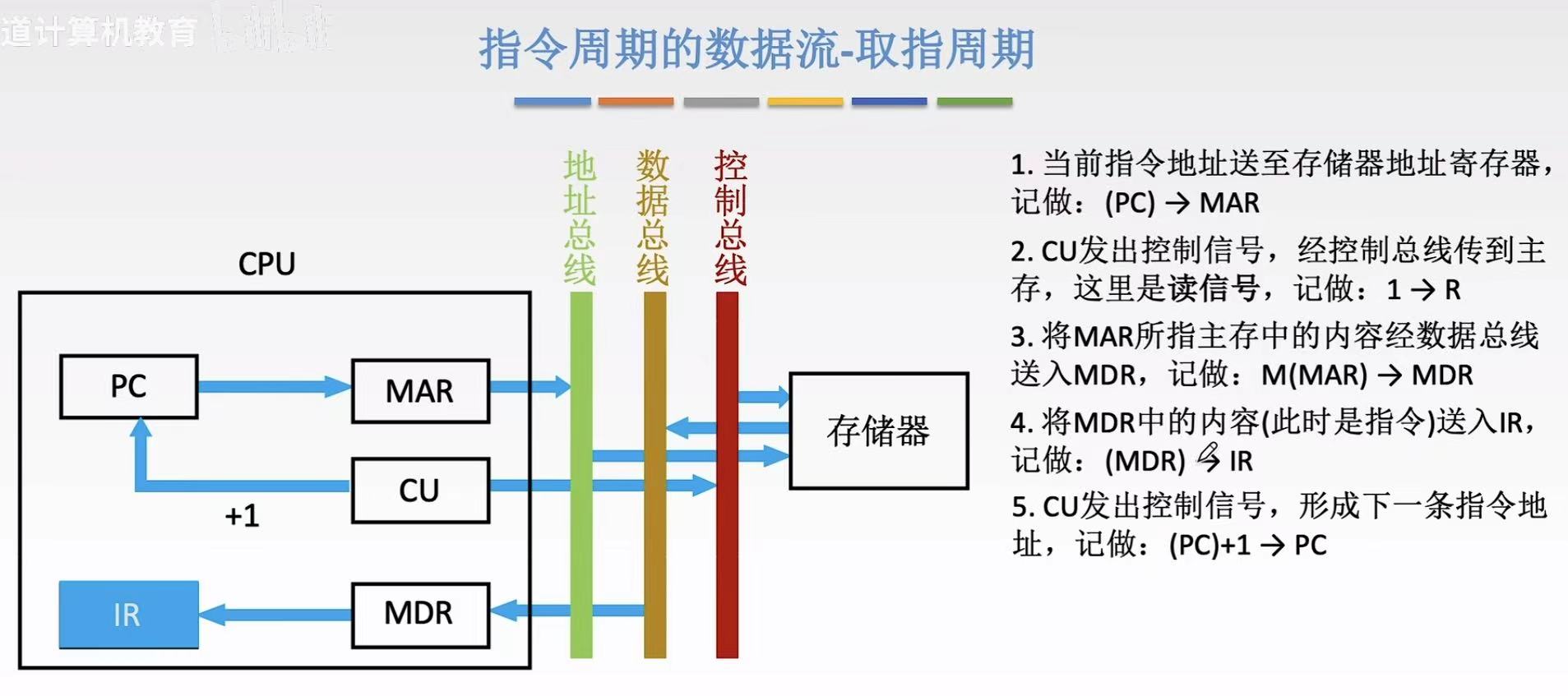

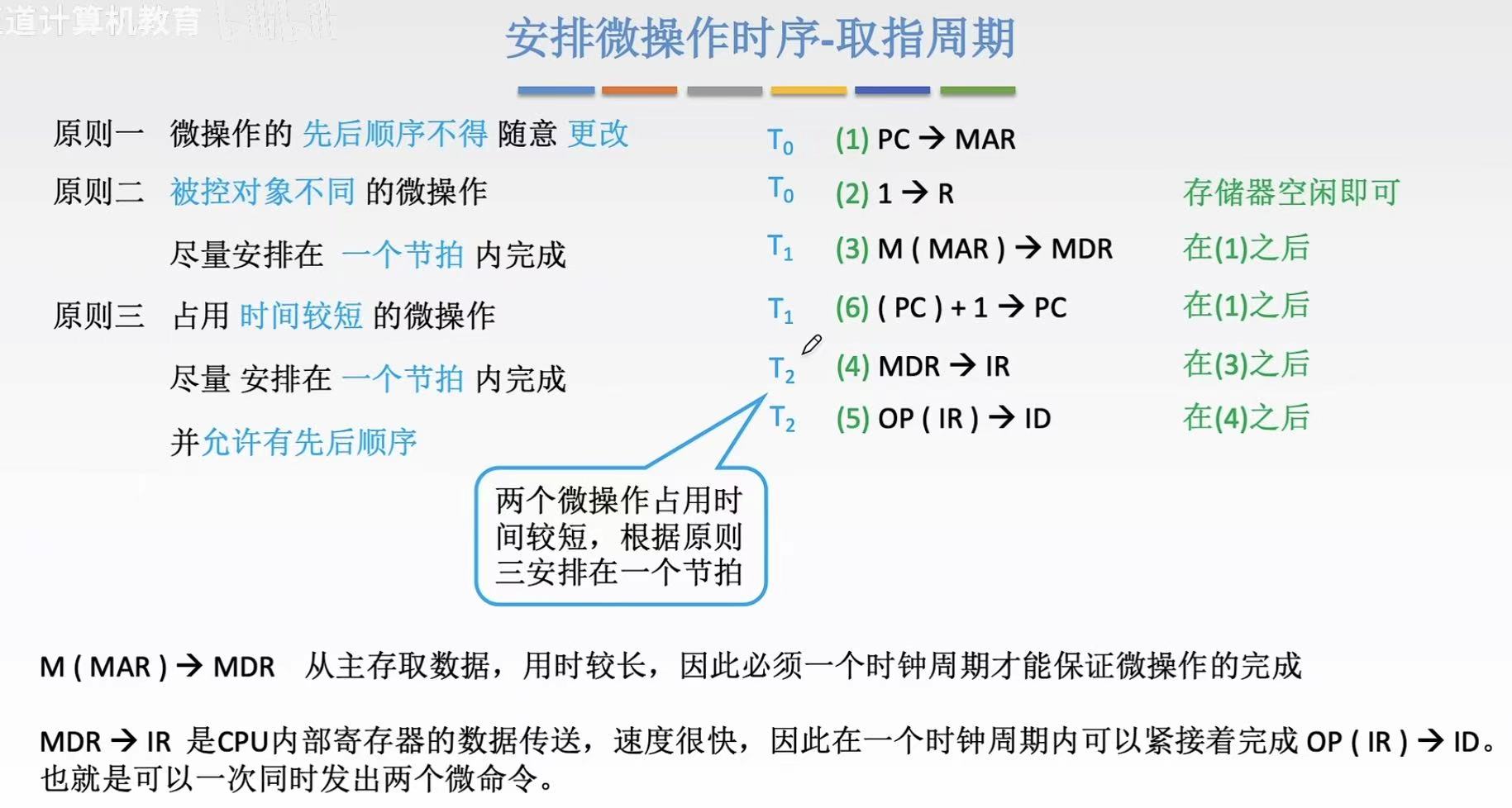

3.1 取指周期

前提:(寄存器):指的是寄存器中存的东西

- 指令地址PC-->存储器地址寄存器MAR

- CU发出控制信号(读信号):1-->R

- 地址寄存器指的主存内容送入数据寄存器:M(MAR)-->MDR

- 数据寄存器得到指令传入指令寄存器:(MDR)-->IR

- 计数器指向下一条指令:(PC)+1-->PC

类比-公交车司机:

- PC → MAR 司机查看电子路单:"下一站是 第5站:中山公园"

→ : 把"中山公园"这个站名输入车载导航(MAR)

PC : 是"下一条指令地址" → 相当于"下一站编号/名称"

MAR: 是"当前要访问的地址" → 导航目的地 - 1 → R(读信号) 司机按下"查询站台信息"按钮 发出"读内存"请求,准备获取该站的详细信息

- M(MAR) → MDR 车载系统从数据库调出中山公园站的信息:"停靠30秒,开门下客,有换乘地铁2号线"

**内存(M)**中存储的是该站的操作指令(不是乘客!)

MDR 暂存这条"操作命令" - MDR → IR 司机看到屏幕显示:"停30秒,开门,可换乘"

→ : 他记住了这条指令(IR = 当前指令)

IR: 存储的是刚取到的指令内容,准备下一步执行 - PC + 1 → PC 司机更新路单:"下下站是 第6站:人民广场" 程序计数器自动+1,为下一次"取指"做准备

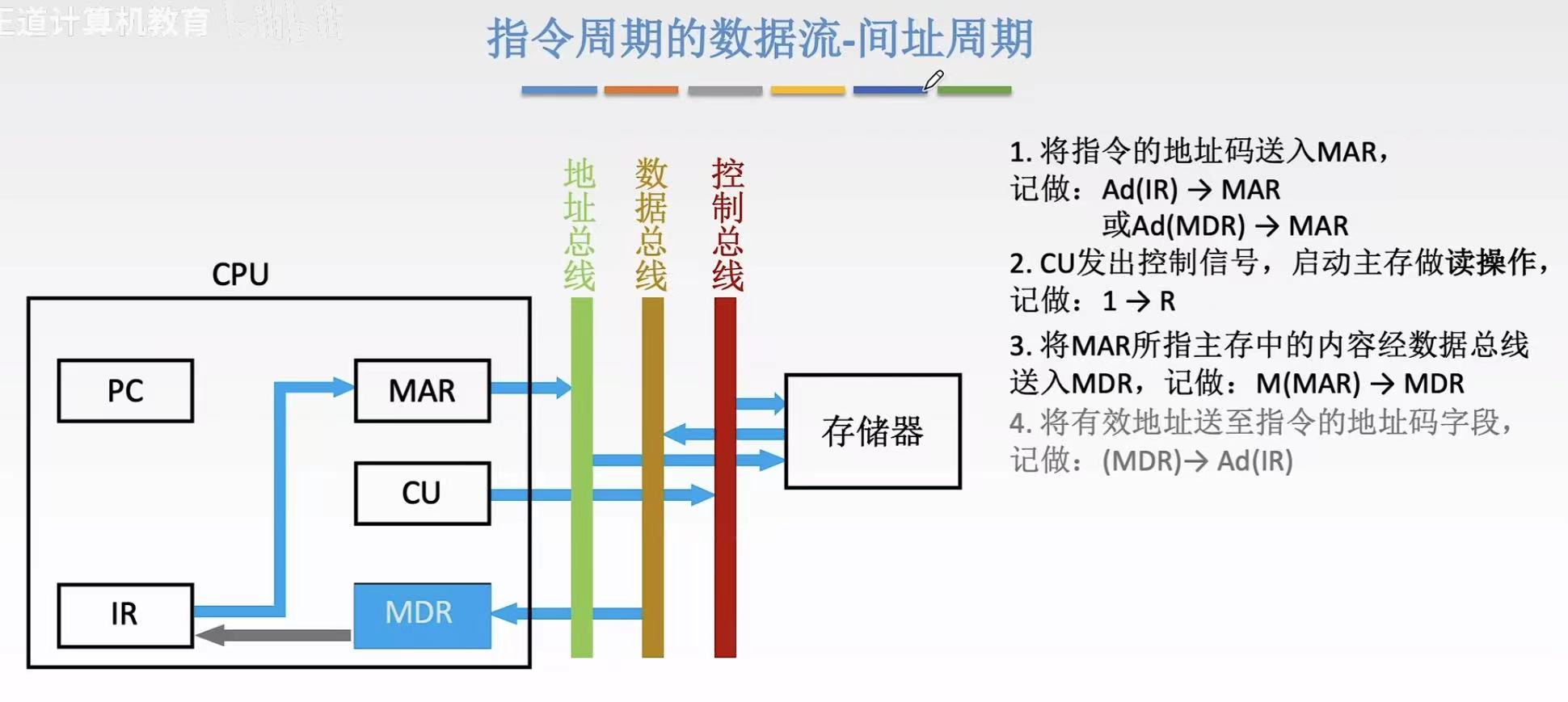

3.2 间址周期

- 将指令的地址码送入地址存储器:Ad(IR)-->MAR

- 控制单元发出控制信号(读操作):1-->R

- 地址存储器所指的主存内容送入数据存储器:M(MAR)-->MDR

- 将有效地址送至指令的地址码字段:(MDR)-->Ad(IR)

类比-去快递柜取快递:

- Ad(IR) → MAR 你看到短信写着:"取件码:A123"

→ : 把 A123 输入快递柜屏幕

A123: 是"间接地址",存入 MAR(相当于输入框) - 1 → R(读信号) 你按下"查询"按钮 发出"读"请求,让系统去查 A123 对应什么格口

- M(MAR) → MDR 屏幕显示:"您的包裹在 格口 B7" 内存(快递系统数据库)返回真正的地址 B7,存入 MDR(屏幕显示)

- MDR → Ad(IR) 你记住"B7",准备去开 B7 格口 把有效地址 B7 写回"下一步要访问的位置"(Ad(IR) 更新为 B7)

3.3 执行周期

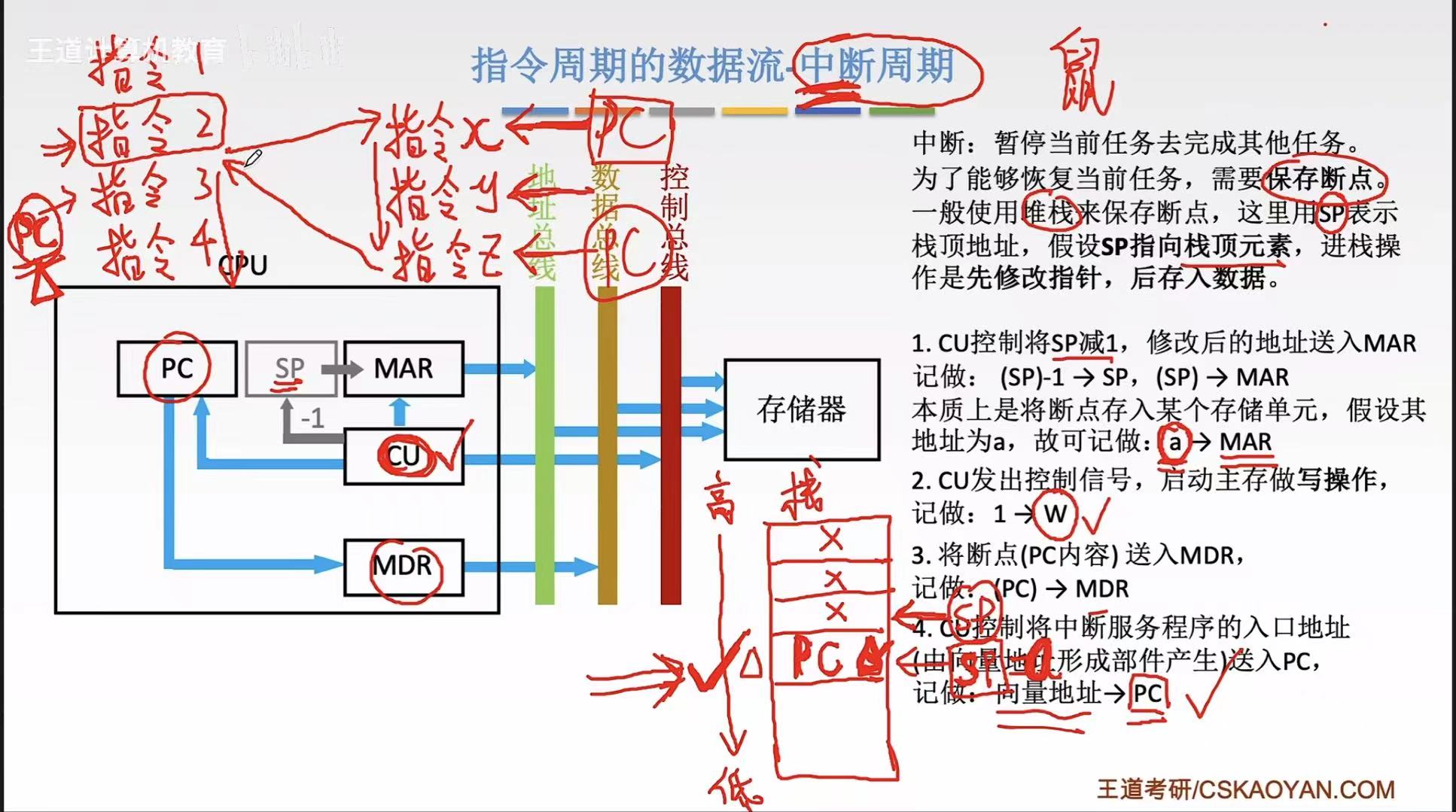

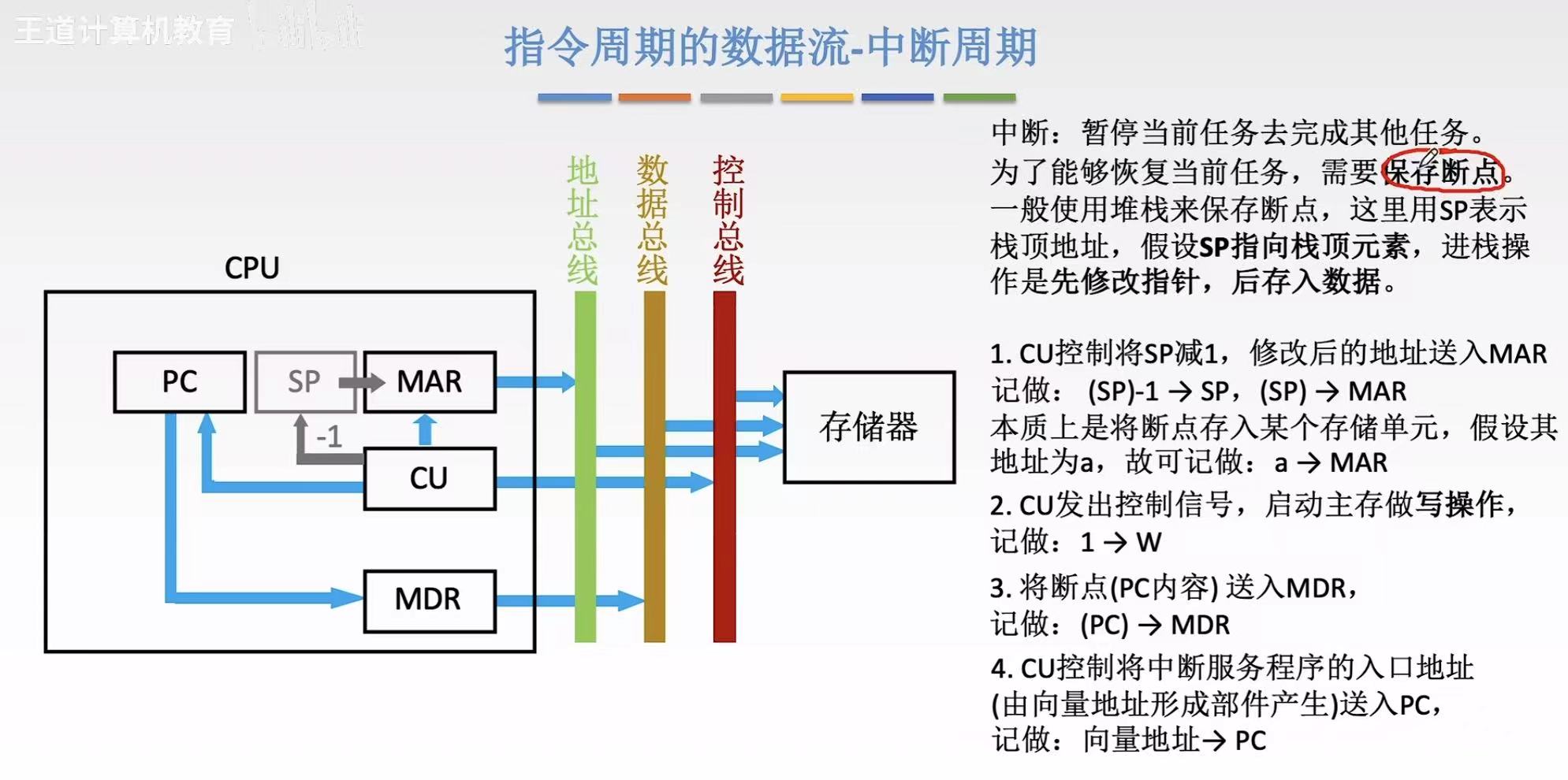

3.4 中断周期

类比-写作业被电话打断:

- CU 控制将 SP 减 1,修改后的地址送入 MAR

记做:(SP)-1 → SP,(SP) → MAR 你放下笔,走到书桌边,从抽屉里拿出一个"记忆便签本"(栈),翻到最后一页,撕下一张空白纸条(SP-1),把这张纸条放在最上面(SP 更新)。

→ : 这张纸条现在就是"待填地址"的位置(MAR = 栈顶地址)

SP : 是栈指针,指向下一个可用栈空间

SP-1 : 是"预留出一个位置"

MAR: 就像"你要往哪里写信息" - CU 发出控制信号,启动主存做写操作

记做:1 → W 你拿起笔,在这张空白纸条上准备写字(发出"写"信号) W=1 表示"开始写数据",就像你准备好记录了 - 将断点(PC 内容)送入 MDR

记做:(PC) → MDR 你回头看看作业本,发现刚才写到第 5 题第 3 步(当前 PC 指向的位置),于是你在心里记下:"我停在第 5 题第 3 步。"

→ : 把这个"位置"记在脑中(MDR = 数据暂存区)

PC : 是"当前执行位置" → 相当于"作业进度"

MDR: 是临时缓存,就像你脑子里先记着 - CU 控制将中断服务程序入口地址送入 PC

记做:向量地址 → PC 你拿起手机,接通电话,听到妈妈说:"你爸到了,快去开门!"

→ : 你立刻决定:"我现在要去门口开门"(转去中断服务程序)

你的"下一步动作"变成了"去门口"(PC 被改写为中断入口) 中断向量地址 = "该做什么事"的指令地址

PC : 被更新为"新任务的起点"

4. 指令执行方案

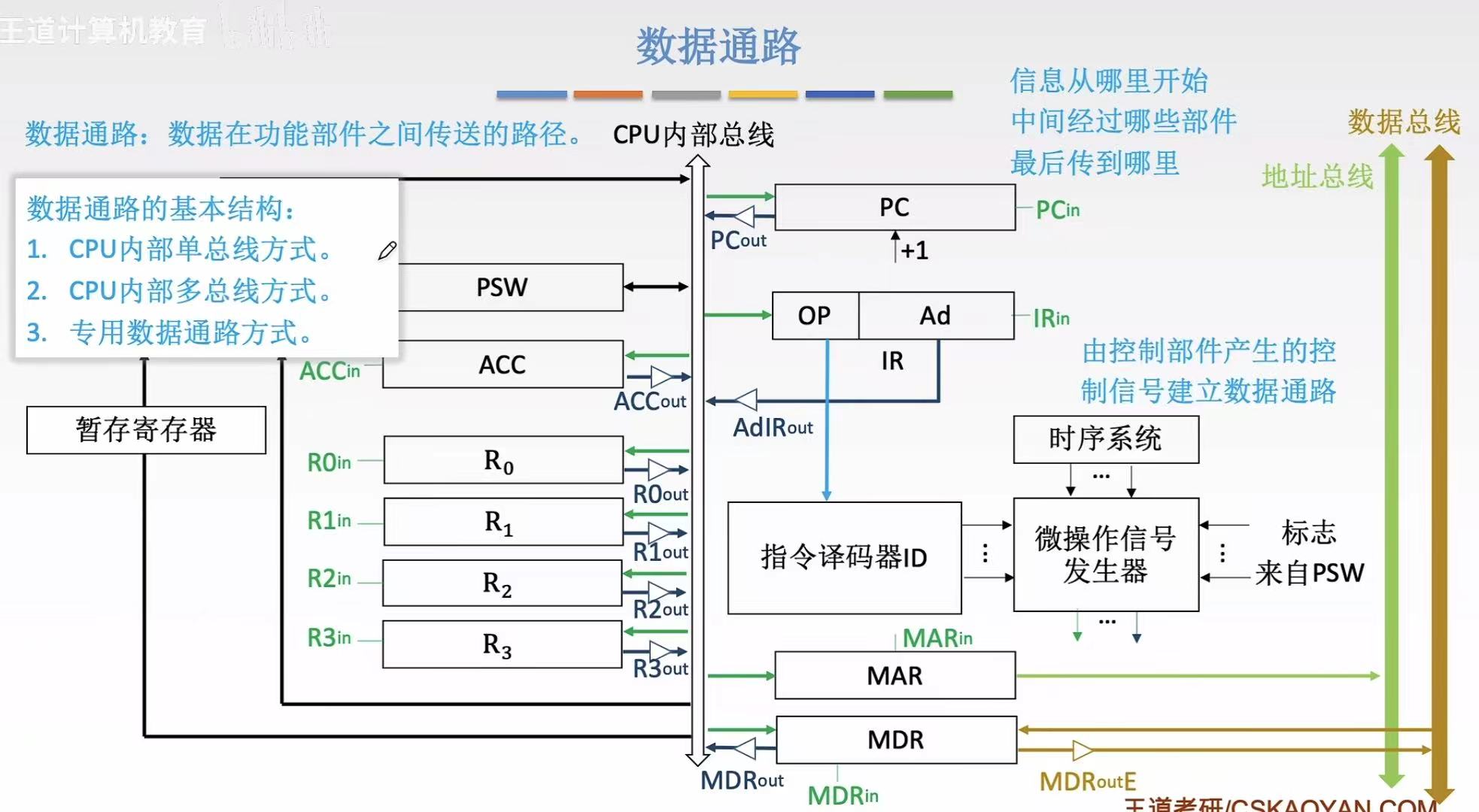

数据通路-单总线结构

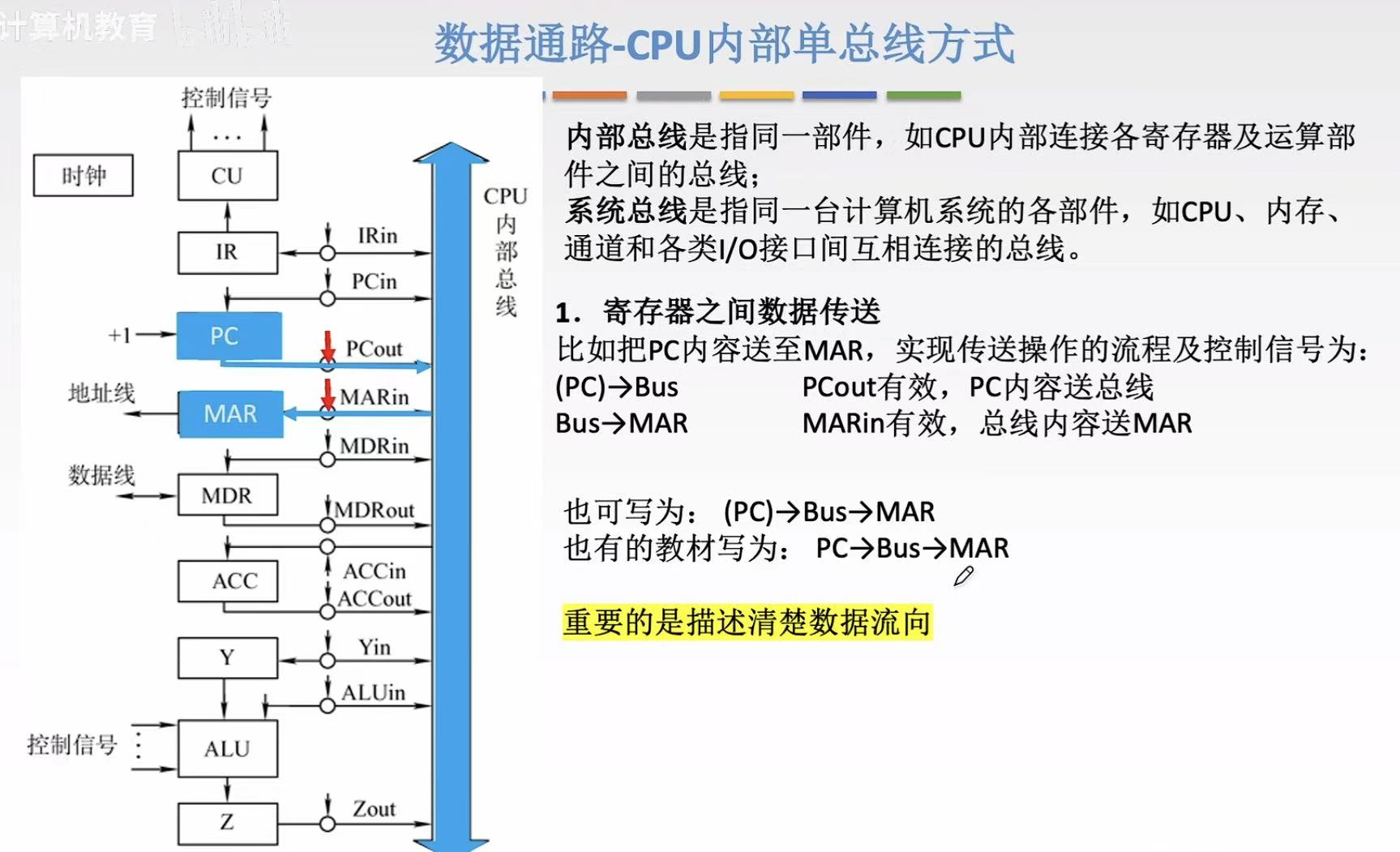

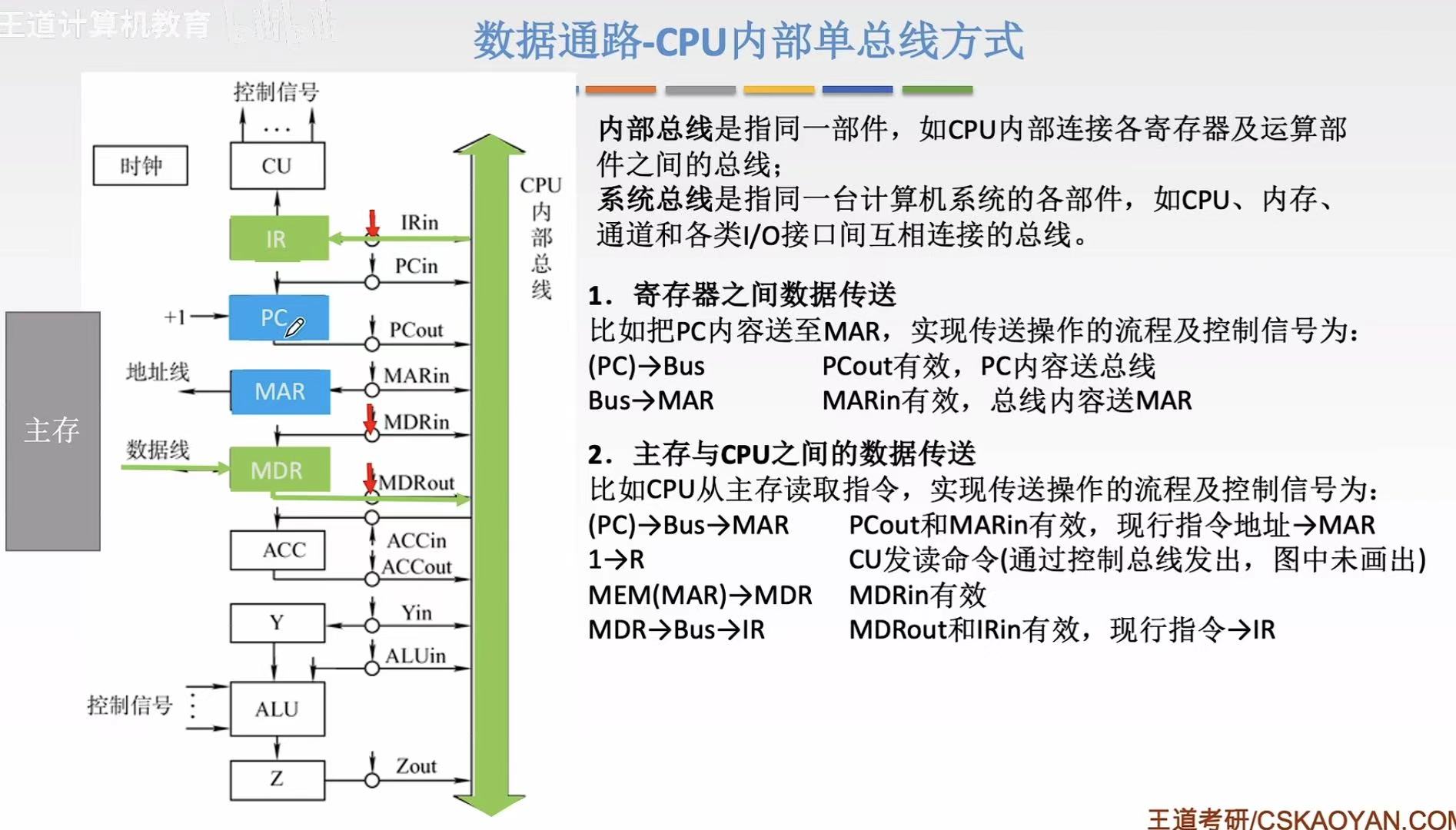

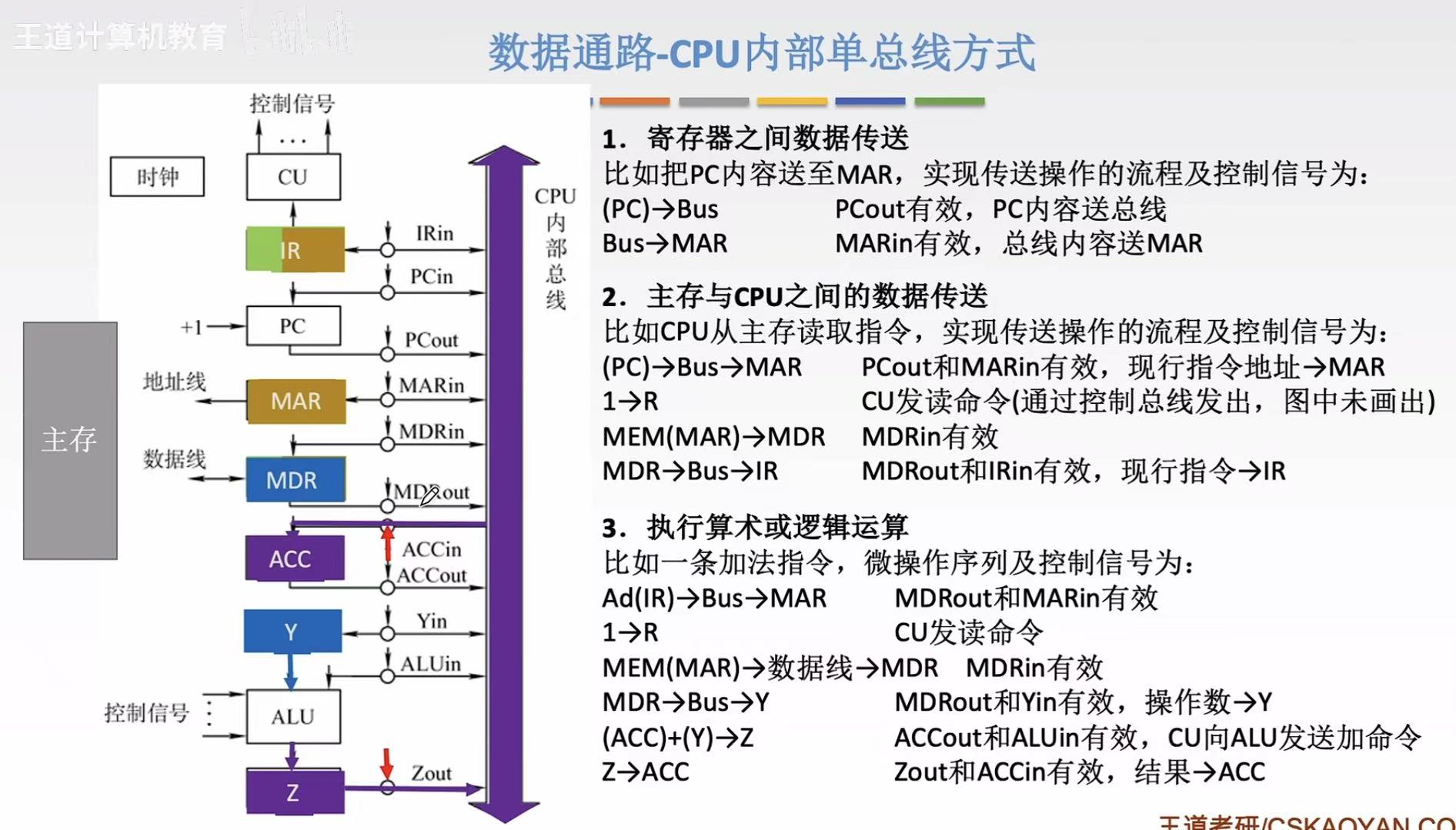

单总线结构:只有一条CPU内部总线。

1. 指令周期的数据流

2. 数据通路

3. 单总线方式

寄存器之间数据传送:

- PC → MAR 司机查看电子路单:"下一站是 第5站:中山公园"

→ : 把"中山公园"这个站名输入车载导航(MAR)

PC : 是"下一条指令地址" → 相当于"下一站编号/名称"

MAR: 是"当前要访问的地址" → 导航目的地 - 总线就相当于中间的一个媒介,相当于输入框(将中山公园输入至车载导航上)

主存与CPU之间的数据传送(包含寄存器之间数据传送):

PC-->总线-->MAR-->主存-->MDR-->总线-->IR

执行加法指令:

IR-->总线-->MAR-->主存-->数据线-->MDR-->总线-->Y-->Z

ACC-->Z

Z-->ACC

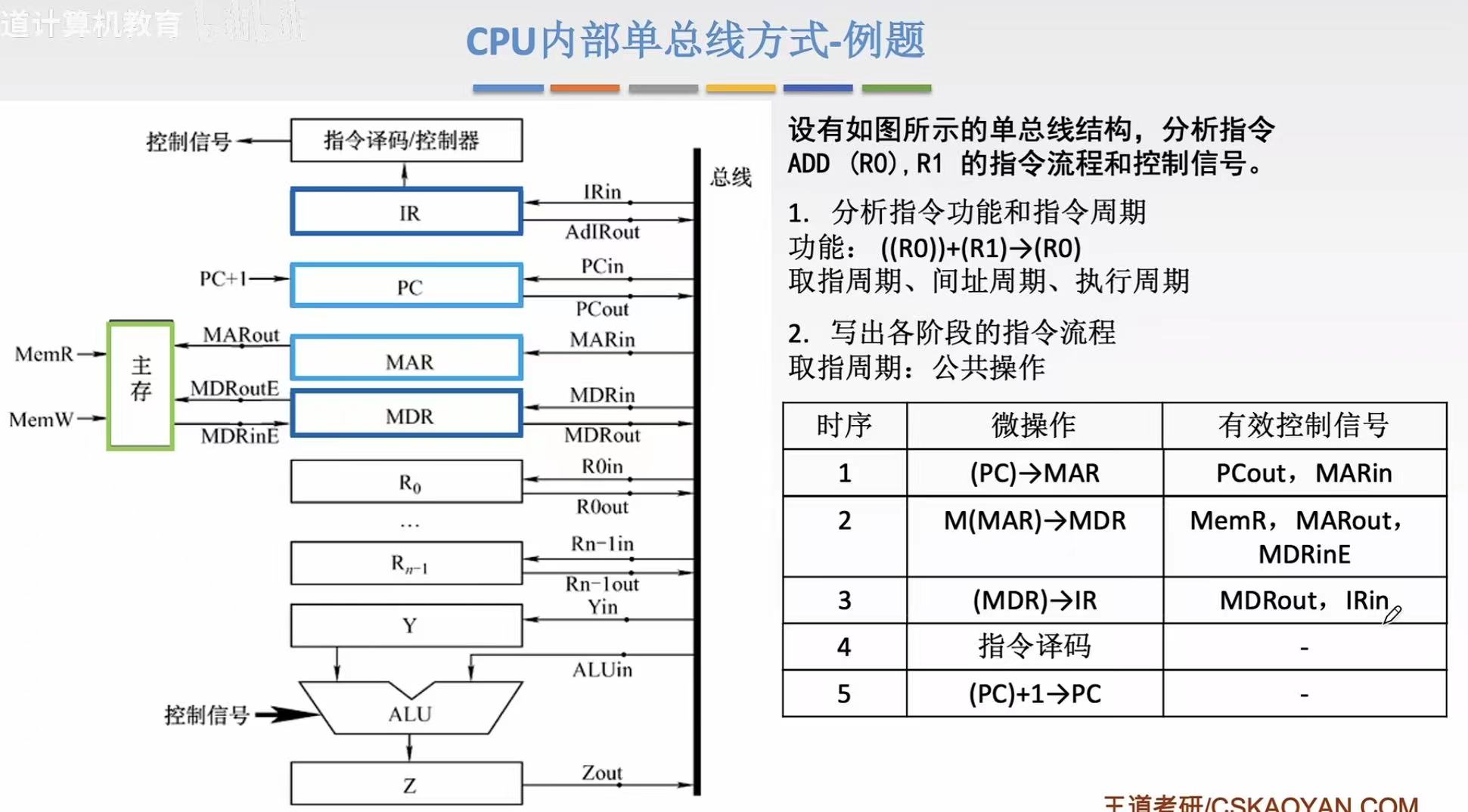

4. 例题

- CPU 采用 单总线结构(所有部件通过一条总线通信)

- 指令:ADD (R0), R1

- 功能:(R0) + (R1) → R0

即:将寄存器 R0 所指向的内存单元内容,与 R1 的内容相加,结果存回 R0。

指令格式隐含:ADD (R0), R1 是 间接寻址(R0 中存放的是操作数的地址),R1 是源操作数寄存器。

- 取指周期:公共操作,所有的指令这个阶段都一样

复习:

类比-公交车司机:

- PC → MAR 司机查看电子路单:"下一站是 第5站:中山公园"

→ : 把"中山公园"这个站名输入车载导航(MAR)

PC : 是"下一条指令地址" → 相当于"下一站编号/名称"

MAR: 是"当前要访问的地址" → 导航目的地 - 1 → R(读信号) 司机按下"查询站台信息"按钮 发出"读内存"请求,准备获取该站的详细信息

- M(MAR) → MDR 车载系统从数据库调出中山公园站的信息:"停靠30秒,开门下客,有换乘地铁2号线"

**内存(M)**中存储的是该站的操作指令(不是乘客!)

MDR 暂存这条"操作命令" - MDR → IR 司机看到屏幕显示:"停30秒,开门,可换乘"

→ : 他记住了这条指令(IR = 当前指令)

IR: 存储的是刚取到的指令内容,准备下一步执行 - PC + 1 → PC 司机更新路单:"下下站是 第6站:人民广场" 程序计数器自动+1,为下一次"取指"做准备

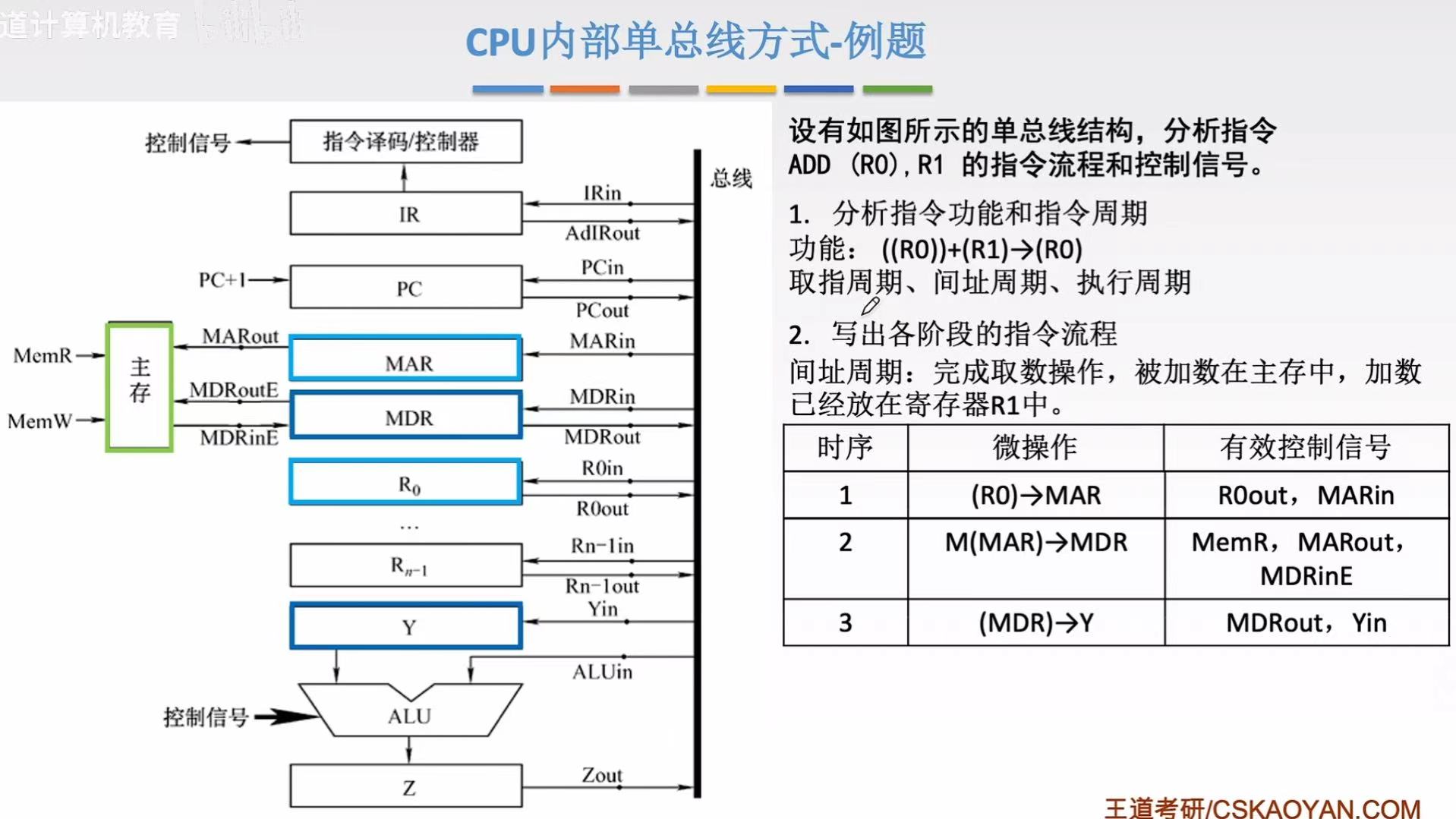

- 间址周期 :也算公共操作,不过可以看具体指令修改Ad(IR)

复习:

类比-去快递柜取快递:

- Ad(IR) → MAR 你看到短信写着:"取件码:A123"

→ : 把 A123 输入快递柜屏幕

A123: 是"间接地址",存入 MAR(相当于输入框) - 1 → R(读信号) 你按下"查询"按钮 发出"读"请求,让系统去查 A123 对应什么格口

- M(MAR) → MDR 屏幕显示:"您的包裹在 格口 B7" 内存(快递系统数据库)返回真正的地址 B7,存入 MDR(屏幕显示)

- MDR → Ad(IR) 你记住"B7",准备去开 B7 格口 把有效地址 B7 写回"下一步要访问的位置"(Ad(IR) 更新为 B7)

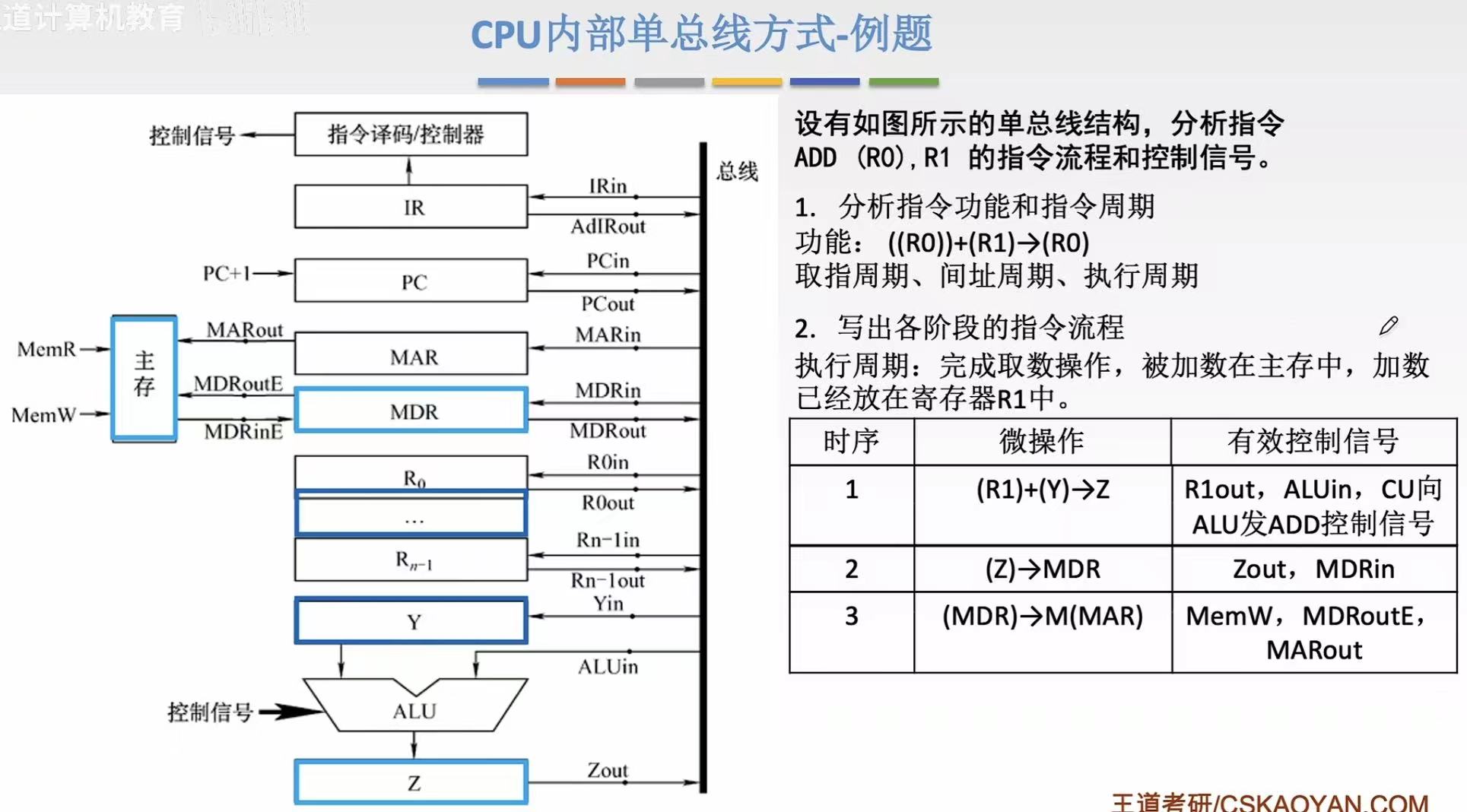

- 执行周期:具体指令具体分析

- 注意:数据最终都是要存入主存的,所以这里加完的结果需要返回主存。

5. 小结

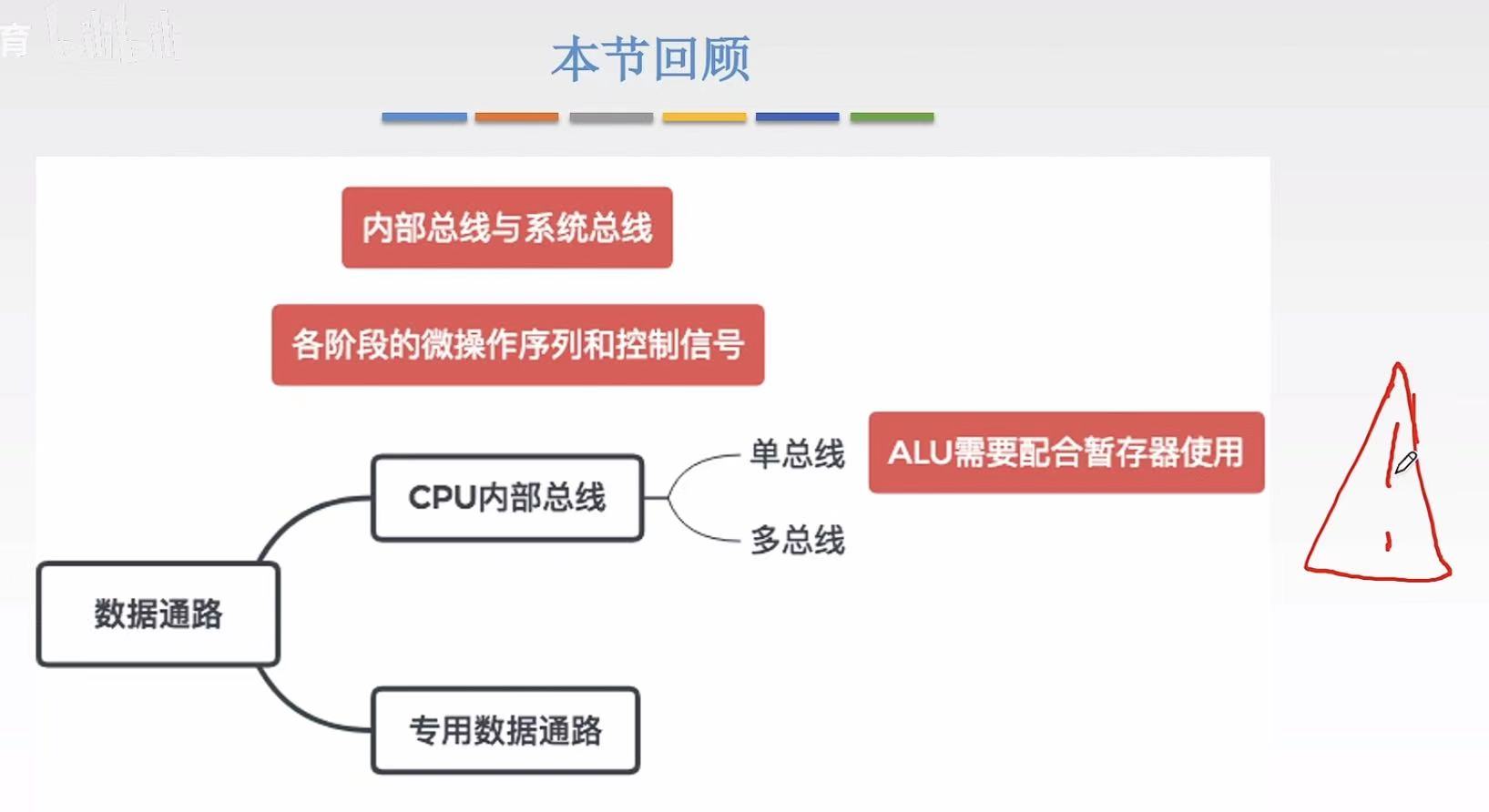

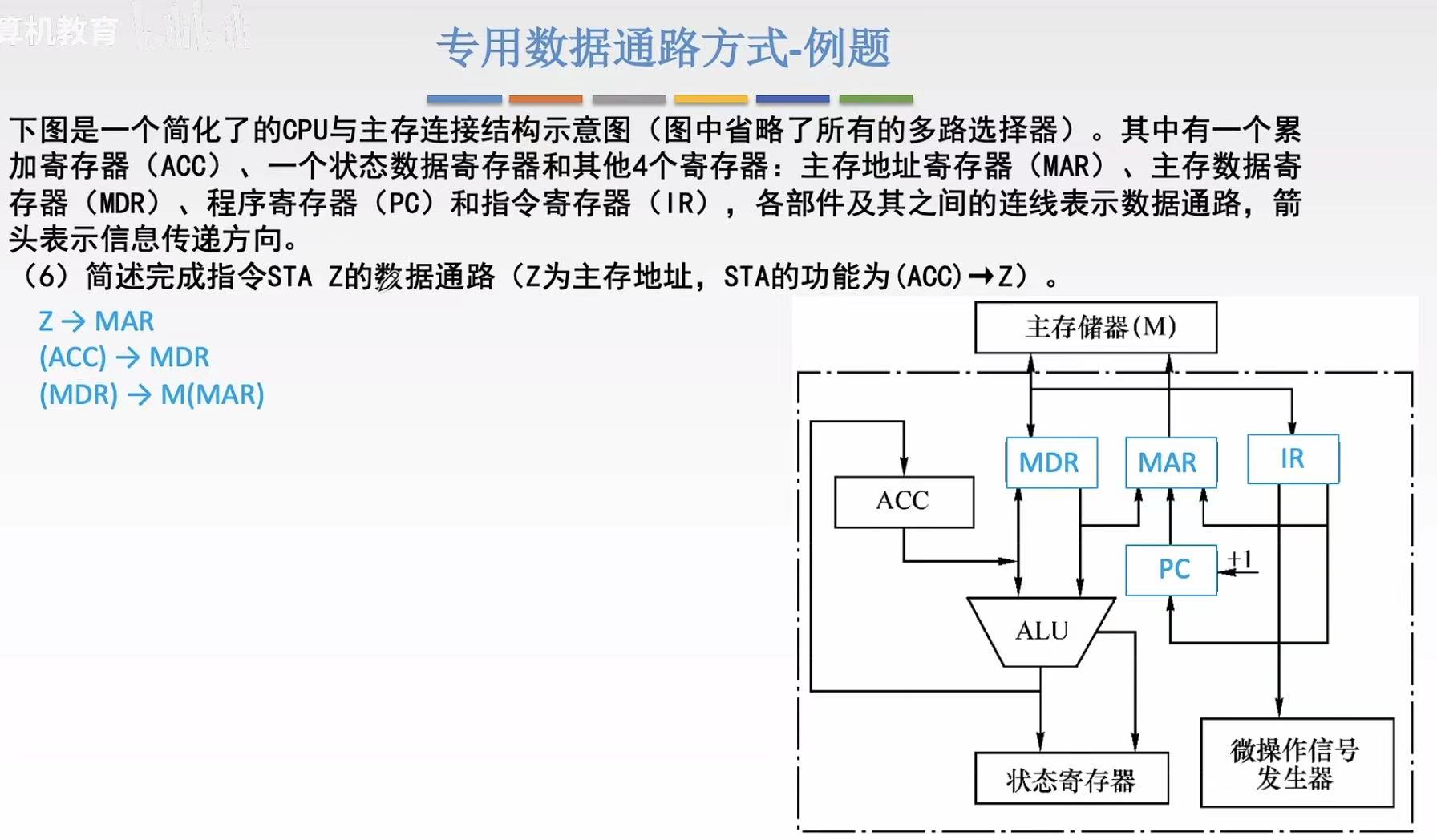

数据通路-专用通路结构

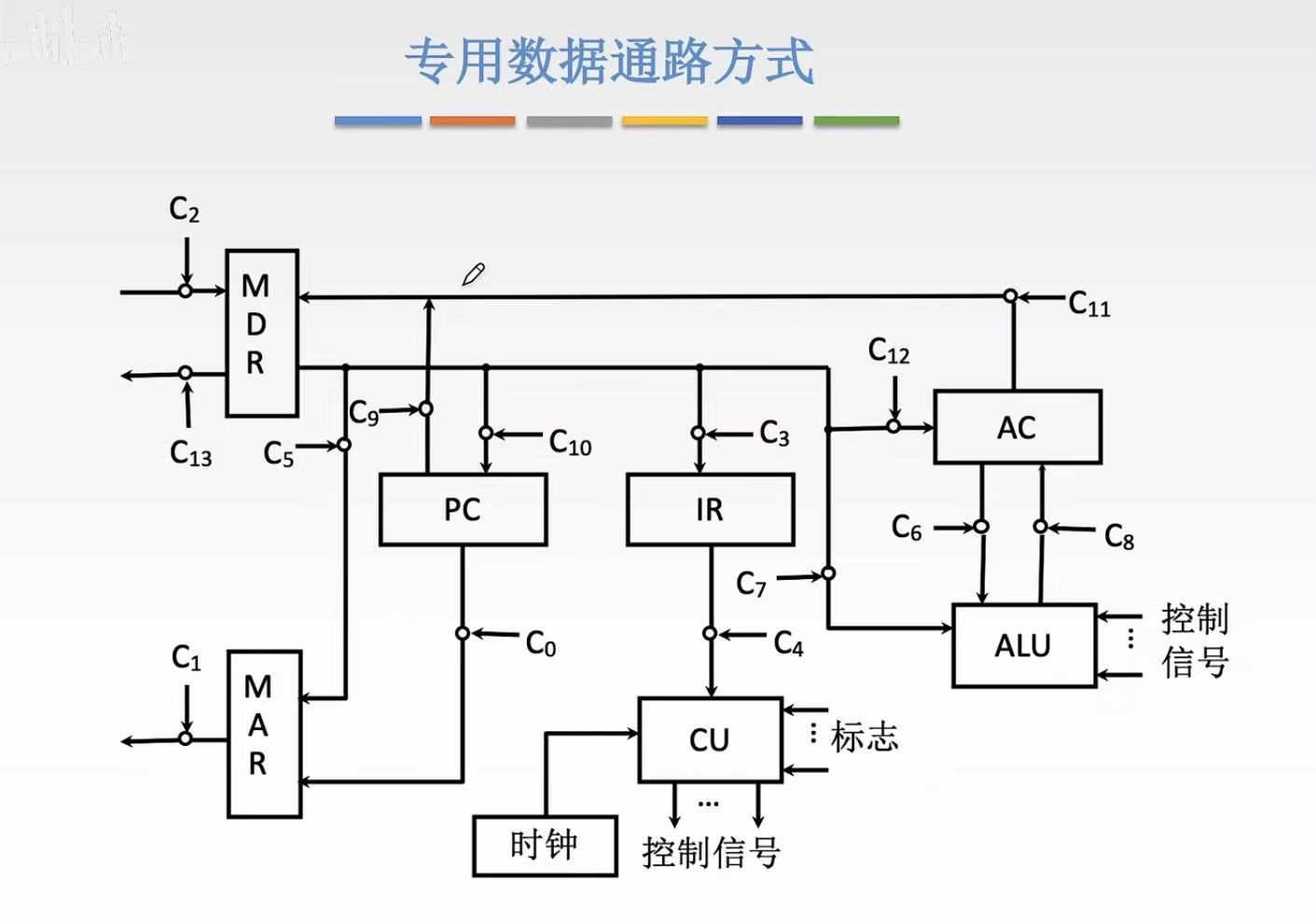

1. 专用数据通路方式

把总线优化掉了,谁可以和谁相连就单纯和它相连

就结构变了一点儿而已,其他的分析和之前相同(倒是做题技巧多了不少)

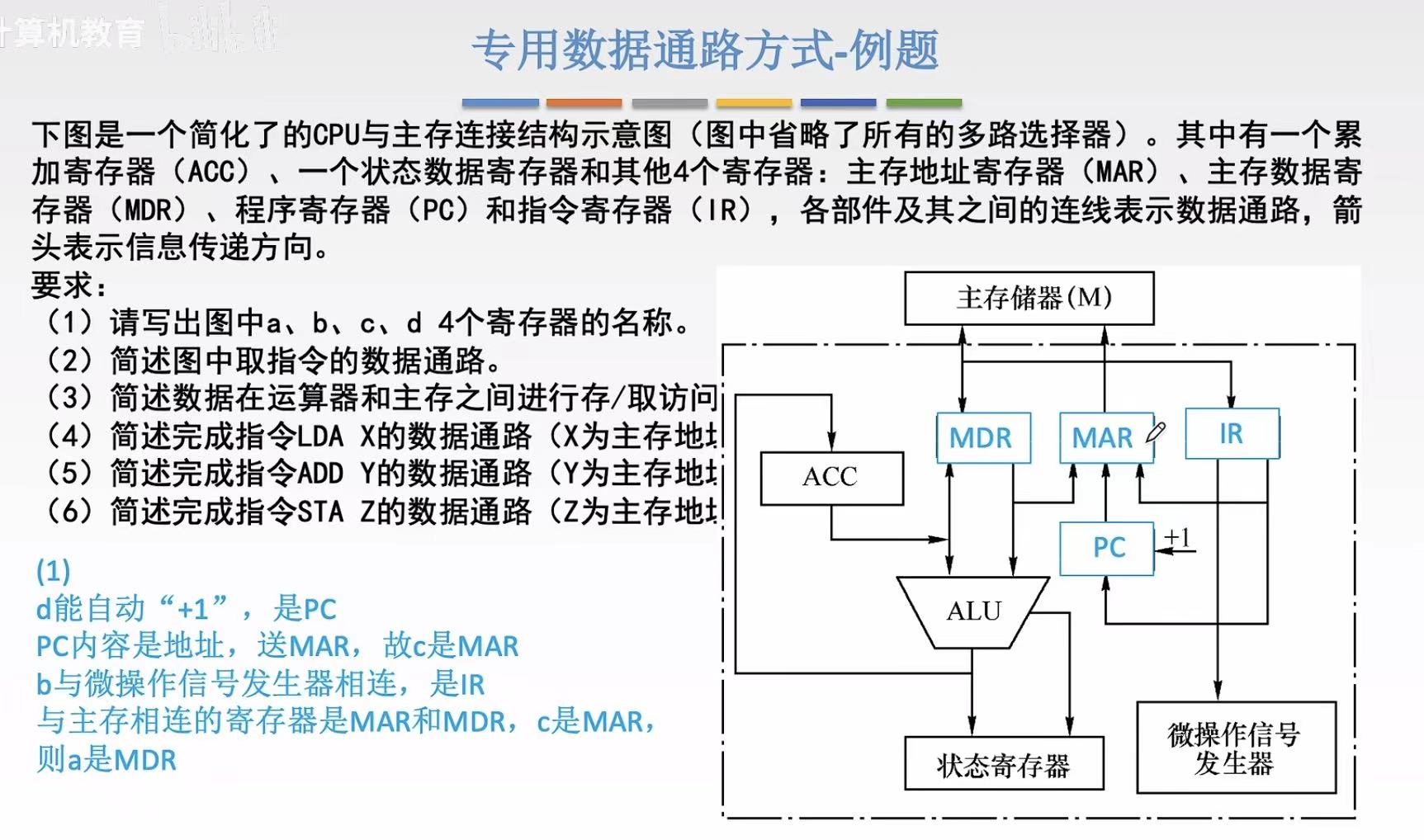

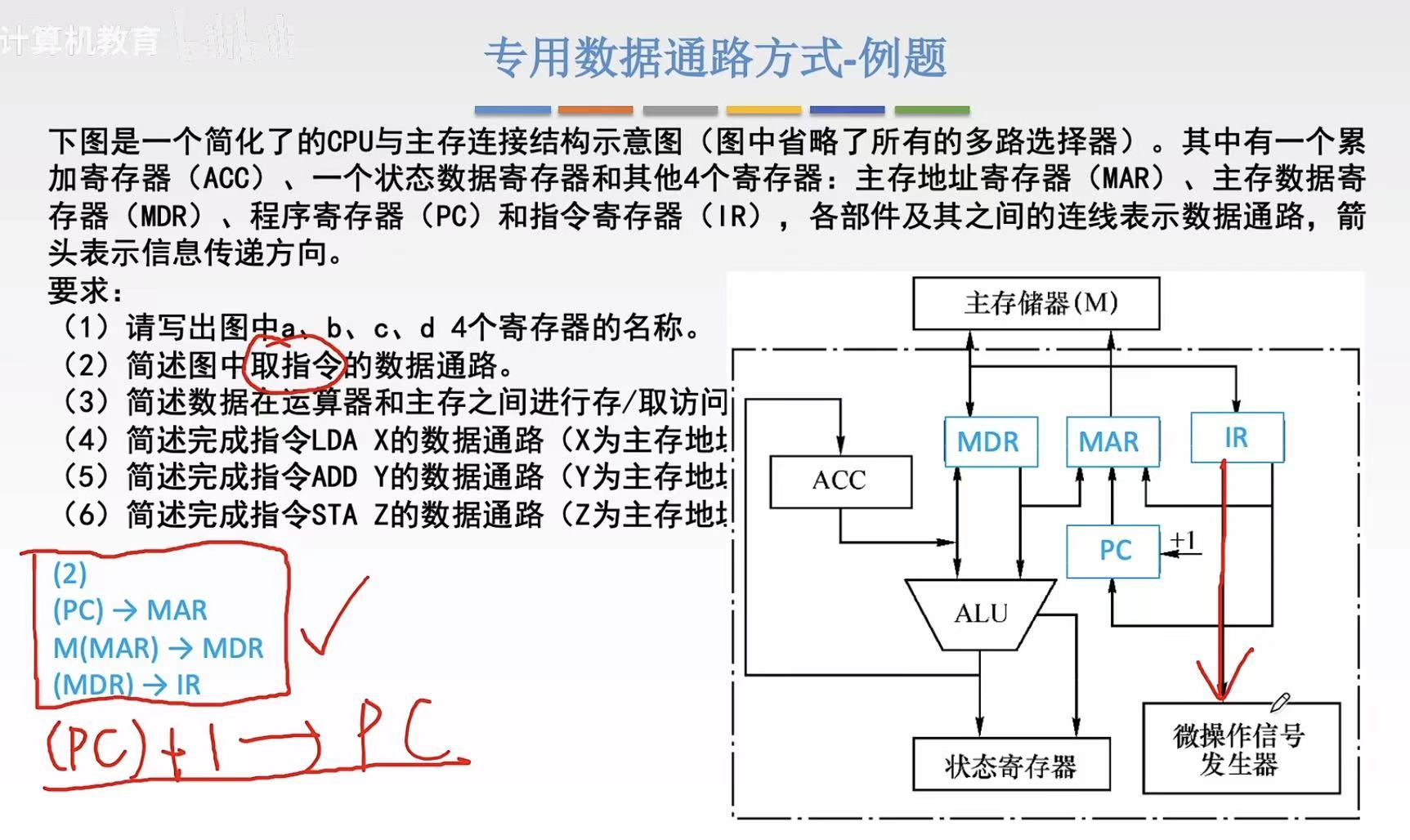

2. 例题

- MDR<-->主存<--MAR:和主存相连的只有MDR(双向)和MAR(单向)

- PC+1:能自动+1的肯定是PC

- IR -->微操作信号发生器:指向微操作信号发生器的一定是IR

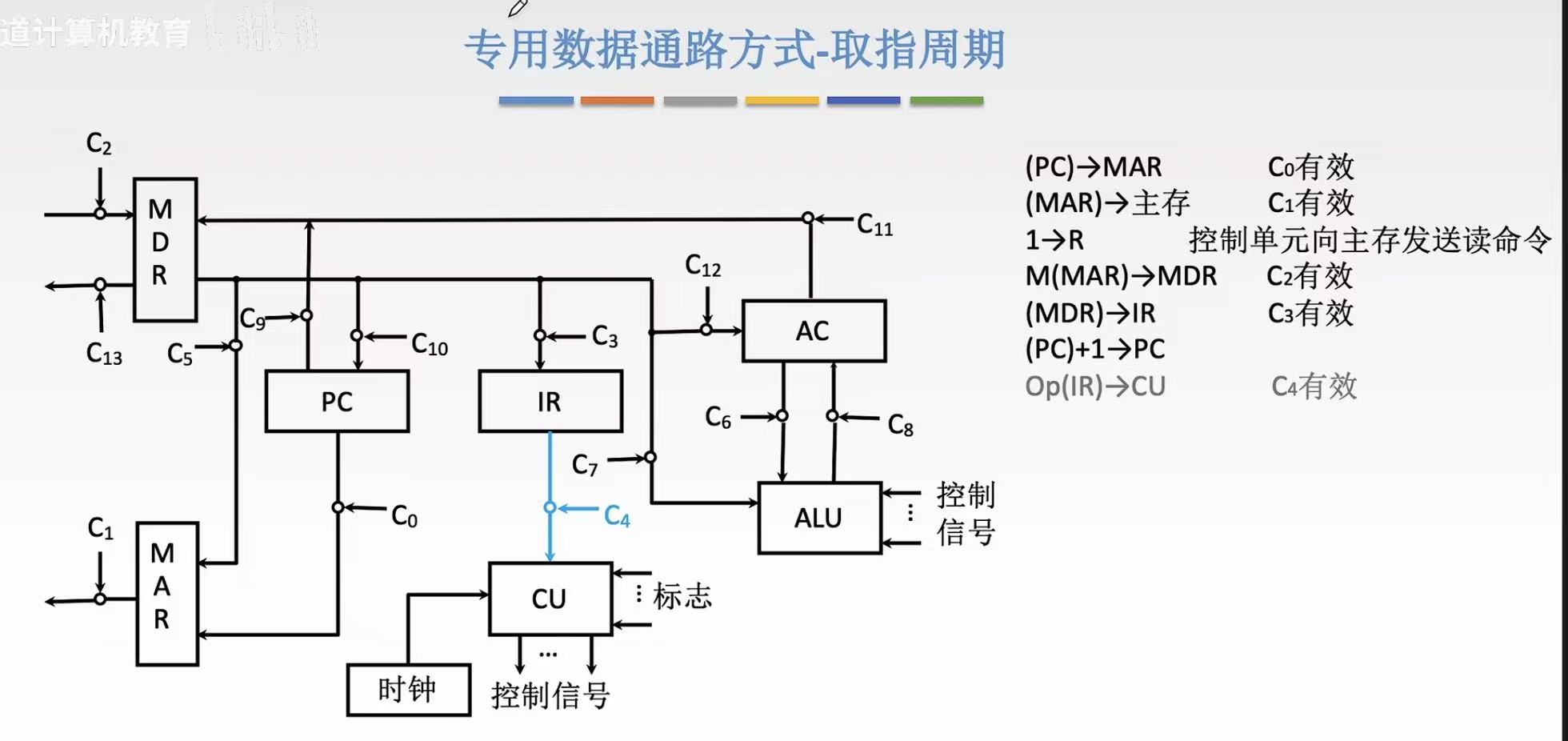

取指令-复习:

类比-公交车司机:

- PC → MAR 司机查看电子路单:"下一站是 第5站:中山公园"

→ : 把"中山公园"这个站名输入车载导航(MAR)

PC : 是"下一条指令地址" → 相当于"下一站编号/名称"

MAR: 是"当前要访问的地址" → 导航目的地 - 1 → R(读信号) 司机按下"查询站台信息"按钮 发出"读内存"请求,准备获取该站的详细信息

- M(MAR) → MDR 车载系统从数据库调出中山公园站的信息:"停靠30秒,开门下客,有换乘地铁2号线"

**内存(M)**中存储的是该站的操作指令(不是乘客!)

MDR 暂存这条"操作命令" - MDR → IR 司机看到屏幕显示:"停30秒,开门,可换乘"

→ : 他记住了这条指令(IR = 当前指令)

IR: 存储的是刚取到的指令内容,准备下一步执行 - PC + 1 → PC 司机更新路单:"下下站是 第6站:人民广场" 程序计数器自动+1,为下一次"取指"做准备

注意:下面的3、4、5、6是连在一起的执行步骤,所以4会按照3存储后的进度继续操作

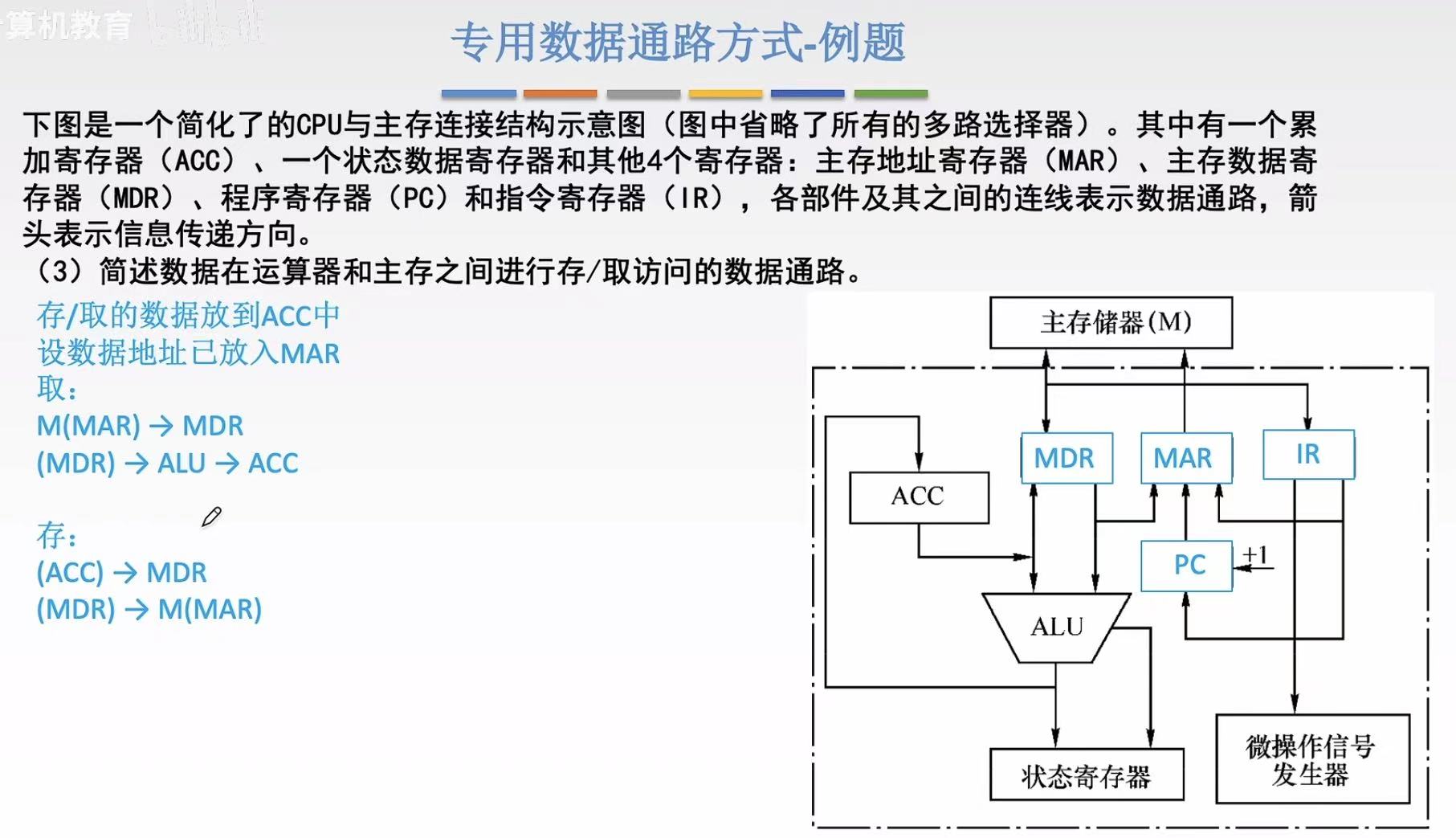

数据流经路径(图中带括号指的是数据本身):

取:MAR-->M-->MDR-->ALU-->ACC

存:ACC-->MDR-->M(MAR)(MAR指的位置)

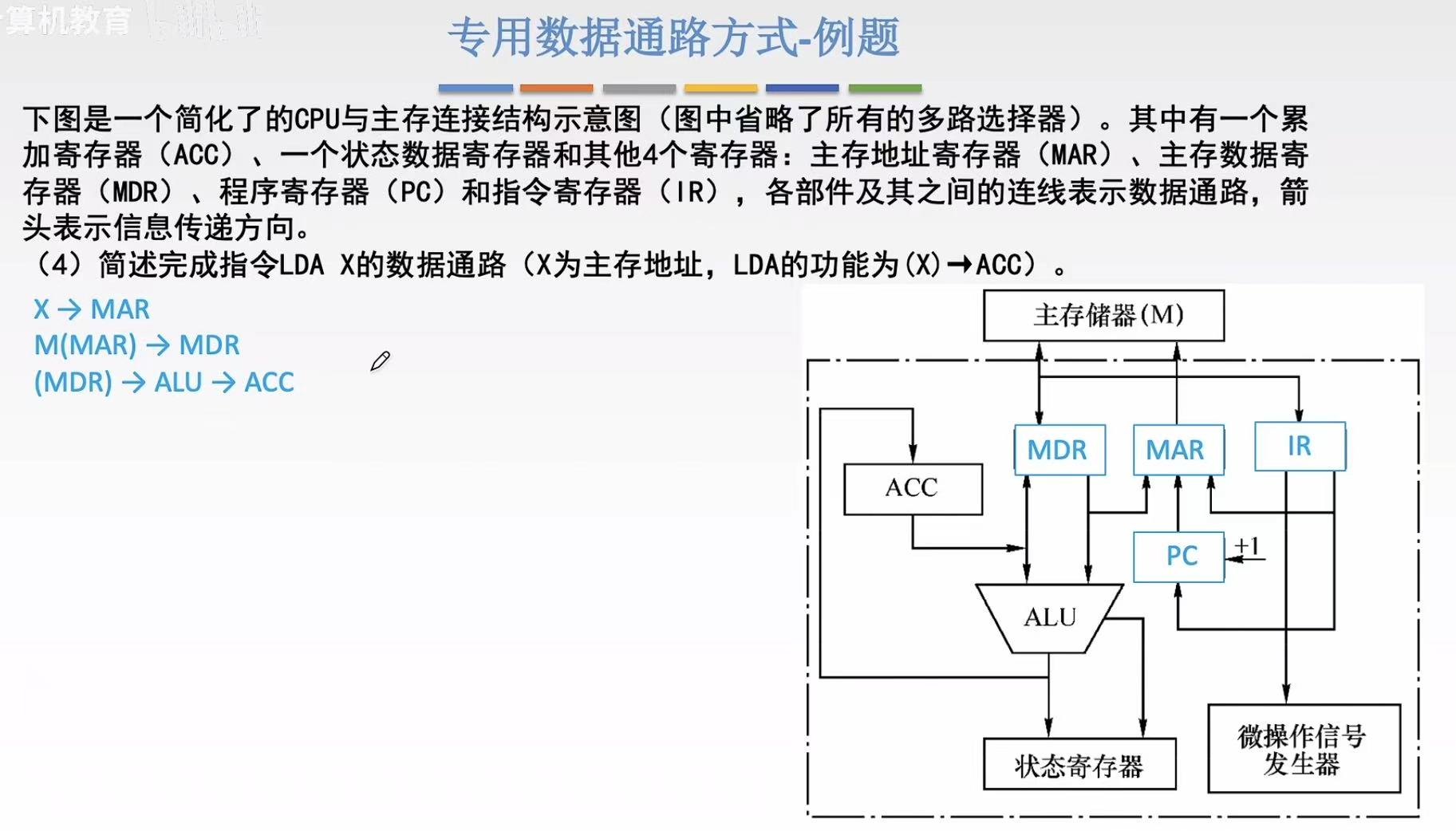

功能:把X指的主存地址中存储的数据放入ACC中

- X-->MAR:把主存地址存入地址寄存器中

- M(MAR)-->MDR:根据主存地址去主存中找到需要的数据,把数据放入数据寄存器

- (MDR)-->ALU-->ACC :把数据寄存器中的数据放入算术逻辑单元再放入累加器

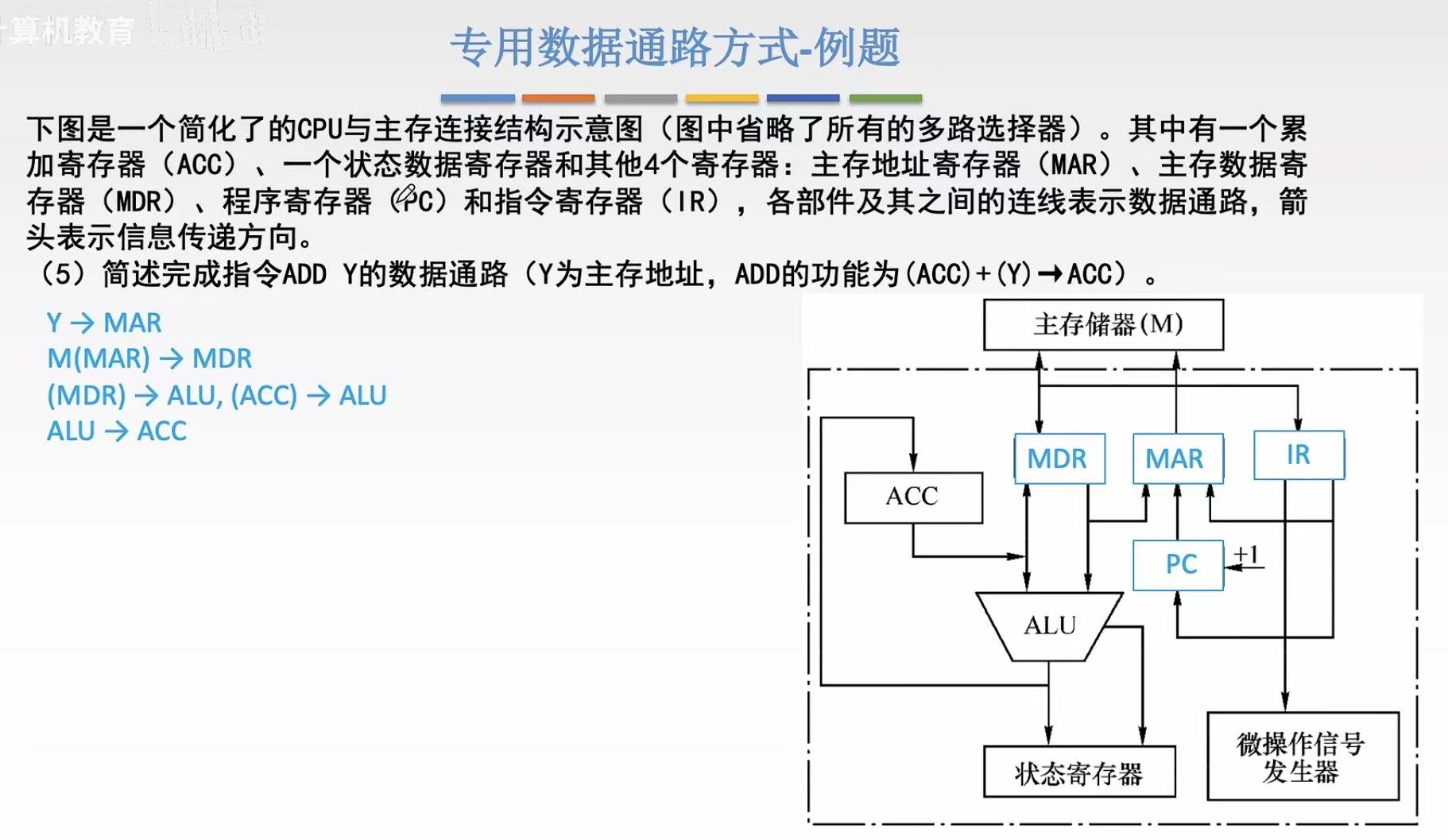

功能:把ACC中的数据(上一题存入的数据)和Y指的主存地址中的数据相加之后存入ACC - Y-->MAR:先把主存地址存入地址寄存器

- M(MAR)-->MDR:根据主存地址去主存中找到需要的数据,把数据放入数据寄存器

- (MDR)-->ALU:将数据寄存器中的数据放入ALU

- (ACC)-->ALU:将ACC中的数据放入ALU

- ALU-->ACC :ALU算出的数据存入ACC中

功能:将ACC中的数据存入Z指的主存地址中 - Z-->MAR:将主存地址存入地址寄存器中

- (ACC)-->MDR:将ACC(上一题得到的数据)存入数据寄存器中

- (MDR)-->M(MAR) :将数据寄存器中的数据存入地址寄存器指的主存中的位置

3. 小结

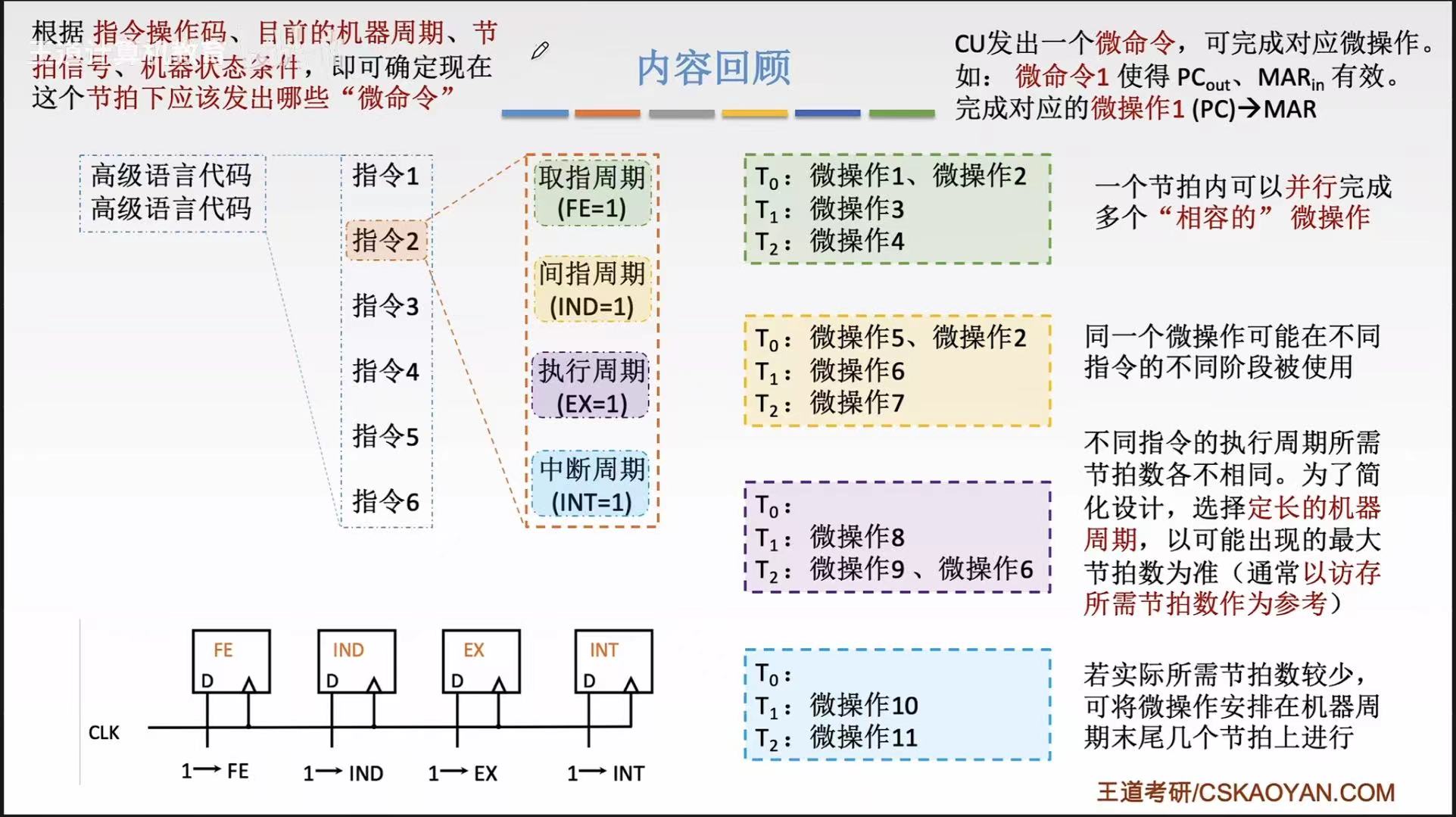

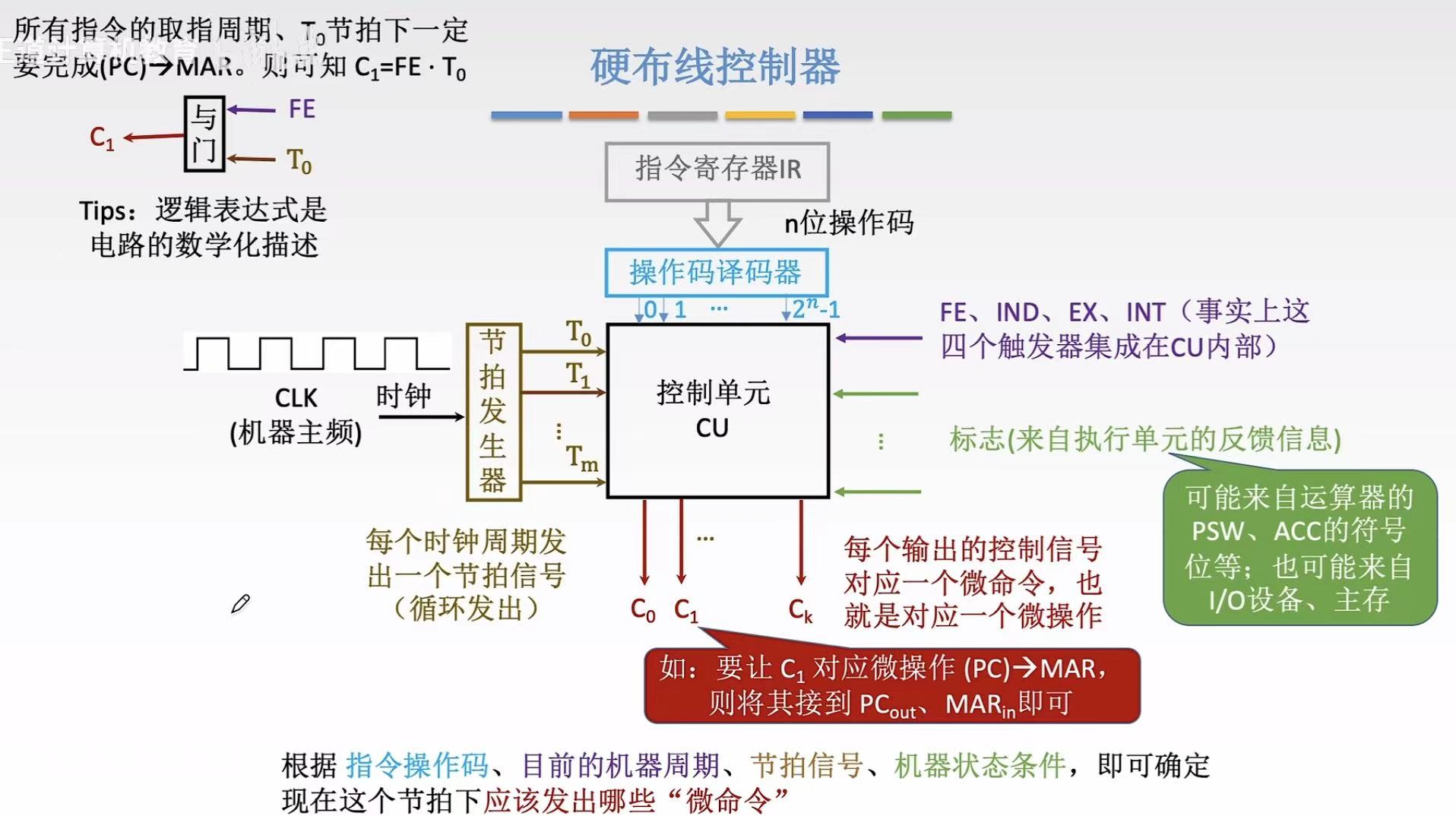

硬布线控制器

过于硬核,所以:【王道计算机考研 计算机组成原理】

1. 硬布线控制器

正常流程 :指令-->译码-->控制单元

影响因素 :节拍、触发器、标志

最终输出:一个具体的微操作

也就是,指令经过译码到达控制单元,同时会有各种因素来限制CU,最终得到这个指令需要进行的微操作。

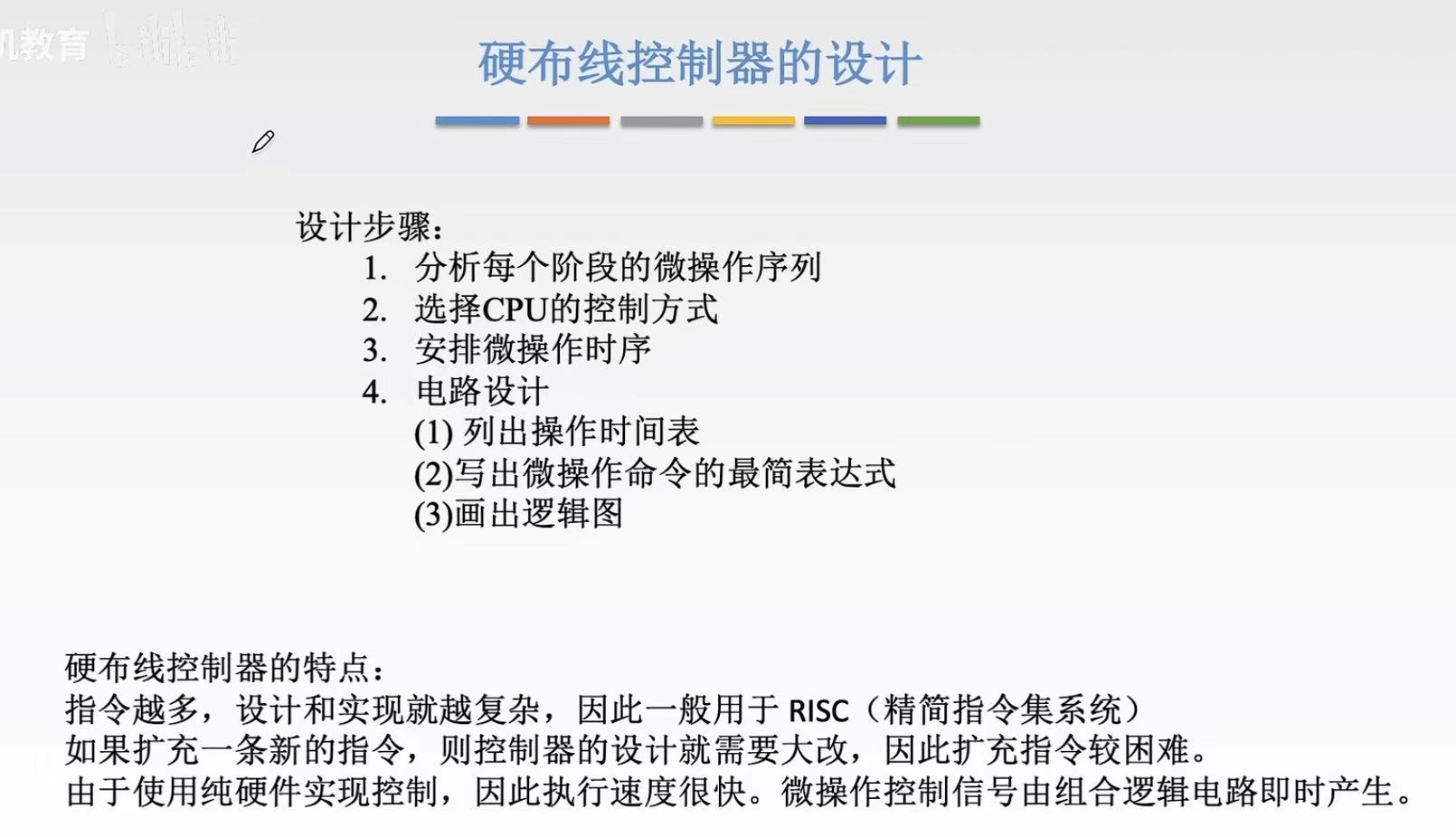

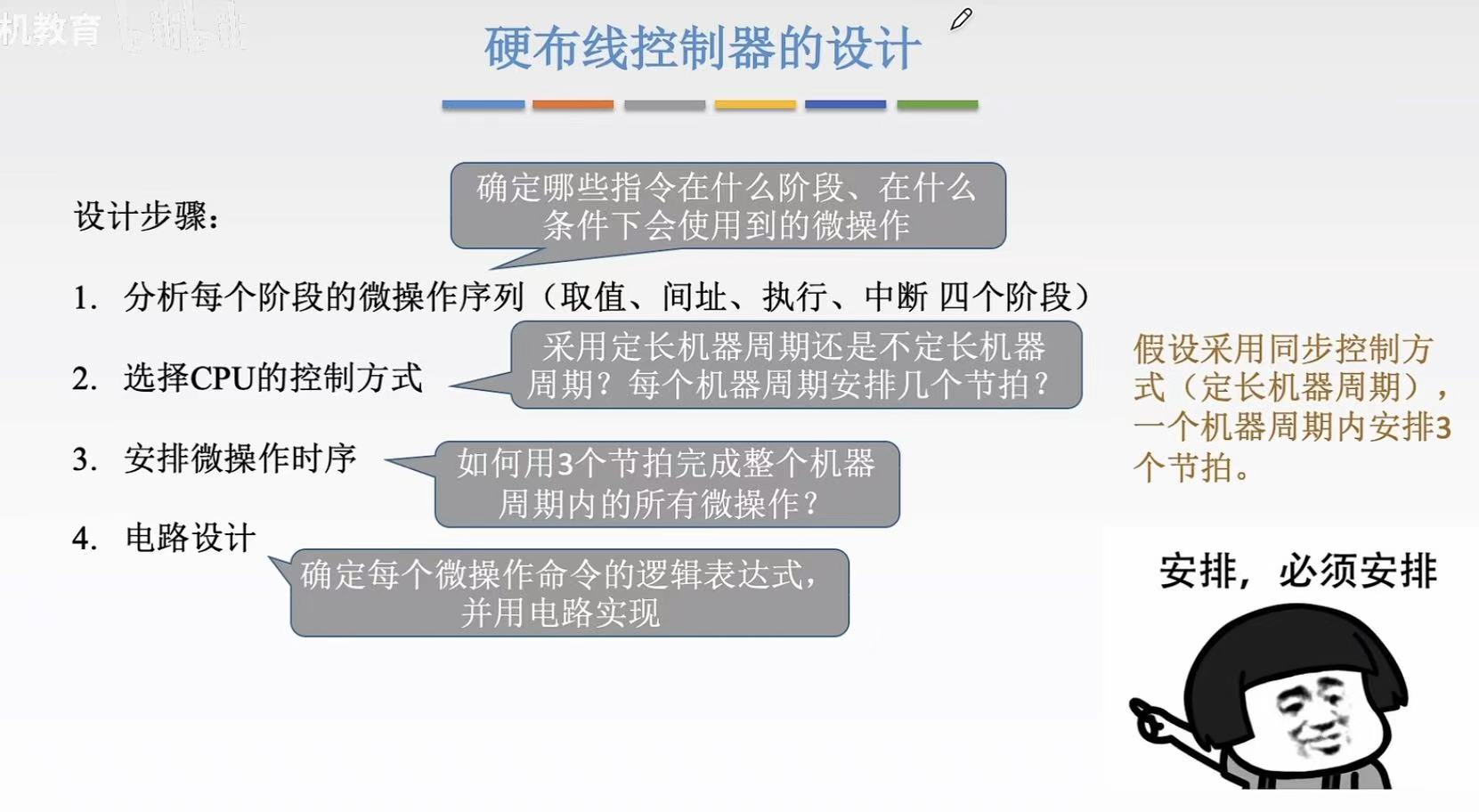

2. 设计(了解)

大前提 :得到逻辑表达式 =可以画出电路图

概括 :下面的步骤,挨个儿完成之后就可以得到一个逻辑表达式,我们就可以根据这个逻辑表达式画出电路图,不考 。

这是设计步骤:

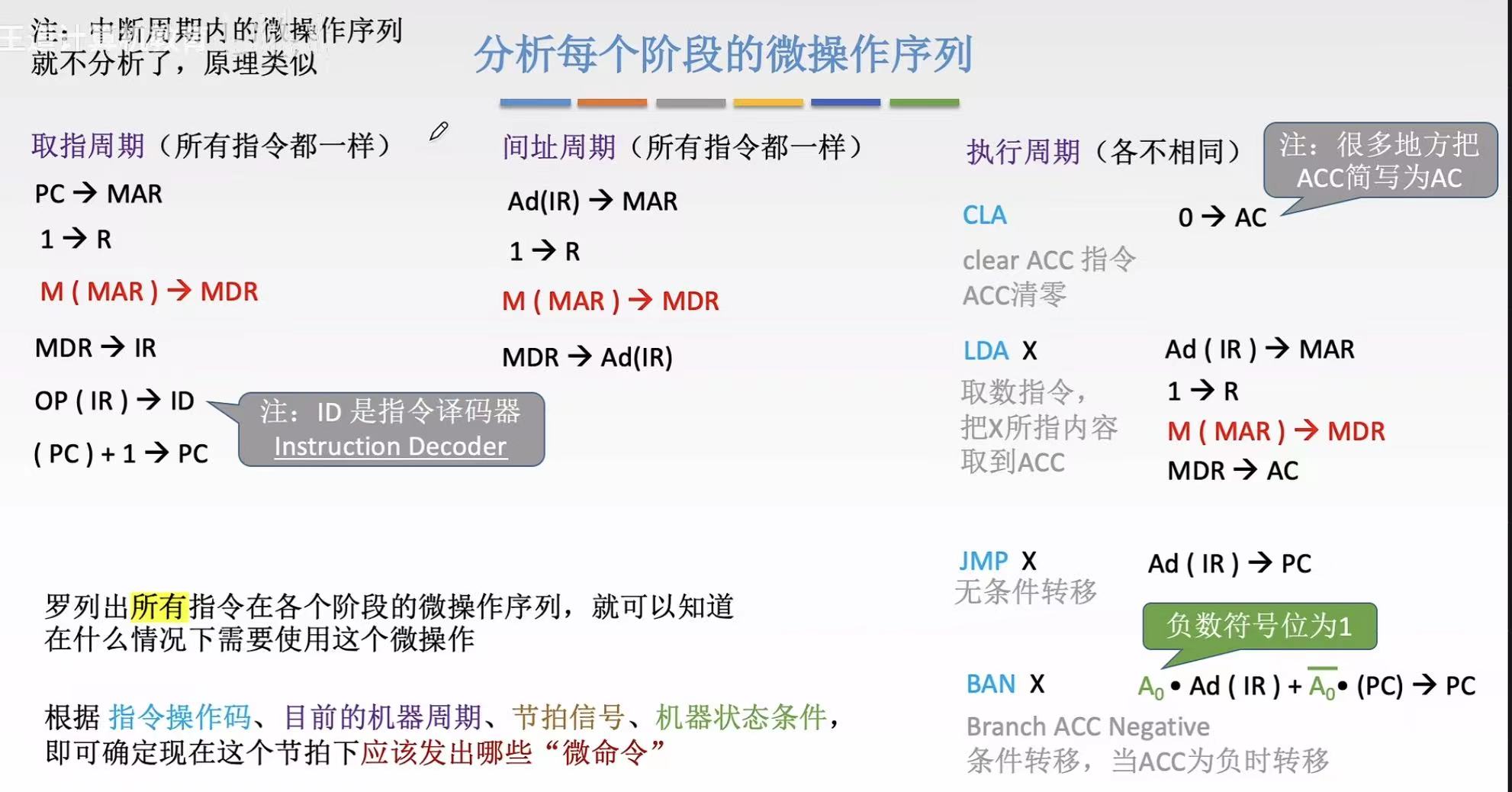

2.1 分析每个阶段的微操作序列

纯手动,把所有需要的指令都列出来

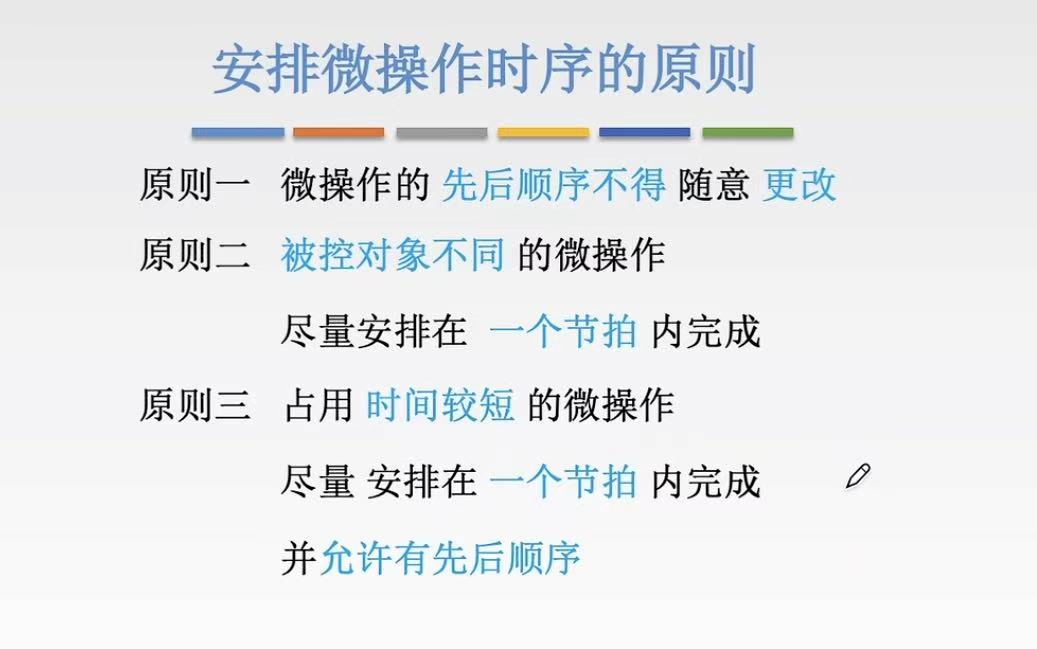

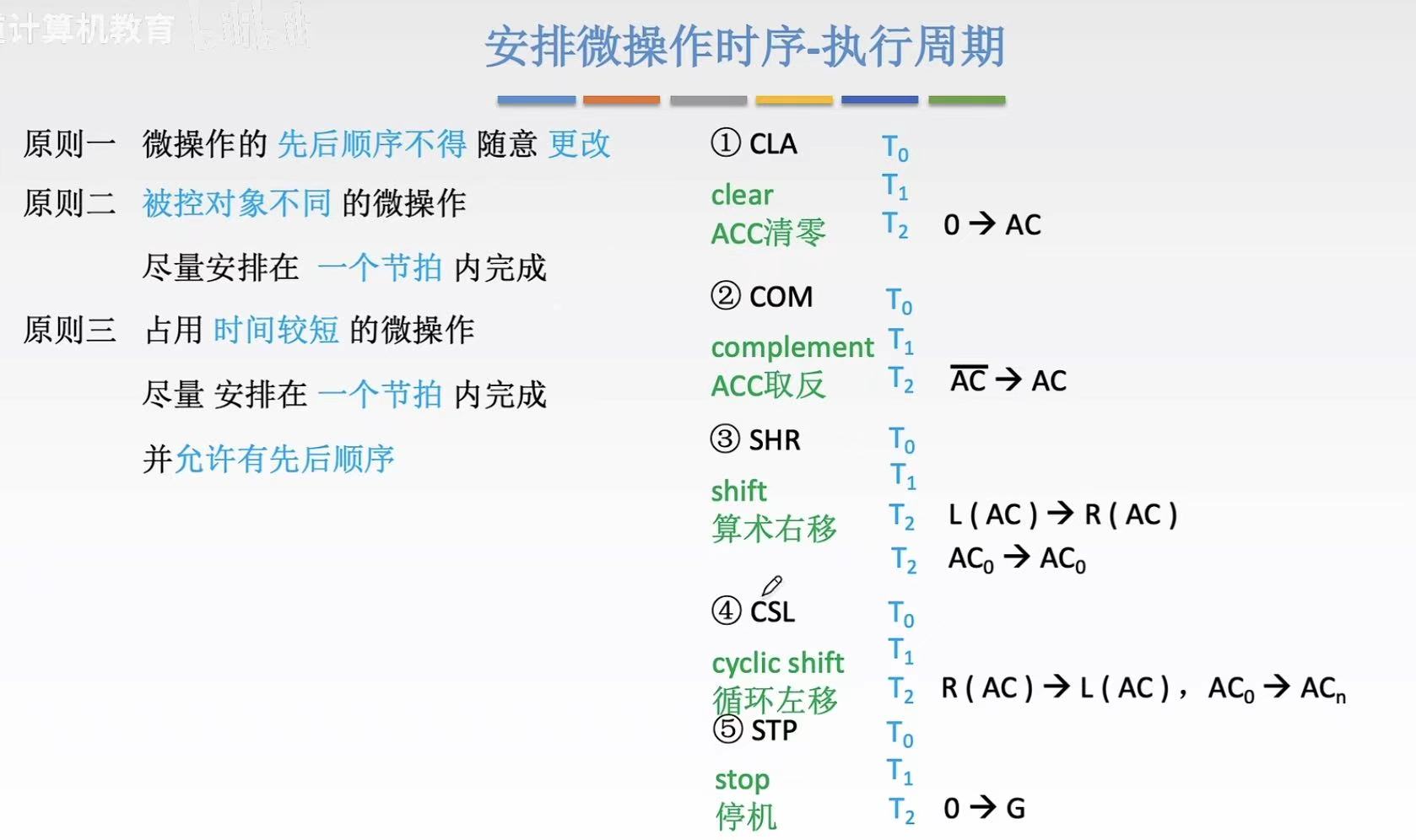

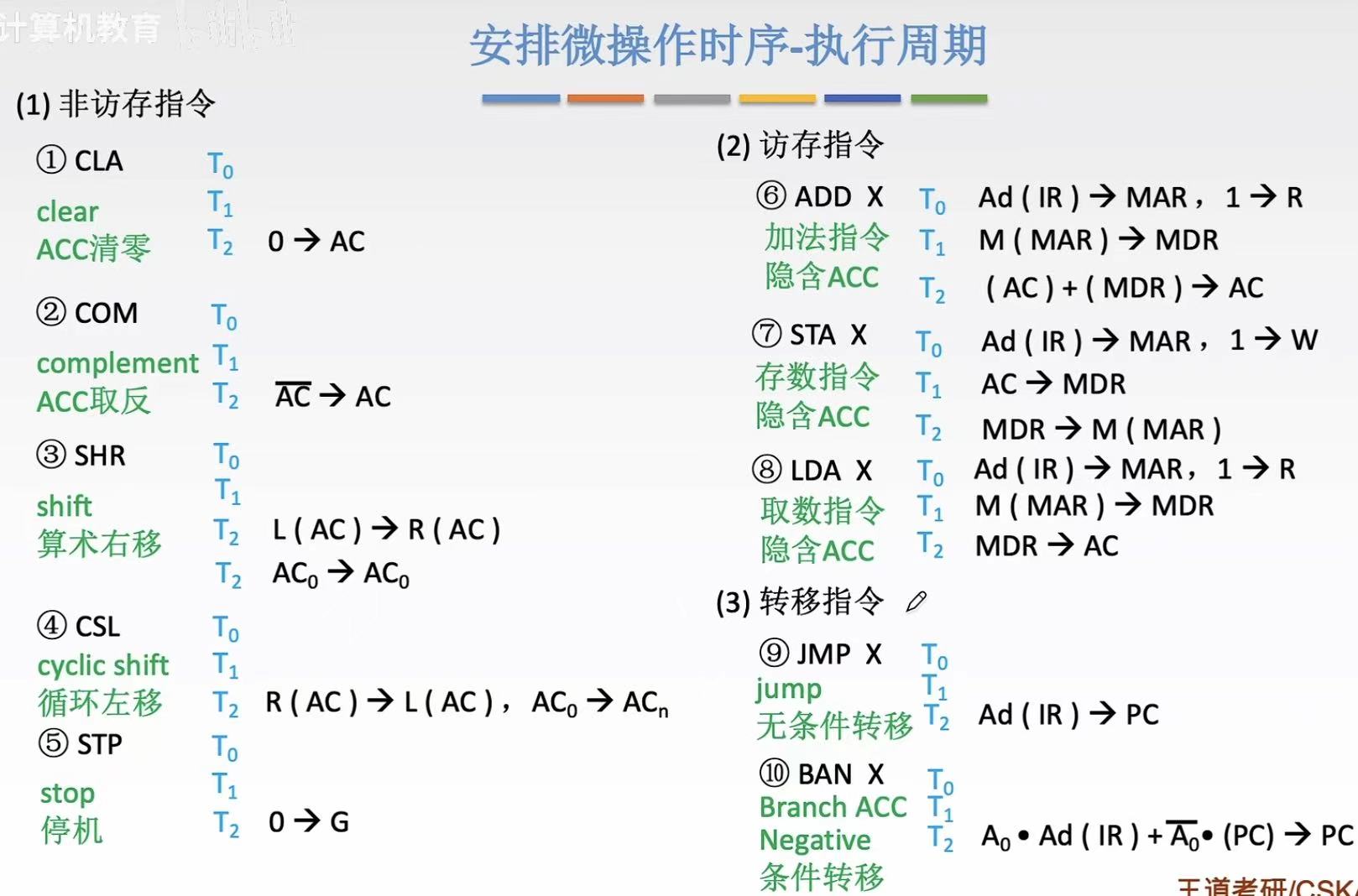

2.2 安排微操作时序的原则

都安排定长(简单),分配节拍。

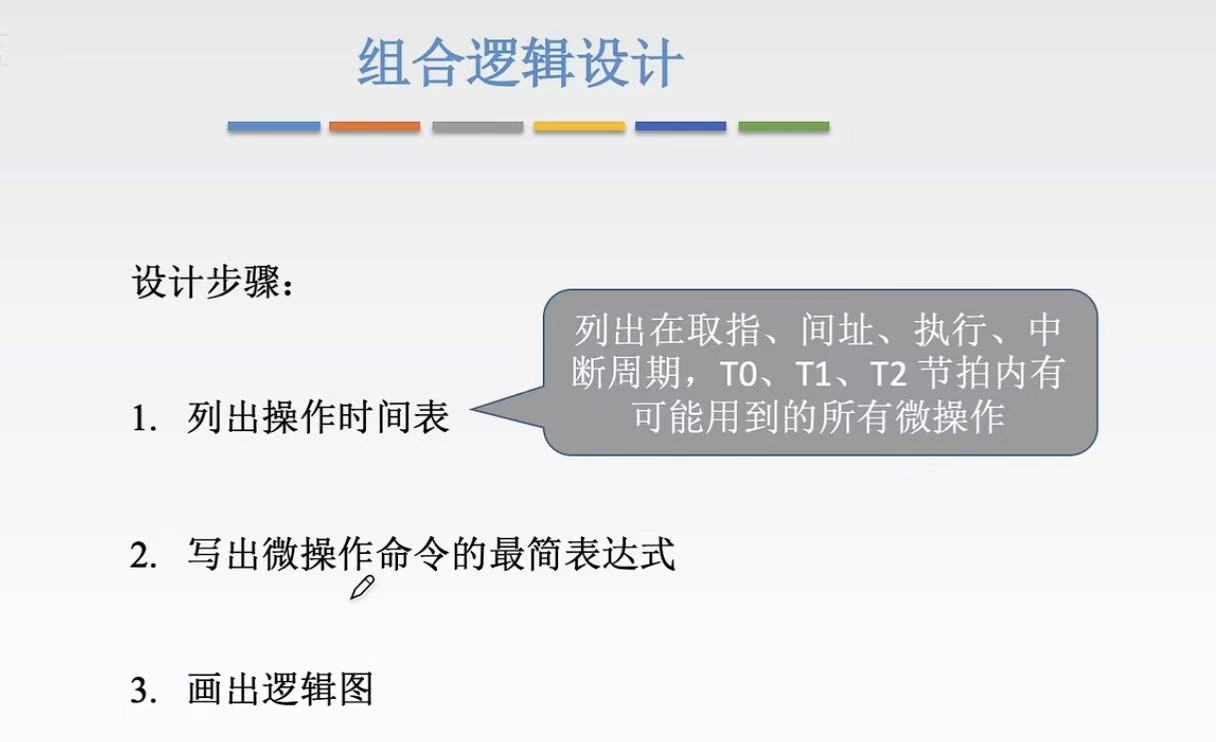

2.3 组合逻辑设计

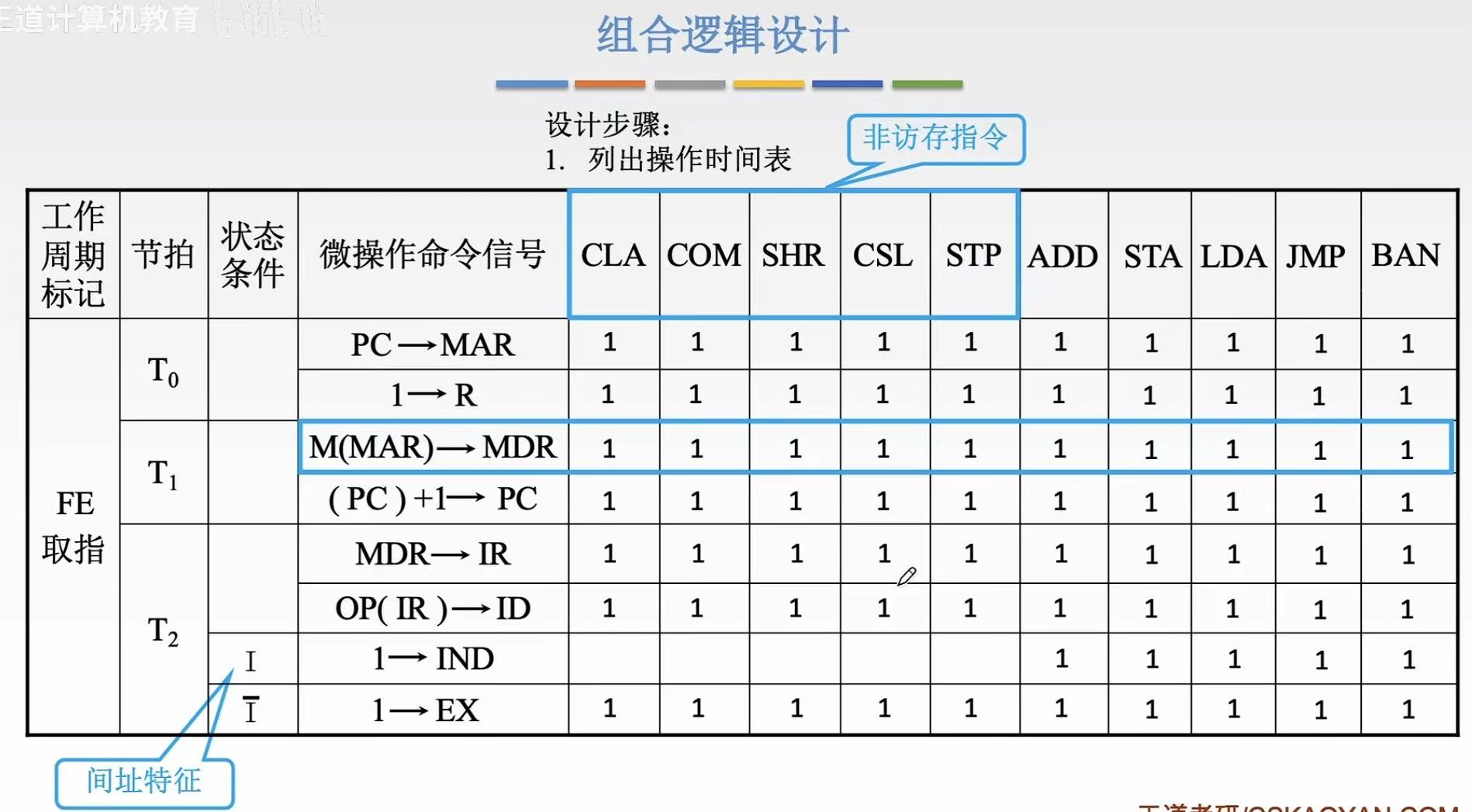

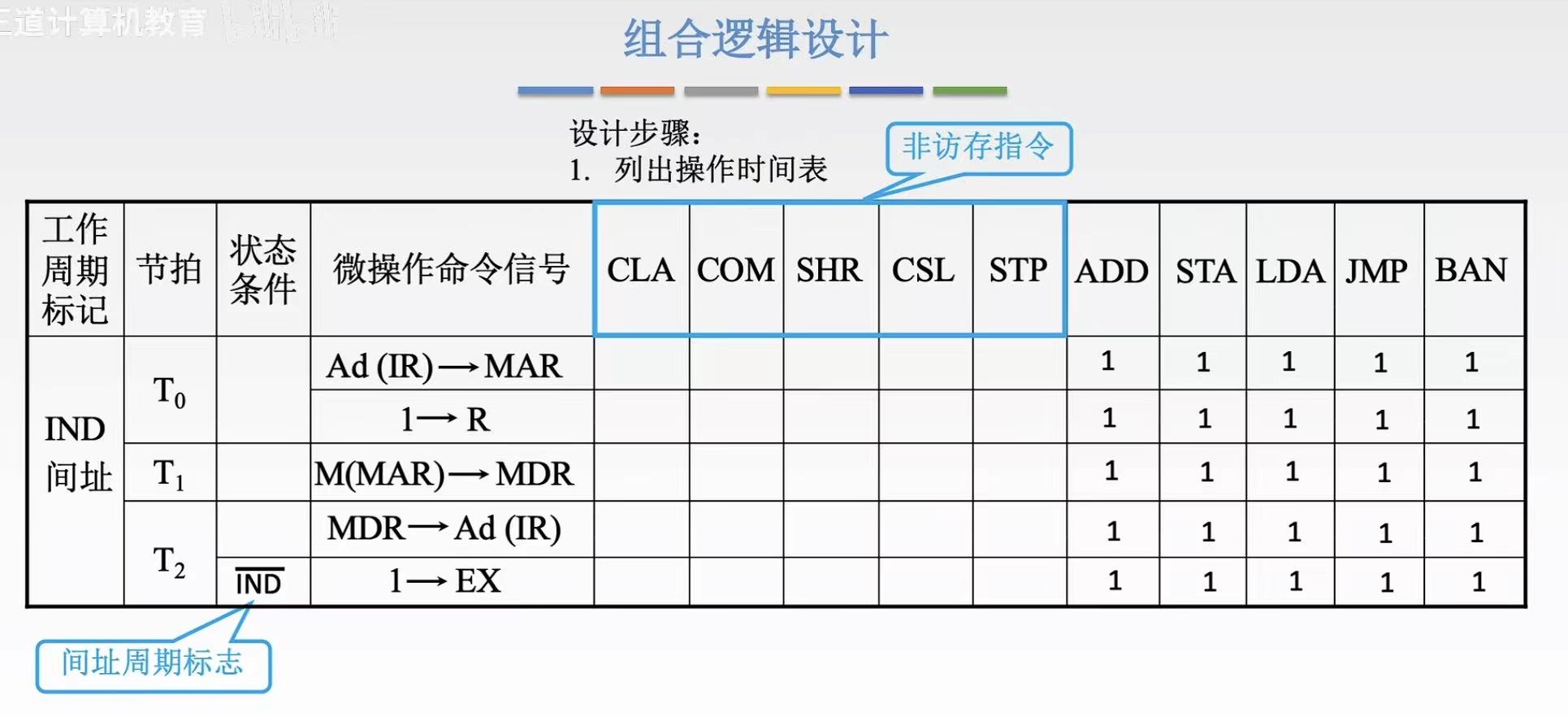

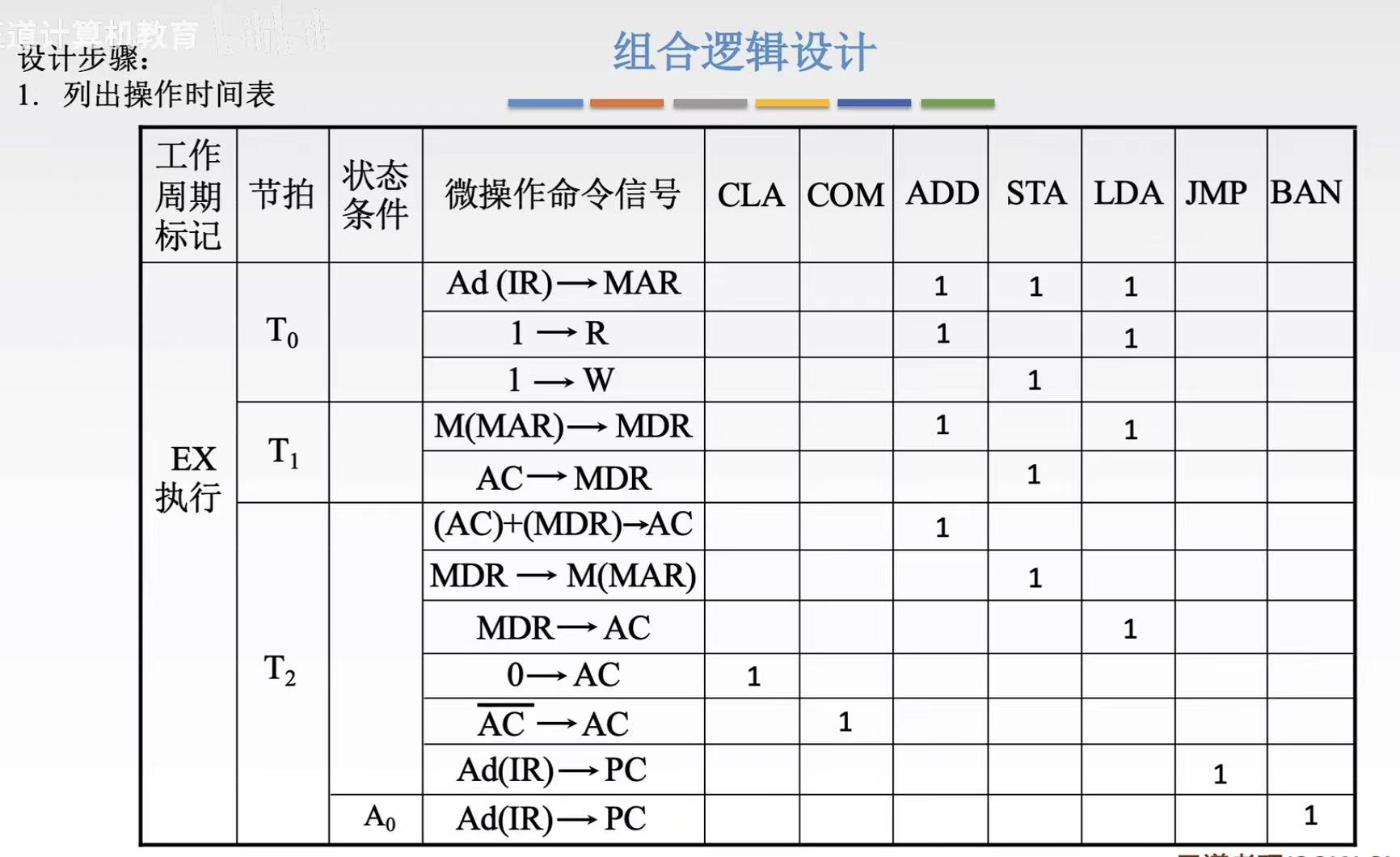

取指周期:公共操作,啥指令都会执行读主存操作,所以都是1

间址周期:需要数据的指令就需要读主存,这些指令都是1.

执行周期:具体指令具体分析

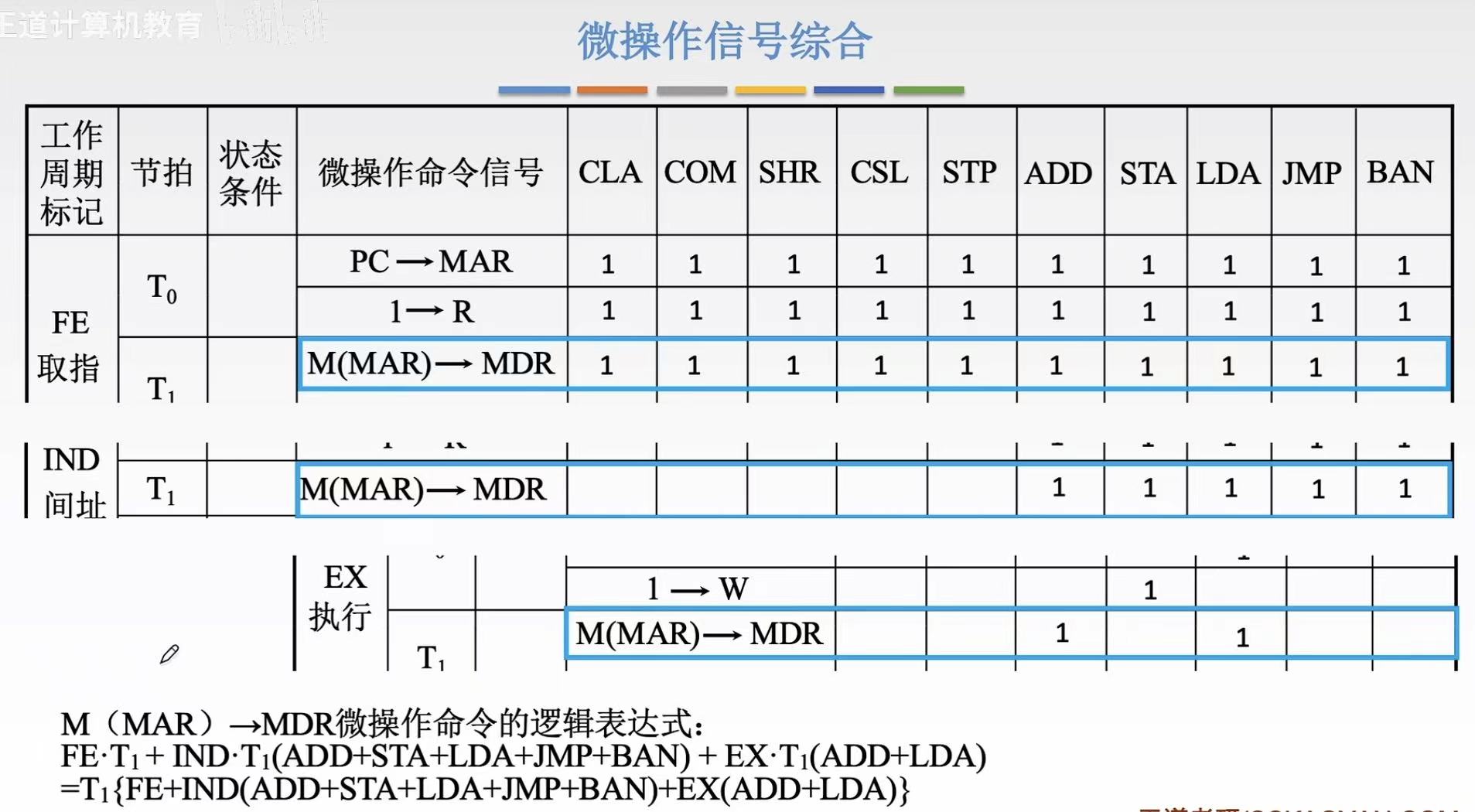

2.4 微操作信号综合

根据1,就可以得到逻辑表达式(建议学一下数字电路,虽然但是过程挺无脑的)

简述:

- FE·T1:FE是取指周期,T1是蓝色框住的指令,·表示FE的时候这个指令全部都是1,就是都执行。

- IND...:IND时期,T1的这个指令中有ADD...这些指令是执行的(把是1的都写在括号里加起来)

- EX... :同上,最后把这几个时期的都加在一起就完事儿了

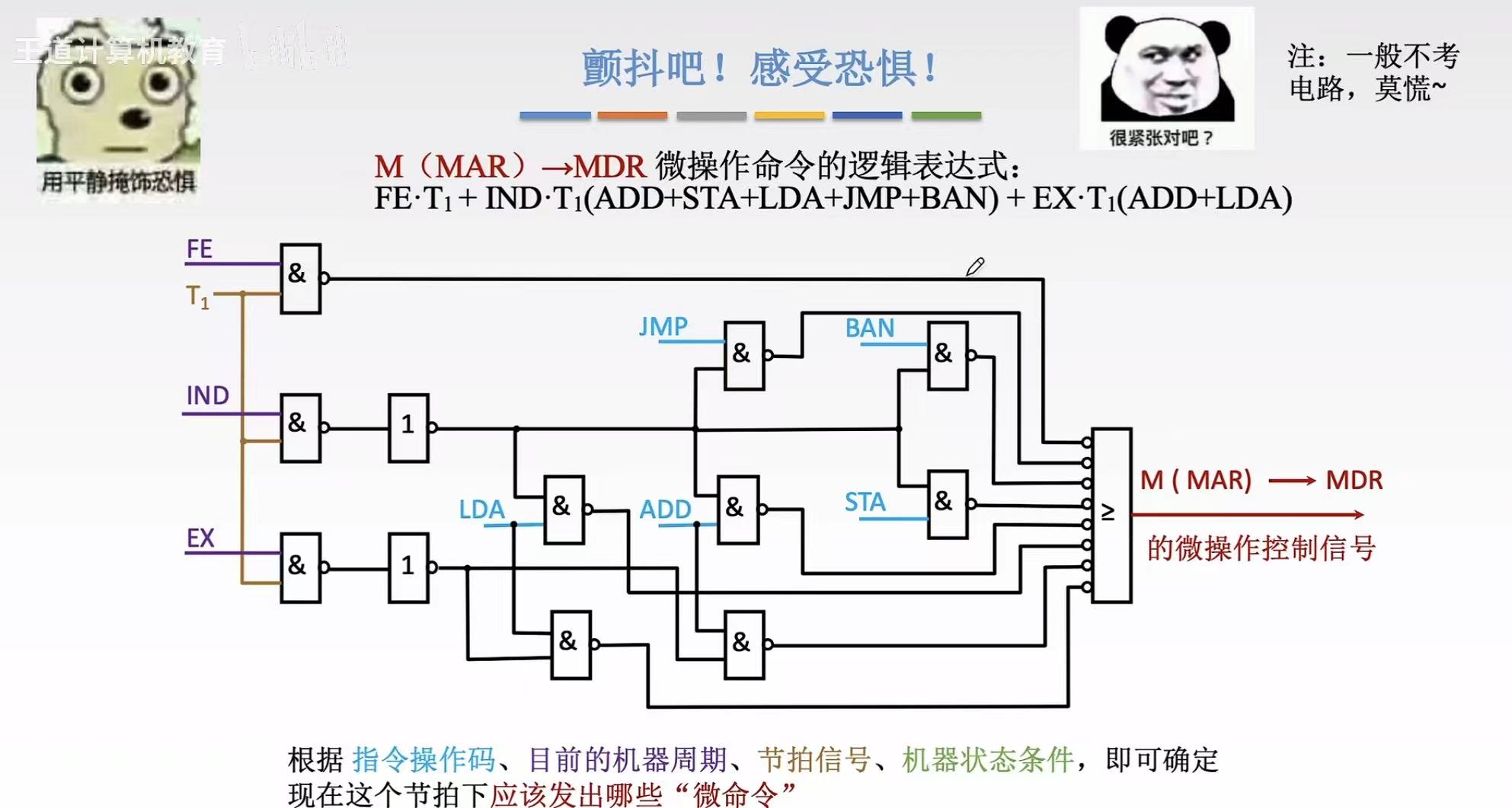

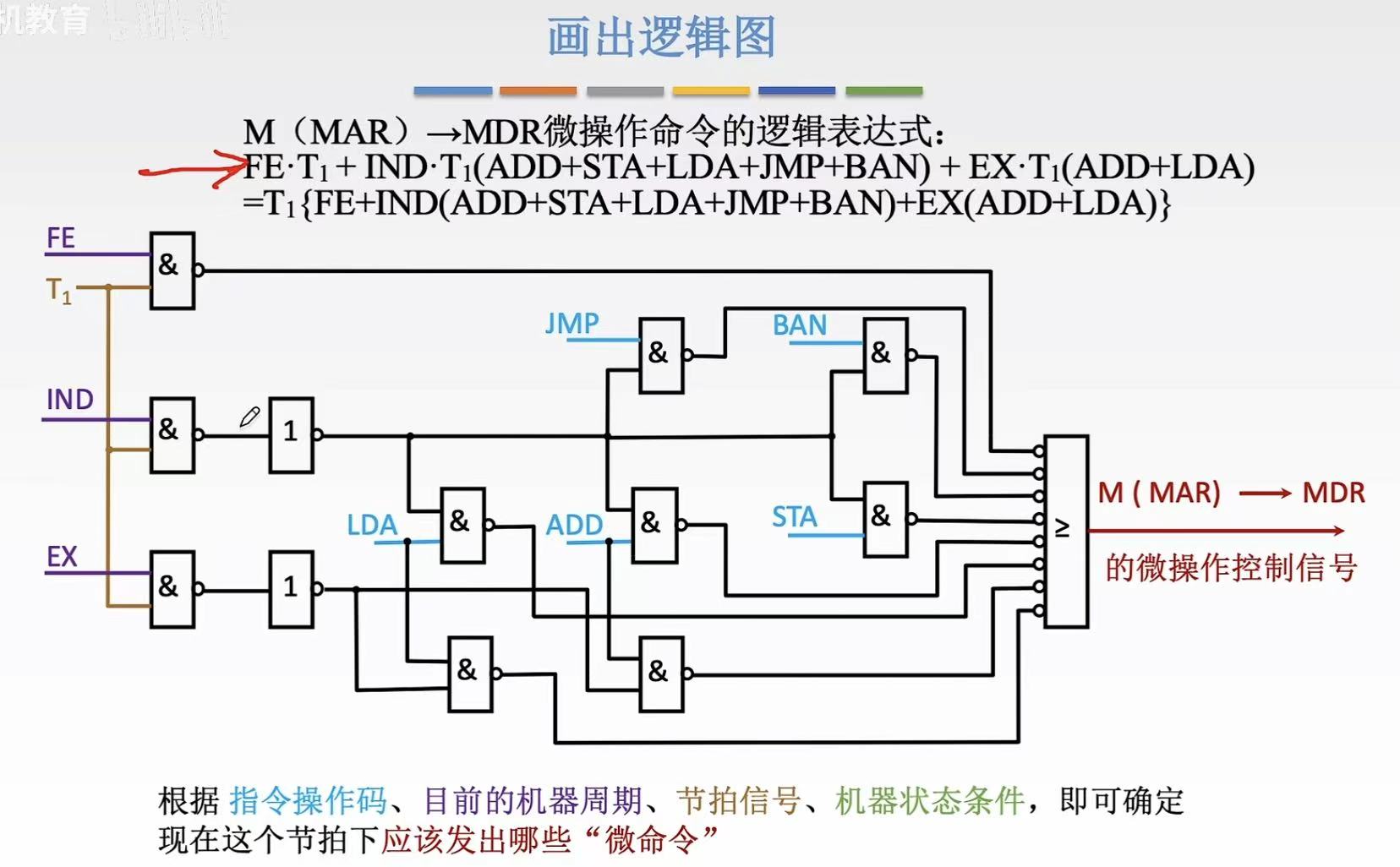

2.5 画出逻辑图

然后根据逻辑表达式:·就是与,+就是或,排好每个指令之间的关系,你就可以得到这么一个逻辑图:

3. 小结