文章目录

- 术语翻译

- [1. 短路自检要求](#1. 短路自检要求)

-

- [1.1 几种短路检测的流程图](#1.1 几种短路检测的流程图)

-

- [1.1.1 短路高边自检](#1.1.1 短路高边自检)

- [1.1.2 短路低边自检流程图](#1.1.2 短路低边自检流程图)

- [1.1.3 Normal 模式下的短路检测](#1.1.3 Normal 模式下的短路检测)

- [2. 短路高边自检](#2. 短路高边自检)

-

- [2.1 高边自检相关寄存器和引脚](#2.1 高边自检相关寄存器和引脚)

-

- [2.1.1 dsm_hsx](#2.1.1 dsm_hsx)

- [2.1.2 Err_scd](#2.1.2 Err_scd)

- [2.1.3 错误引脚 ERR_N](#2.1.3 错误引脚 ERR_N)

- [2.2 与短路自检相关的参数](#2.2 与短路自检相关的参数)

-

- [2.2.1 消隐时间和滤波时间](#2.2.1 消隐时间和滤波时间)

- [2.2.2 死区时间](#2.2.2 死区时间)

- [3. 易错点和注意点](#3. 易错点和注意点)

-

- [3.1 ENA复位](#3.1 ENA复位)

- [3.2 自检模式](#3.2 自检模式)

- [3.3 短路诊断时序图分析](#3.3 短路诊断时序图分析)

- [3.4 复位方式](#3.4 复位方式)

- [4. 实操中的误区](#4. 实操中的误区)

- 参考文档

术语翻译

对官方文档中的名词翻译如下:

- Self Test Short Circuit Detection High-side: 短路高边自检

- Self Test Short Circuit Detection Low-side: 短路低边自检

- a Short Circuit Detection Test in Normal Operation Mode: Normal模式下的短路检测

- self test mode: 自检模式

1. 短路自检要求

根据文档,短路检测包括以下几种,正常情况下,都要进行检测:

- 短路高边自检

- 短路低边自检

- Normal模式下的短路检测

1.1 几种短路检测的流程图

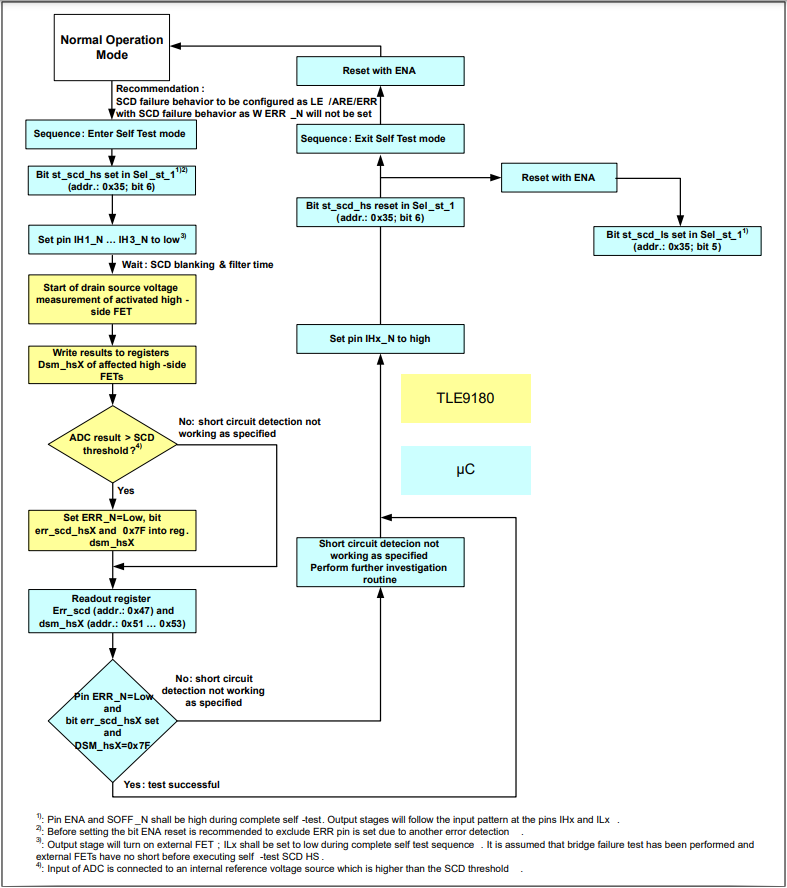

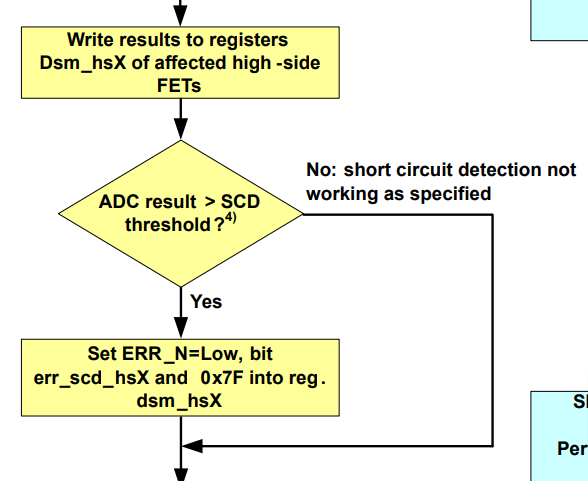

1.1.1 短路高边自检

由流程图可以看出,高边自检需要全程在自检模式下进行。高边检测结束复位st_scd_st后,可以退出自检模式,也可以在ENA复位后,直接进行短路低边自检,而不用退出自检模

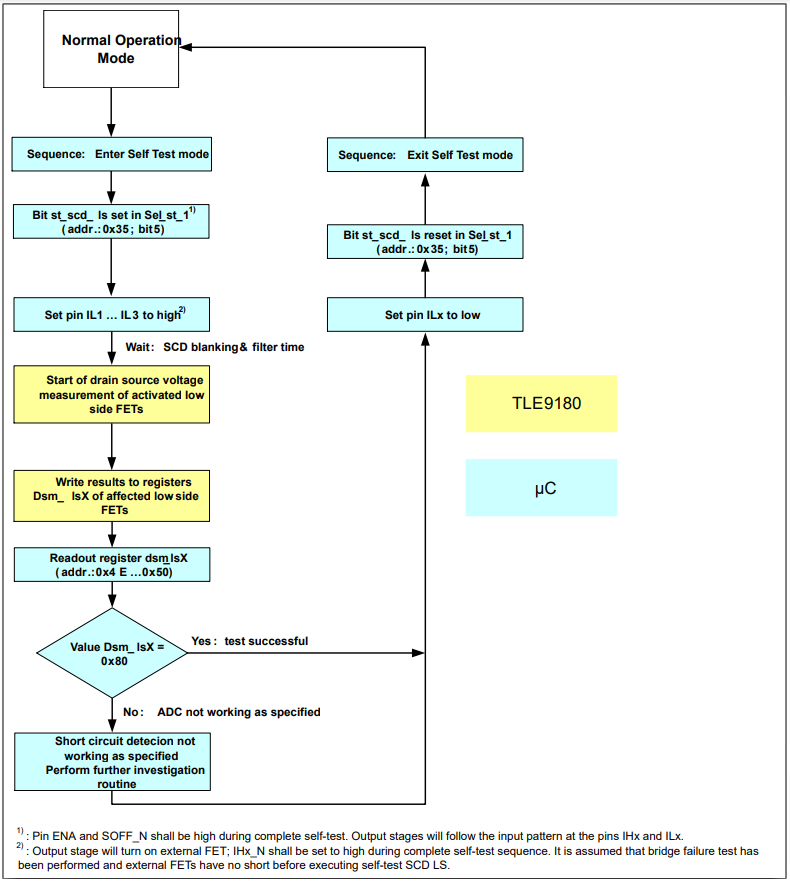

1.1.2 短路低边自检流程图

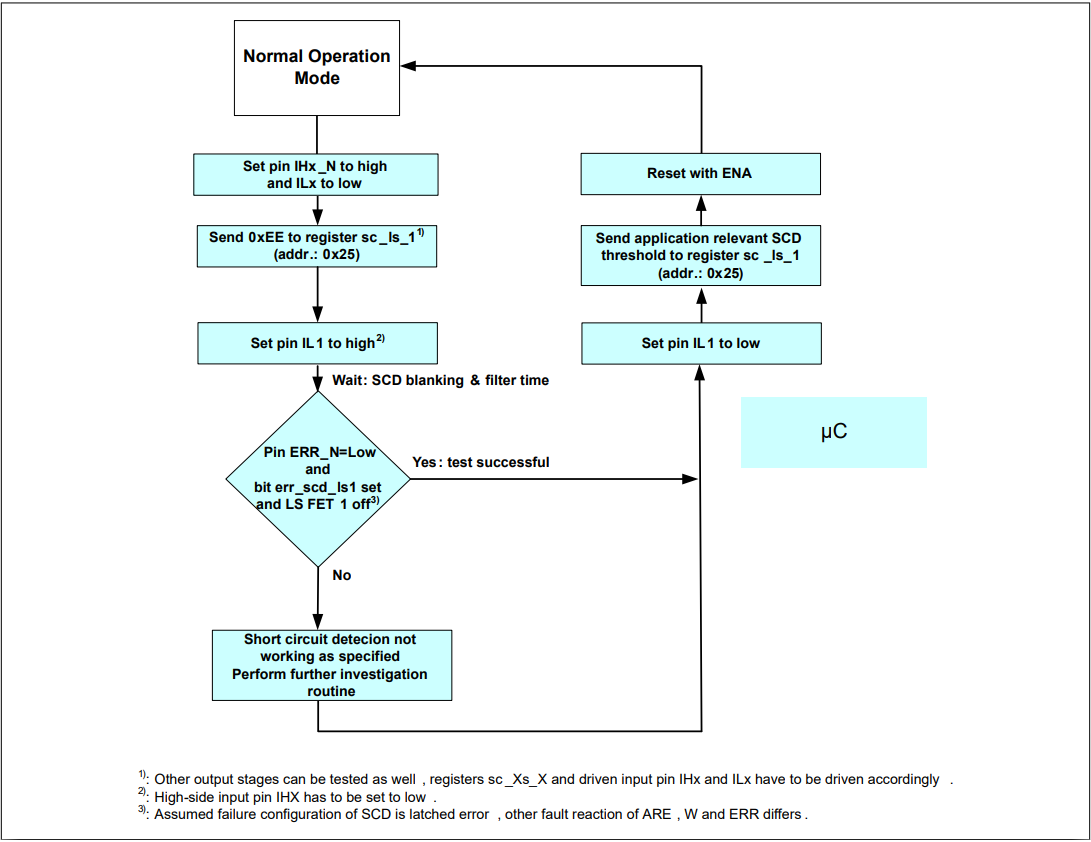

1.1.3 Normal 模式下的短路检测

2. 短路高边自检

我们以短路高边自检为例,对自检进行简单的总结。

2.1 高边自检相关寄存器和引脚

根据流程图,与判断自检是否通过相关的寄存器有dsm_hsx和Err_scd,相关的引脚为ERR_N

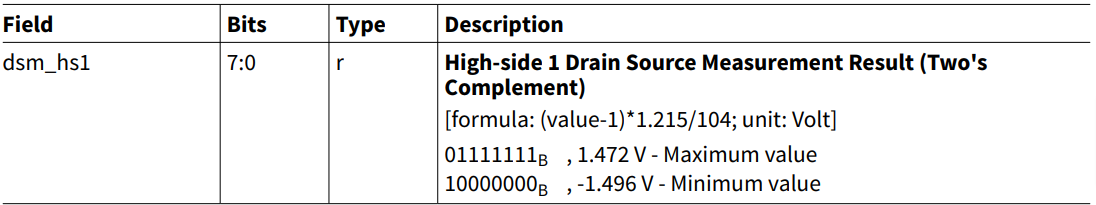

2.1.1 dsm_hsx

dsm_hsx寄存器的类型为r,只读

2.1.2 Err_scd

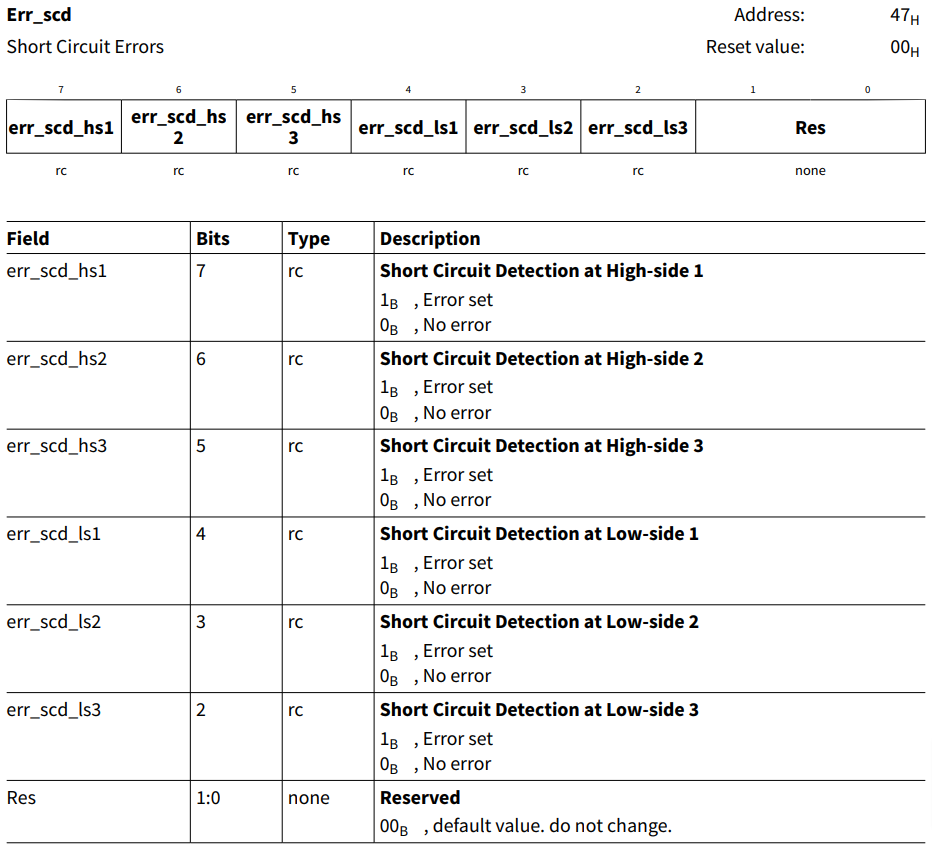

可以看出,Err_scd寄存器的类型为rc,即clear-on-read,寄存器可读且在读取后,寄存器的值会被清除。

2.1.3 错误引脚 ERR_N

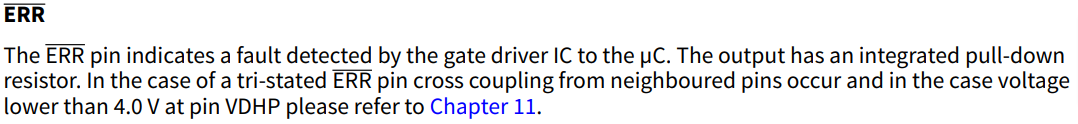

发生故障后,ERR_N为低电平

门驱动IC通过ERR引脚向微控制器(µC)指示检测到的故障。该输出端集成了下拉电阻。当ERR引脚处于高阻态时,相邻引脚会发生交叉耦合。

2.2 与短路自检相关的参数

对短路检测会产生影响甚至直接决定检测通过与否的参数有如下:

- dead time:死区时间

- blanking time:消隐时间

- filter time:滤波时间

2.2.1 消隐时间和滤波时间

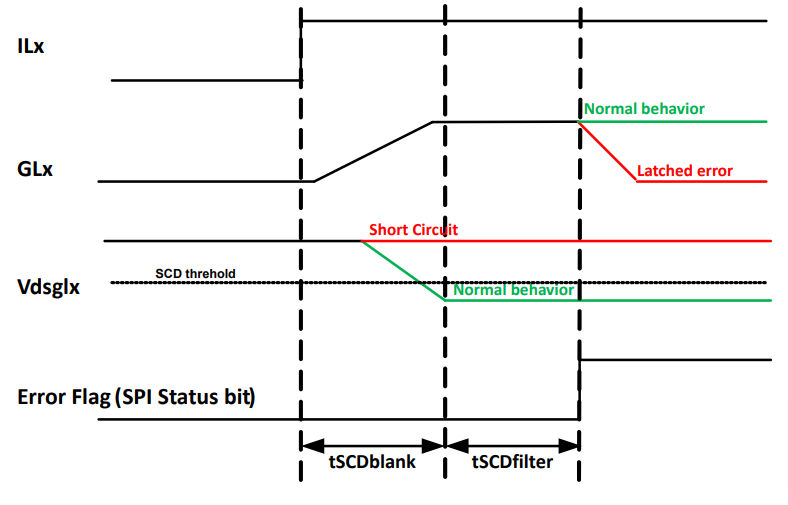

驱动芯片对其控制的外部场效应晶体管(FET)实施短路监控。短路检测(SCD)功能通过检测漏源极电压实现,具体为采集 VDHx 与 VDHP、SHx 之间及 SHx 与 SLx 之间的电压差,并与编程设定电压阈值进行比对。短路检测支持宽范围配置,阈值电平、滤波时间、消隐时间及故障响应行为均可灵活调整,另可额外配置两种故障响应行为,具体详见表 26。

若外部 FET 的占空比区间小于短路检测滤波时间(filter time)与消隐时间(blanking time)之和,短路故障将无法被检测;仅当高边缓冲电容未检测到欠压时,短路检测功能才正常工作。故障寄存器 Err_scd 的第 7 位至第 2 位,用于指示外部 FET 发生短路故障。

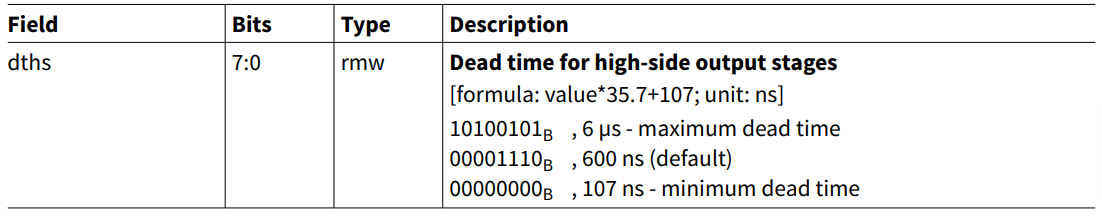

2.2.2 死区时间

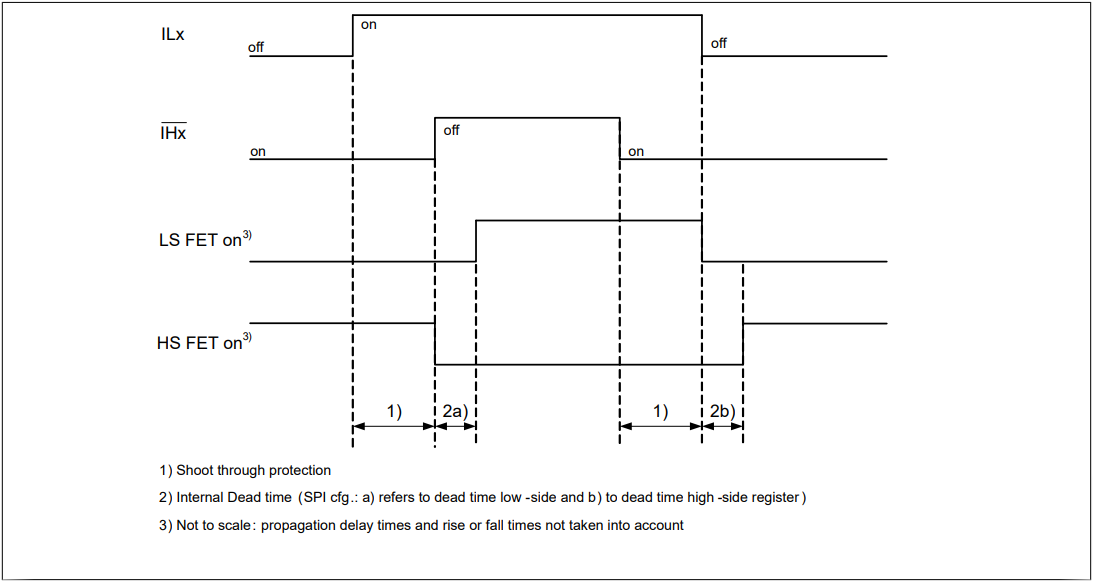

死区时间保护可提供额外的桥臂直通保护功能。死区时间定义为半桥中一路 MOSFET 关断至互补路 MOSFET 开通的时间间隔。TLE9180D-31QK 的死区时间支持可编程配置,可独立设置两组死区时间,分别对应两种开关切换场景:高边关断→低边开通、低边关断→高边开通。其中高边关断→低边开通的死区时间配置请参考 Dt_ls 寄存器,低边关断→高边开通请参考 Dt_hs 寄存器。该设计可避免因外部 FET 传播延迟过长或开关时间过长导致的桥臂短路故障,且无论编程值如何,均能保证最小死区时间。

芯片内置监控功能,用于检测微控制器输出模式是否违反桥臂直通限制及设定的死区时间;若违规,输入模式错误位会被置位,同时指示受影响的输出级。故障响应行为可在配置阶段通过 SPI 灵活调整。若将高低边输入引脚短接,仅用 3 路输出端口驱动所有 FET,建议禁用该监控功能。

Shoot Through Protection and Dead Time Generation in Normal Operation Mode

IHx_N 与 ILx 引脚输入开通脉冲宽度若小于 50 ns,可能导致外部场效应晶体管(FET)开通时间延长,最长可达 1000 ns。CB 引脚存在短时电压毛刺现象。

若采用 6 路微控制器输出端口驱动 6 路 FET,且死区时间由微控制器生成,需避免 IHx_N与 ILx 引脚输入脉冲宽度小于输入脉冲最小宽度tPulse_in;

若采用 3 路微控制器输出端口驱动 6 路 FET,且启用 TLE9180D-31QK 芯片内置死区时间功能,则需避免 IHx_N 与 ILx 引脚输入脉冲宽度小于(芯片内置死区时间 + 输入脉冲最小宽度 t P u l s e i n t_{Pulse_in} tPulsein)。

3. 易错点和注意点

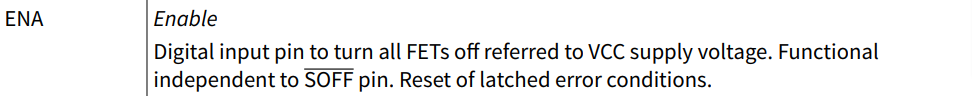

3.1 ENA复位

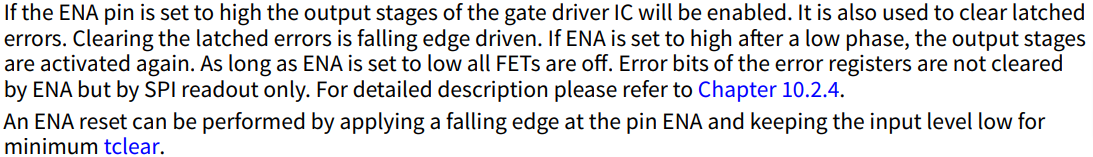

ENA 引脚 当 ENA 引脚置高时,栅极驱动芯片的输出级将被使能;该引脚同时用于清除锁存故障,故障清除为下降沿触发。ENA 引脚经低电平阶段后置高时,输出级将重新激活;ENA 引脚保持低电平时,所有场效应晶体管(FET)均处于关断状态。故障寄存器的故障位不可通过 ENA 引脚清除,仅能通过 SPI 读取操作清除。ENA 复位操作方法:在 ENA 引脚施加下降沿信号,并将输入电平保持低电平至少 tclear 时长。

- 易错点:

- ENA复位后,芯片不能主动清除故障寄存器中的故障位。从2.1.1章节可知,Err_scd寄存器的类型为rc,ENA复位后需要进行一次读取操作,才能清除故障位。

- ENA复位只能清除故障故障寄存器中的故障位,不能对其他寄存器进行复位。对于类型为r(只读)的寄存器,只能通过硬复位或者INH_N引脚复位的方式进行复位。

3.2 自检模式

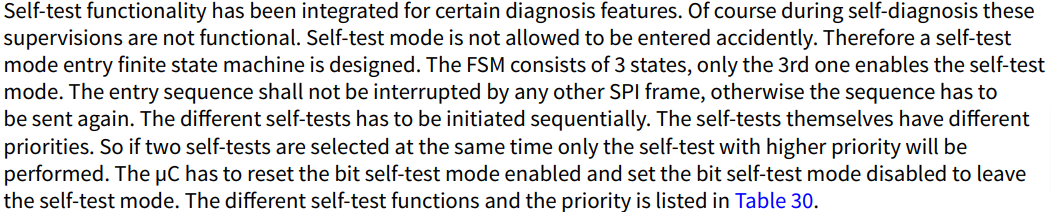

部分诊断功能已集成自检功能。需注意,自检过程中相关监控功能不生效。自检模式禁止误进入,因此专门设计了自检模式进入有限状态机(FSM)。该状态机包含 3 个状态,仅第 3 状态可启用自检模式。模式进入序列不得被任何其他 SPI 帧中断,否则需重新发送该序列。各类自检需按顺序启动,且自身具备不同优先级 ------ 若同时选中两项自检,仅执行优先级更高的那一项。微控制器需复位 "自检模式使能" 位并置位 "自检模式禁用" 位,方可退出自检模式。

- 易错点:

- 自检过程中监控功能不生效。

- 进行短路自检前,应确保进入自检模式,并在自检结束后,退出自检模式。

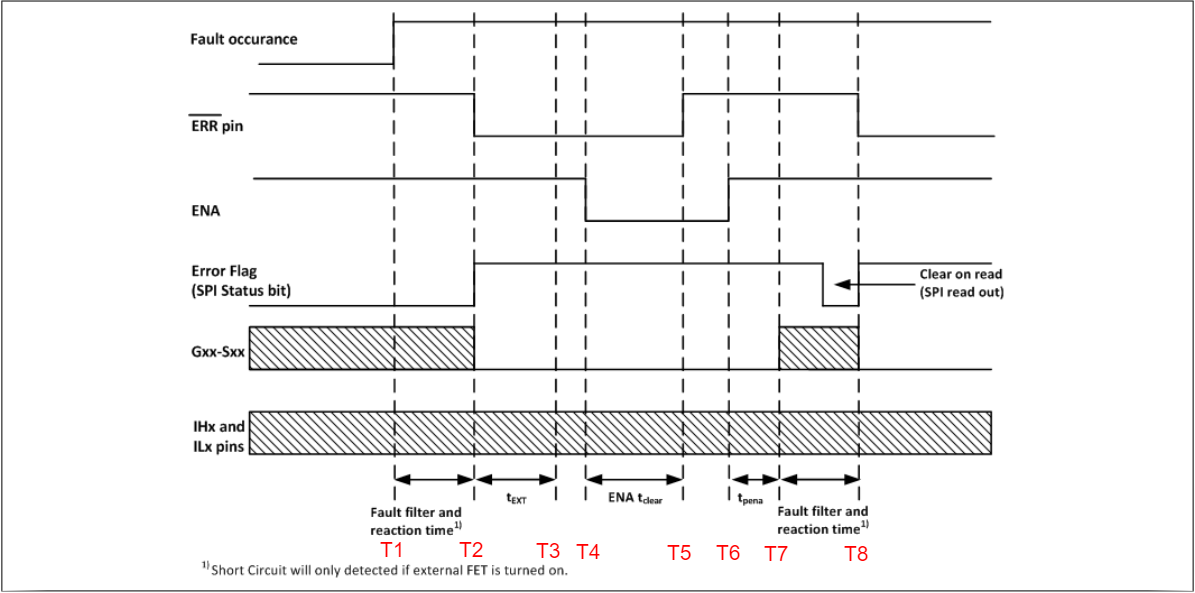

3.3 短路诊断时序图分析

用于短路诊断的锁存错误时序图------永久性故障发生

名词解释

t e x t t_{ext} text:External time fault signaling at pin ERR_N

t c l e a r t_{clear} tclear:ENA low time threshold for clearing latched Errors

t p e n a t_{pena} tpena:ENA propagation time(for enable or disable the output stages)

时序分析

T1: 短路错误发生点

T2: 芯片检测到短路错误后,拉低管脚ERR_N,并对相关寄存器进行置位,Gxx-Sxx停止输出

T3: MCU检测到短路错误,并进行处理

T4: MCU处理后,拉低ENA,进行复位处理

T5: 达到 t c l e a r t_{clear} tclear阈值,ERR_N拉高

T6: 完成ENA复位,ENA拉高

T7: Gxx-Sxx恢复输出

T8: 故障为为永久性,在Gxx-Sxx恢复输出后,故障依然会被检测出,ERR_N引脚拉低,Error Flag恢复置位,Gxx-Sxx停止输出

3.4 复位方式

-

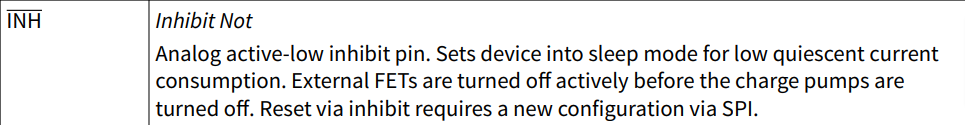

INH_N复位

模拟低有效禁止引脚,用于将器件置于休眠模式以降低静态电流消耗。电荷泵关闭前,外部场效应晶体管会被主动关断。通过禁止引脚复位后,需重新通过 SPI 配置器件。

-

ENA复位

数字输入引脚,用于关断所有场效应晶体管,电平参考电源电压 VCC;功能独立于 SOFF_N 引脚,兼具锁存故障状态复位功能。

ENA 引脚 当 ENA 引脚置高时,栅极驱动芯片的输出级将被使能;该引脚同时用于清除锁存故障,故障清除为下降沿触发。ENA 引脚经低电平阶段后置高时,输出级将重新激活;ENA 引脚保持低电平时,所有场效应晶体管(FET)均处于关断状态。故障寄存器的故障位不可通过 ENA 引脚清除,仅能通过 SPI 读取操作清除。ENA 复位操作方法:在 ENA 引脚施加下降沿信号,并将输入电平保持低电平至少 tclear 时长。

4. 实操中的误区

-

误区一:为了减少误报,短路自检不成功就多做几次,确保在硬件系统正常的情况下不会出现误报。

解释: 以短路高边自检为例,自检模式下,判断自检通过与否的条件有三个:1. dsm_hsx的值;2. Err_scd寄存器. 3. ERR_N引脚。由文档可知,在自检模式下,dsm_hsx只会被写为0x7F或者保持不变两种情况。若出现以下情况

- 第1次自检:hs1超过阈值,hs2,hs3未过阈值,则dsm_hs1被写入0x7F,dsm_hs2/3保持不变;

- 第2次自检:hs2超过阈值,hs1,hs3未过阈值,则dsm_hs2被写入0x7F,dsm_hs1/3保持不变,dsm_hs1的值为0x7F;

- 第3次自检:hs3超过阈值,hs1,hs2未过阈值,则dsm_hs3被写入0x7F,dsm_hs1/2保持不变,dsm_hs1/2的值均为0x7F;

- 第4次自检:hs1/2/3均未过阈值,dsm_hs1/2/3保持不变,dsm_hs1/2/3的值均为0x7F;此次自检可能通过。

当然,上述情况出现的可能性极低。

-

误区二:既然进入自检模式后需要先拉低/拉高电平,像是要造一个边沿,做边沿触发,那在进自检模式前先拉一个相反的电平。

短路检测并非边沿触发,只需要芯片检测到外部FET的电压。

-

误区三:要做全部的自检

TLE9180有3相低边和3相高边,供6相输出,如果只使用了高边/低边3相,那只对高边/低边3相做短路检测即可。