一、计算机系统概论

1.1 计算机系统的本质

计算机系统是一个由硬件 和软件 组成的复杂系统,其核心功能是执行程序 和处理数据。

-

硬件:物理设备的总称,是软件运行的物理基础。包括CPU、内存、主板、I/O设备等。

-

软件:程序及其相关文档的集合,是指挥硬件工作的指令序列。包括系统软件(如操作系统、编译器)和应用软件。

1.2 冯·诺依曼体系结构

现代计算机的理论基础,其核心思想是存储程序控制,主要由五大部件构成:

-

运算器 :执行算术运算和逻辑运算的核心部件。核心是ALU。

-

控制器 :计算机的指挥中心,负责从内存中按顺序取出指令、译码,并产生控制信号以驱动其他部件协调工作。运算器+控制器 = 中央处理器。

-

存储器 :存放程序和数据。分为主存储器 (内存,直接与CPU交互)和辅助存储器(外存,如硬盘,用于长期存储)。

-

输入设备:将外部信息转换为计算机内部可处理的数据形式(如键盘、鼠标、扫描仪)。

-

输出设备:将计算机的处理结果转换为人类或其他设备可识别的形式(如显示器、打印机、音响)。

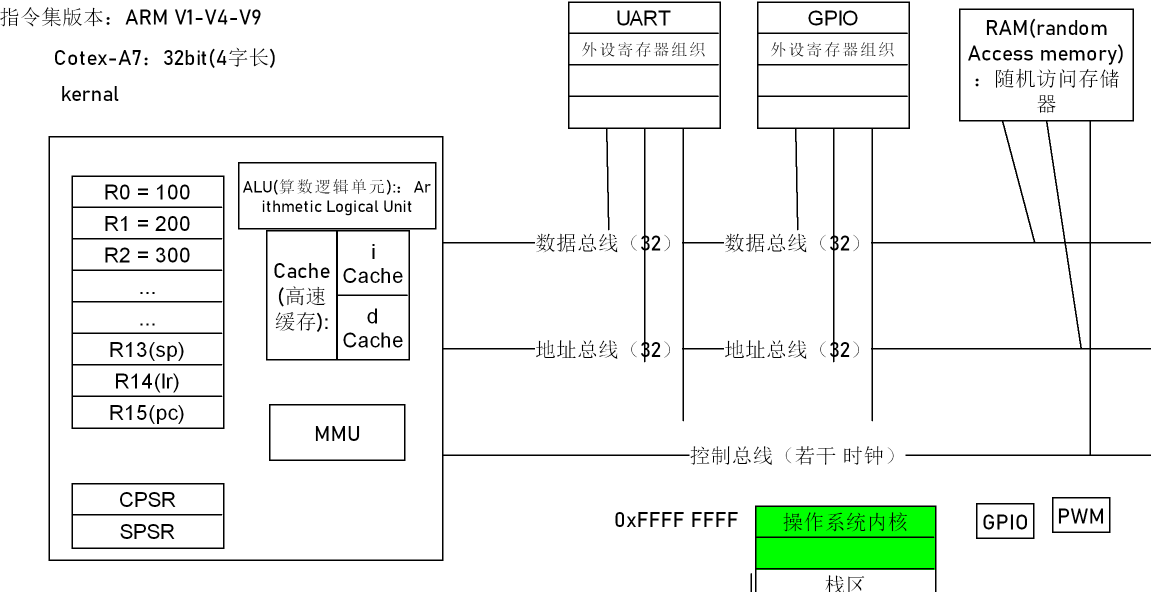

1.3 总线结构

连接系统各部件的公共通信通道。

-

数据总线:双向传输数据,其宽度(位数)决定了一次可传输的数据量。

-

地址总线:单向(CPU发出),用于指定内存或I/O端口的地址,其宽度决定了系统的寻址空间。

-

控制总线:传输控制信号,如读/写、中断请求、时钟等。

二、中央处理器

2.1 CPU的功能与组成

CPU是计算机的"大脑",其根本任务是取指、译码、执行。

-

ALU:执行所有数学运算和逻辑运算。

-

寄存器组:CPU内部的高速存储单元,用于暂存指令、数据和地址。访问速度极快。

-

通用寄存器:存放操作数和中间结果。

-

专用寄存器:

-

程序计数器 :存放下一条要执行的指令的内存地址。

-

指令寄存器:存放当前正在执行的指令。

-

堆栈指针:指向当前堆栈顶部的地址。

-

状态寄存器:存放上一条指令执行后的状态信息(如是否溢出、是否为负等)。

-

-

-

控制单元:产生控制序列,指挥ALU、寄存器和总线协同工作。

-

内部数据通路:连接CPU内部各组件的高速通道。

2.2 指令集架构

是软件和硬件之间的接口,定义了CPU可执行的基本命令集合。

-

CISC:

-

特点:指令系统复杂,指令长度可变,一条指令可完成复杂操作。

-

优点:代码密度高,简化编译器设计。

-

缺点:控制器硬件复杂,指令执行周期不一致。代表:x86。

-

-

RISC:

-

特点:指令系统精简,指令长度固定,采用加载/存储结构,指令大部分在一个时钟周期内完成。

-

优点 :硬件设计简单,有利于提高主频和并行执行。ARM架构是RISC的典范。

-

缺点:代码密度相对较低。

-

2.3 位宽

指CPU一次能处理的二进制数据的位数(如32位、64位)。它直接影响:

-

计算能力:64位CPU一次可处理64位数据,性能更强。

-

寻址空间:32位CPU最大寻址4GB,而64位CPU寻址空间极大。

三、存储器系统层次结构

为了解决速度、容量和成本的矛盾,计算机采用多级存储体系。

| 存储层次 | 特点 | 作用 |

|---|---|---|

| 寄存器 | 速度最快,容量最小,成本最高,在CPU内部。 | 存放当前正在执行的指令和数据。 |

| 高速缓存 | 速度很快,容量小,成本高,分L1, L2, L3。 | 存放最可能被CPU使用的程序和数据副本,解决CPU与主存的速度差异。 |

| 主存储器 | 速度中等,容量较大,成本中等。 | 存放当前正在运行的活跃程序和数据。CPU可直接访问。 |

| 辅助存储器 | 速度慢,容量大,成本低。 | 用于长期、海量存储。CPU不能直接访问,需调入主存。 |

工作原理 :基于程序访问的局部性原理(时间局部性和空间局部性),将活跃数据从低速存储器预取到高速存储器。

四、ARM体系结构精讲

4.1 ARM公司商业模式

ARM采用IP授权模式,自身不生产芯片,而是设计CPU核心架构,将设计授权给其他公司使用。

4.2 ARM数据类型与指令集

-

基本数据类型:

-

字节:8位。

-

半字:16位。

-

字:32位。

-

-

指令集状态:

-

ARM状态:执行32位ARM指令,性能高。

-

Thumb状态:执行16位Thumb指令,代码密度高。

-

Thumb-2状态:支持16位和32位指令混合,兼顾性能和代码密度。

-

4.3 ARM处理器工作模式

ARM有7种工作模式,以适应不同任务和异常。

| 处理器模式 | 描述 | 用途 |

|---|---|---|

| 用户模式 | 非特权模式,资源访问受限。 | 普通应用程序的执行。 |

| 系统模式 | 特权模式,使用与用户模式相同的寄存器。 | 运行特权操作系统任务。 |

| 管理模式 | 复位或执行SWI指令时进入。 | 操作系统的保护模式,用于系统调用。 |

| 中断模式 | 发生普通IRQ中断时进入。 | 通用中断处理。 |

| 快速中断模式 | 发生FIQ中断时进入,有独立的影子寄存器。 | 处理高速、低延迟的中断。 |

| 中止模式 | 数据或指令预取中止时进入。 | 处理内存访问失败错误。 |

| 未定义模式 | 执行未定义指令时进入。 | 处理未支持的指令或用于软件仿真。 |

4.4 ARM寄存器组织详述

ARM处理器共有37个32位寄存器 ,但在任何时刻,只有16个通用寄存器 和1-2个状态寄存器对程序员可见,这取决于当前处理器模式。

-

通用寄存器:

-

R0-R12:真正通用的寄存器,用于数据操作。

-

R13 :通常用作堆栈指针 。每种异常模式都有自己独立的R13,用于管理各自的堆栈。

-

R14 :链接寄存器 ,用于在调用子程序时保存返回地址。异常模式有自己的R14,用于保存异常的返回地址。

-

R15 :程序计数器。读操作返回当前指令地址+8(ARM状态)或+4(Thumb状态)。

-

-

程序状态寄存器:

-

当前程序状态寄存器:

-

条件码标志:

-

N:运算结果为负时置1。

-

Z:运算结果为零时置1。

-

C:运算产生进位或借位时置1。

-

V:运算产生溢出时置1。

-

-

控制位:

-

中断禁止位:I=1禁止IRQ,F=1禁止FIQ。

-

T位:T=0为ARM状态,T=1为Thumb状态。

-

模式位:决定当前处理器模式。

-

-

-

保存的程序状态寄存器:当异常发生时,硬件自动将CPSR的副本存入当前异常模式的SPSR中。异常返回时,用SPSR来恢复CPSR。

-

4.5 ARM异常处理机制详解

-

异常向量表:一块固定的内存区域,存放着各种异常处理程序的入口地址。

-

异常处理流程:

-

保存现场 :将PC 值保存到当前异常模式的LR 中,将CPSR 保存到当前异常模式的SPSR中。

-

模式切换 :设置CPSR中的模式位,切换到对应的异常模式;设置中断禁止位以防止嵌套中断。

-

跳转 :将PC 设置为对应的异常向量地址,跳转到异常处理程序。

-

-

异常返回 :异常处理程序执行完毕后,需要手动操作,从SPSR 恢复CPSR ,并从LR 恢复PC。

五、软件编译与开发流程

5.1 从高级语言到机器码

-

预处理:处理宏定义、文件包含、条件编译等。

-

编译:将高级语言翻译成汇编语言。

-

汇编:将汇编语言翻译成机器码,生成目标文件。

-

链接:将多个目标文件和库文件链接在一起,解析符号引用,生成最终的可执行文件。

5.2 集成开发环境

用于ARM开发的工具链通常包括交叉编译器 、调试器 和仿真器。

六、数字电路与半导体基础

6.1 逻辑电平与数字表示

-

TTL电平:

-

输出:高电平 ≥ 2.4V,低电平 ≤ 0.4V。

-

输入:识别为高电平 ≥ 2.0V,识别为低电平 ≤ 0.8V。

-

-

CMOS电平:

-

高电平 ≈ 电源电压,低电平 ≈ 0V。

-

噪声容限比TTL大。

-

6.2 基本逻辑门

-

与门:所有输入为1,输出才为1。

-

或门:任一输入为1,输出就为1。

-

非门:输出是输入的反相。

-

与非门、或非门、异或门:由基本门组合而成。

6.3 关键半导体器件

-

二极管:具有单向导电性(正向导通,反向截止)。

-

三极管 :电流控制型器件,工作在截止区 、放大区 和饱和区,可用于放大和开关。

-

MOS管:电压控制型器件,是构成CMOS集成电路的基础。分为NMOS和PMOS。

七、硬件实践与系统集成

7.1 ARM最小系统

指使一个ARM处理器能够正常工作所需的最少组件构成的系统。

-

电源电路:提供稳定、干净的电源。

-

时钟电路:提供系统工作的基准时钟。

-

复位电路:提供上电复位和手动复位信号。

-

存储器:Flash和SDRAM,用于存储程序和数据。

-

调试接口:用于程序下载和调试。

7.2 通信接口概念

-

单工、半双工、全双工:定义数据传输方向。

-

串行通信与并行通信:定义数据传输方式。

-

同步通信与异步通信:定义收发双方的时钟同步方式。

7.3 常见封装

-

BGA:球栅阵列封装,引脚在芯片底部,以焊球形式分布,集成度高。

-

COB:芯片直接贴在PCB上,用黑胶封装,成本低。